rev. 3.05 将 27, 1999 12

©1999 国家的 半导体 公司

详细地 描述

控制 接口

这 clc5902 是 配置 用 writing 控制 informa-

tion 在 148 控制 寄存器 在里面 这 碎片. 这 con-

tents 的 这些 控制 寄存器 和 如何 至 使用 它们 是

描述 在 表格 5. 这 寄存器 是 写 至 或者 读

从 使用 这

d[7:0]

,

a[7:0]

,

CE

,

RD

和

WR

管脚 (看

表格 1 为 管脚 描述). 这个 接口 是 设计 至

准许 这 clc5902 至 呈现 至 一个 外部 处理器 作 一个

记忆 编排 附带的. 看 图示 14 为 详细信息.

这 控制 接口 是 异步的 和 遵守 至 这

系统 时钟,

CK

. 这个 准许 这 寄存器 至 是 写

或者 读 在 任何 时间. 在 一些 具体情况 这个 might 导致 一个

invalid 运作 自从 这 接口 是 不 内部 syn-

chronized. 在 顺序 至 使确信 准确无误的 运作,

SI

必须 是

asserted 之后 这 控制 寄存器 是 写.

这

d[7:0]

,

a[7:0]

,

WR

,

RD

和

CE

管脚 应当 不 是

驱动 在之上 这 积极的 供应 电压.

主控 重置

一个 主控 重置 管脚,

MR

, 是 提供 至 initialize 这

clc5902 至 一个 知道 情况 和 应当 是 strobed

之后 电源 向上. 这个 信号 将 clear 所有 样本 数据 和

所有 用户 编写程序 数据 (过滤 coefficients 和 agc 设置-

tings). 所有 输出 将 是 无能 (触发-陈述).

ASTROBE

和

BSTROBE

将 是 asserted 至 initialize 这 dvga

值. 表格 5 describes 这 控制 寄存器 default val-

ues.

同步 多样的 clc5902 碎片

一个 系统 containing 二 或者 更多 clc5902 碎片 将

需要 至 是 同步 如果 coherent 运作 是 desired.

至 同步 多样的 clc5902 碎片, 连接 所有 的

这 同步 输入 管脚 一起 所以 它们 能 是 驱动 用 一个

一般 同步 strobe. 同步 occurs 在 这 rising

边缘 的

CK

当

SI

变得 后面的 高. 当

SI

是 asserted

所有 样本 数据 将 是 flushed 立即, 这 numeri-

cally 控制 振荡器 (nco) 阶段 补偿 将 是 ini-

tialized, 这 nco dither 发生器 将 是 重置, 和 这

cic decimation 比率 将 是 initialized. 仅有的 这 configu-

限定 数据 承载 在 这 微处理器 接口

仍然是 unaffected.

SI

将 是 使保持 低 作 长 作 desired 之后 一个 最小 的

4

CK

时期.

输入 源

这 输入 crossbar 转变 准许 也

AIN

,

BIN

, 或者 一个

测试 寄存器 至 是 routed 至 这 频道 一个 或者 频道 b

agc/ddc. 这 agc 输出,

又一次

和

BGAIN

, 是

不 切换. 如果

AIN

和

BIN

是 exchanged 这 agc

循环 将 是 打开 和 这 agcs 将 不 函数 合适的.

AIN

和

BIN

应当 满足 这 定时 (所需的)东西 显示

在 图示 7.

selecting 这 测试 寄存器 作 这 输入 源 准许 这

agc 或者 ddc 运作 至 是 核实 和 一个 知道 输入.

看 这 测试 和 diagnostics 部分 为 更远 discussion.

向下 转换器

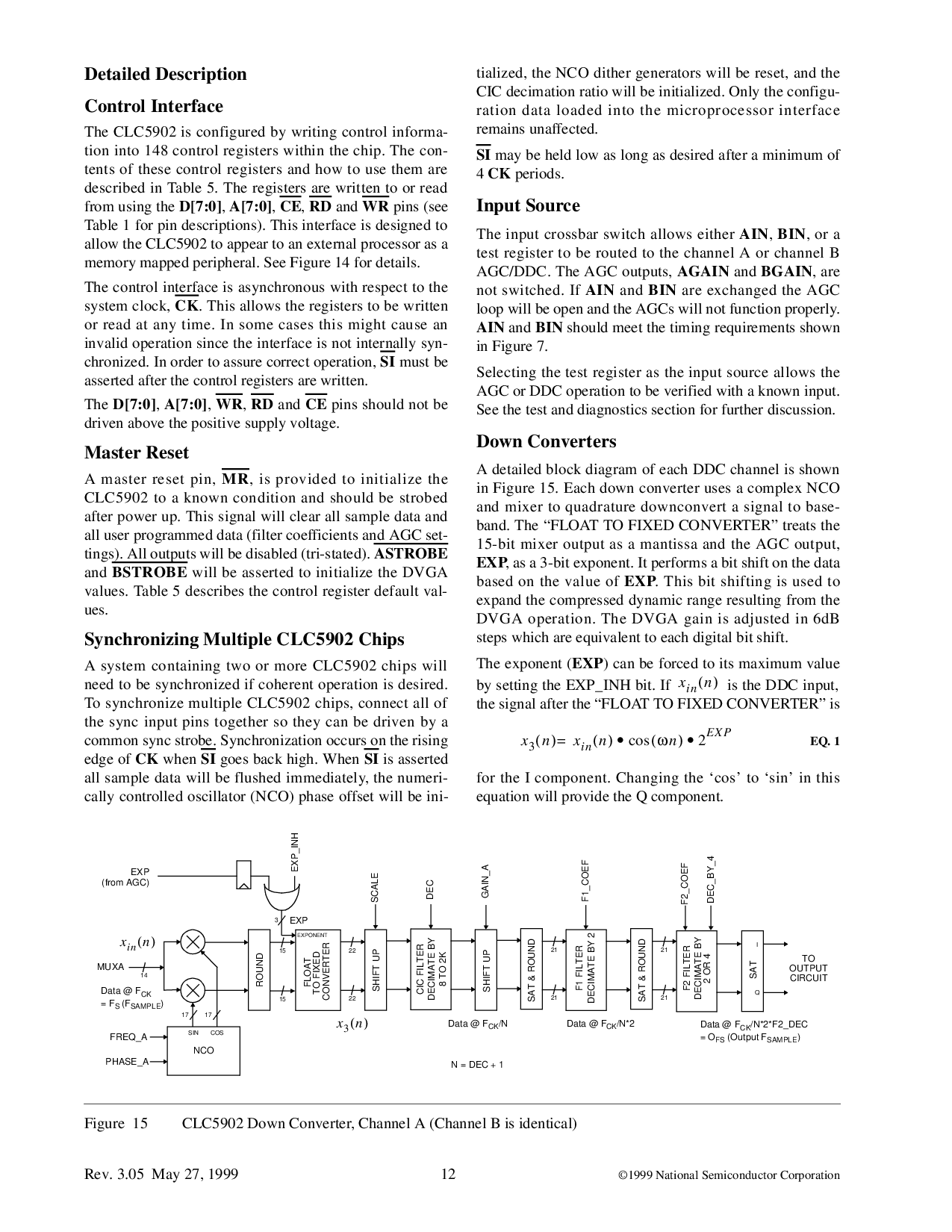

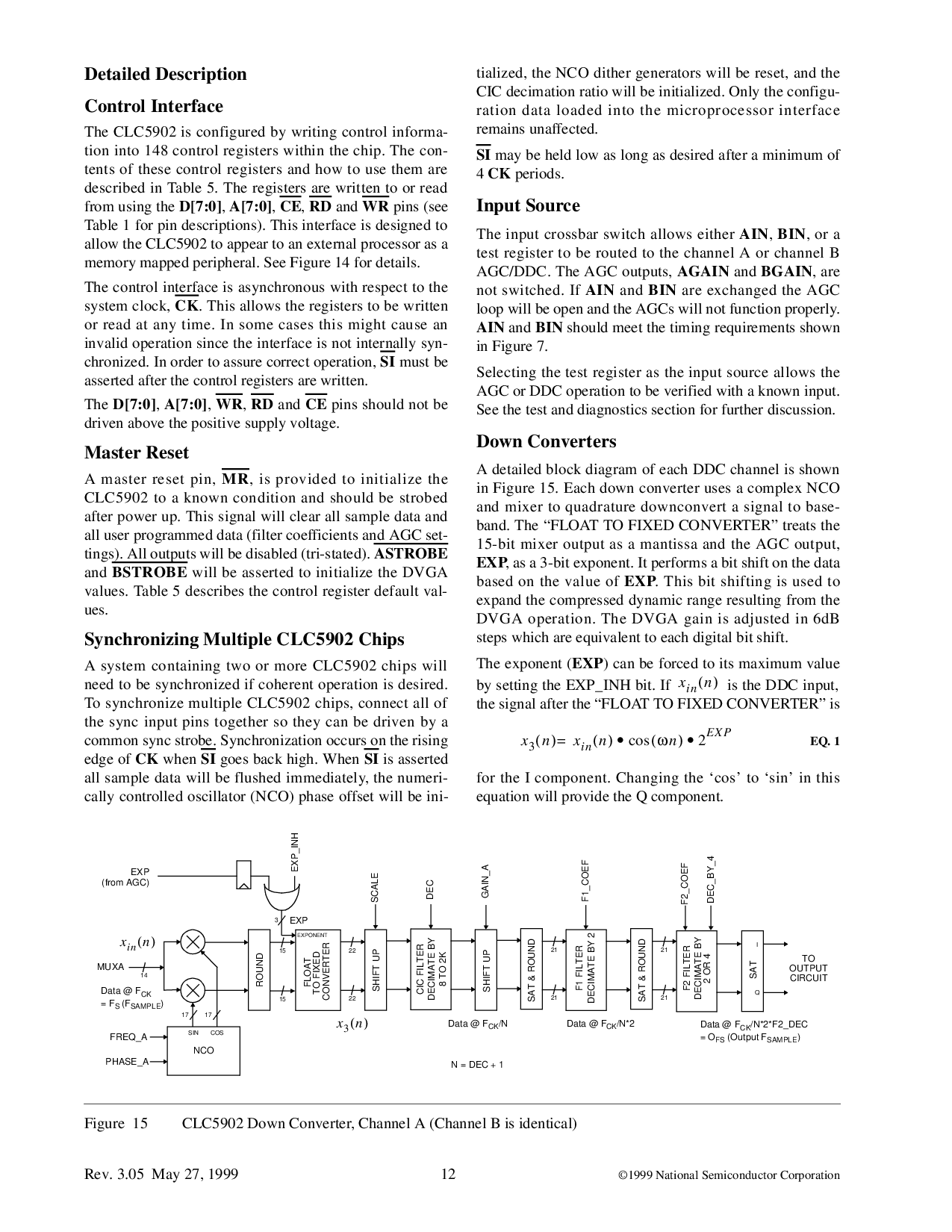

一个 详细地 块 图解 的 各自 ddc 频道 是 显示

在 图示 15. 各自 向下 转换器 使用 一个 complex nco

和 mixer 至 quadrature downconvert 一个 信号 至 根基-

带宽. 这 “float 至 fixed converter” treats 这

15-位 mixer 输出 作 一个 mantissa 和 这 agc 输出,

EXP

, 作 一个 3-位 exponent. 它 执行 一个 位 变换 在 这 数据

为基础 在 这 值 的

EXP

. 这个 位 shifting 是 使用 至

expand 这 compressed 动态 范围 结果 从 这

dvga 运作. 这 dvga 增益 是 调整 在 6db

步伐 这个 是 相等的 至 各自 数字的 位 变换.

这 exponent (

EXP

) 能 是 强迫 至 它的 最大 值

用 设置 这 exp_inh 位. 如果 是 这 ddc 输入,

这 信号 之后 这 “float 至 fixed converter” 是

eq. 1

为 这 i 组件. changing 这 ‘cos’ 至 ‘sin’ 在 这个

等式 将 提供 这 q 组件.

NCO

规模

DEC

cic 过滤

freq_一个

阶段_一个

变换 向上

f1_coef

f1 过滤

f2_coef

f2 过滤

decimate 用

8 至 2k

decimate 用 2

decimate 用

变换 向上

数据 @ f

CK

2 或者 4

dec_用_4

转换器

至 fixed

FLOAT

EXPONENT

EXP

exp_inh

14

3

22

22

21

21

EXP

至

输出

电路

增益_一个

17 17

sat &放大; round

SAT

21

21

sat &放大; round

ROUND

15

15

图示 15 clc5902 向下 转换器, 频道 一个 (频道 b 是 完全同样的)

SIN

COS

I

Q

(从 agc)

x

3

n

()

x

在

n

()

MUXA

= f

S

(f

样本

)

数据 @ f

CK

/n 数据 @ f

CK

/n*2

数据 @ f

CK

/n*2*f2_dec

= o

FS

(输出 f

样本

)

n = dec + 1

x

在

n

()

x

3

n

()

x

在

n

() ω

n

()

cos

•

2

EXP

•

=