©1999 国家的 半导体 公司

7 rev. 3.05 将 27, 1999

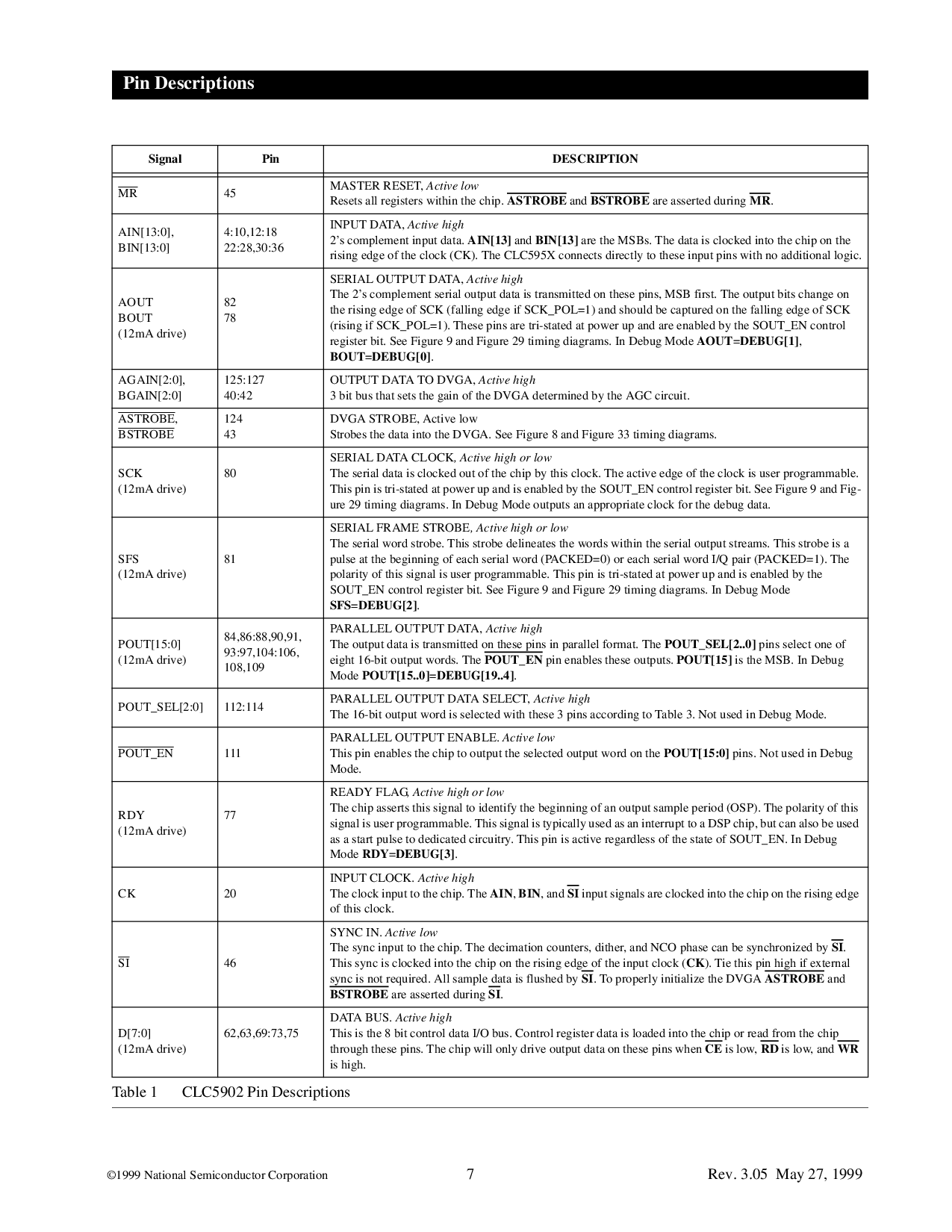

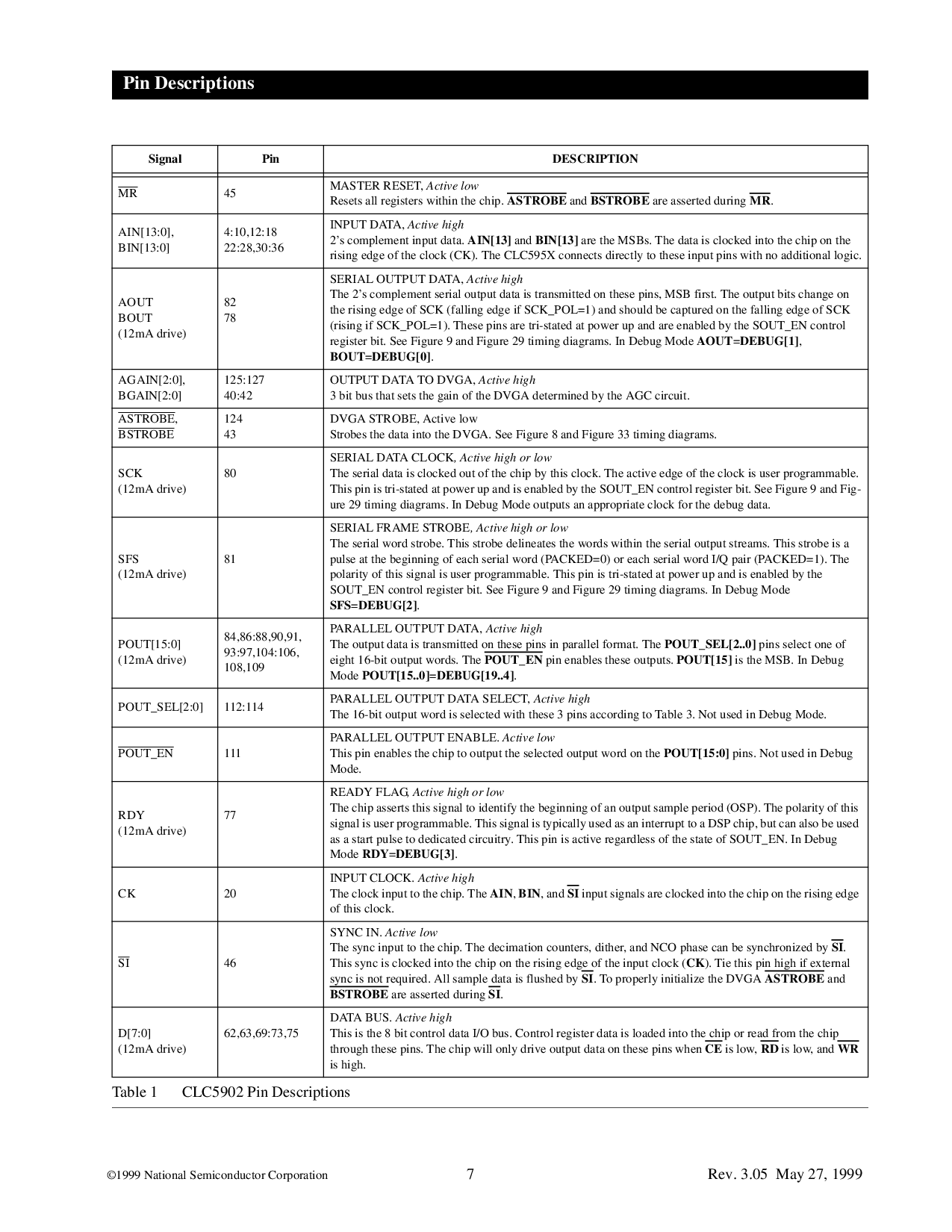

管脚 描述

信号 管脚 描述

MR

45

主控 重置,

起作用的 低

resets 所有 寄存器 在里面 这 碎片.

ASTROBE

和

BSTROBE

是 asserted 在

MR

.

ain[13:0],

bin[13:0]

4:10,12:18

22:28,30:36

输入 数据,

起作用的 高

2’s complement 输入 数据.

AIN[13]

和

BIN[13]

是 这 msbs. 这 数据 是 clocked 在 这 碎片 在 这

rising 边缘 的 这 时钟 (ck). 这 clc595x connects 直接地 至 这些 输入 管脚 和 非 额外的 逻辑.

AOUT

BOUT

(12ma 驱动)

82

78

串行 输出 数据,

起作用的 高

这 2’s complement 串行 输出 数据 是 transmitted 在 这些 管脚, msb 第一. 这 输出 位 改变 在

这 rising 边缘 的 sck (下落 边缘 如果 sck_pol=1) 和 应当 是 captured 在 这 下落 边缘 的 sck

(rising 如果 sck_pol=1). 这些 管脚 是 触发-陈述 在 电源 向上 和 是 使能 用 这 sout_en 控制

寄存器 位. 看 图示 9 和 图示 29 定时 图解. 在 debug 模式

AOUT

=

DEBUG[1]

,

BOUT

=

DEBUG[0]

.

again[2:0],

bgain[2:0]

125:127

40:42

输出 数据 至 dvga,

起作用的 高

3 位 总线 那 sets 这 增益 的 这 dvga 决定 用 这 agc 电路.

ASTROBE

,

BSTROBE

124

43

dvga strobe, 起作用的 低

strobes 这 数据 在 这 dvga. 看 图示 8 和 图示 33 定时 图解.

SCK

(12ma 驱动)

80

串行 数据 时钟

, 起作用的 高 或者 低

这 串行 数据 是 clocked 输出 的 这 碎片 用 这个 时钟. 这 起作用的 边缘 的 这 时钟 是 用户 可编程序的.

这个 管脚 是 触发-陈述 在 电源 向上 和 是 使能 用 这 sout_en 控制 寄存器 位. 看 图示 9 和 图-

ure 29 定时 图解. 在 debug 模式 输出 一个 适合的 时钟 为 这 debug 数据.

SFS

(12ma 驱动)

81

串行 框架 strobe

, 起作用的 高 或者 低

这 串行 文字 strobe. 这个 strobe delineates 这 words 在里面 这 串行 输出 streams. 这个 strobe 是 一个

脉冲波 在 这 beginning 的 各自 串行 文字 (packed=0) 或者 各自 串行 文字 i/q 一双 (packed=1). 这

极性 的 这个 信号 是 用户 可编程序的. 这个 管脚 是 触发-陈述 在 电源 向上 和 是 使能 用 这

sout_en 控制 寄存器 位. 看 图示 9 和 图示 29 定时 图解. 在 debug 模式

SFS

=

DEBUG[2]

.

pout[15:0]

(12ma 驱动)

84,86:88,90,91,

93:97,104:106,

108,109

并行的 输出 数据,

起作用的 高

这 输出 数据 是 transmitted 在 这些 管脚 在 并行的 format. 这

pout_sel[2..0]

管脚 选择 一个 的

第八 16-位 输出 words. 这

pout_en

管脚 使能 这些 输出.

POUT[15]

是 这 msb. 在 debug

模式

pout[15..0]

=

debug[19..4]

.

pout_sel[2:0] 112:114

并行的 输出 数据 选择,

起作用的 高

这 16-位 输出 文字 是 选择 和 这些 3 管脚 符合 至 表格 3. 不 使用 在 debug 模式.

pout_en

111

并行的 输出 使能.

起作用的 低

这个 管脚 使能 这 碎片 至 输出 这 选择 输出 文字 在 这

pout[15:0]

管脚. 不 使用 在 debug

模式.

RDY

(12ma 驱动)

77

准备好 标记

, 起作用的 高 或者 低

这 碎片 asserts 这个 信号 至 identify 这 beginning 的 一个 输出 样本 时期 (osp). 这 极性 的 这个

信号 是 用户 可编程序的. 这个 信号 是 典型地 使用 作 一个 中断 至 一个 dsp 碎片, 但是 能 也 是 使用

作 一个 开始 脉冲波 至 专心致志的 电路系统. 这个 管脚 是 起作用的 regardless 的 这 状态 的 sout_en. 在 debug

模式

RDY

=

DEBUG[3]

.

CK 20

输入 时钟.

起作用的 高

这 时钟 输入 至 这 碎片. 这

AIN

,

BIN

, 和

SI

输入 信号 是 clocked 在 这 碎片 在 这 rising 边缘

的 这个 时钟.

SI

46

同步 在.

起作用的 低

这 同步 输入 至 这 碎片. 这 decimation counters, dither, 和 nco 阶段 能 是 同步 用

SI

.

这个 同步 是 clocked 在 这 碎片 在 这 rising 边缘 的 这 输入 时钟 (

CK

). 系 这个 管脚 高 如果 外部

同步 是 不 必需的. 所有 样本 数据 是 flushed 用

SI

. 至 合适的 initialize 这 dvga

ASTROBE

和

BSTROBE

是 asserted 在

SI

.

d[7:0]

(12ma 驱动)

62,63,69:73,75

数据 总线.

起作用的 高

这个 是 这 8 位 控制 数据 i/o 总线. 控制 寄存器 数据 是 承载 在 这 碎片 或者 读 从 这 碎片

通过 这些 管脚. 这 碎片 将 仅有的 驱动 输出 数据 在 这些 管脚 当

CE

是 低,

RD

是 低, 和

WR

是 高.

表格 1 clc5902 管脚 描述