DS618PP1 7

CS4382A

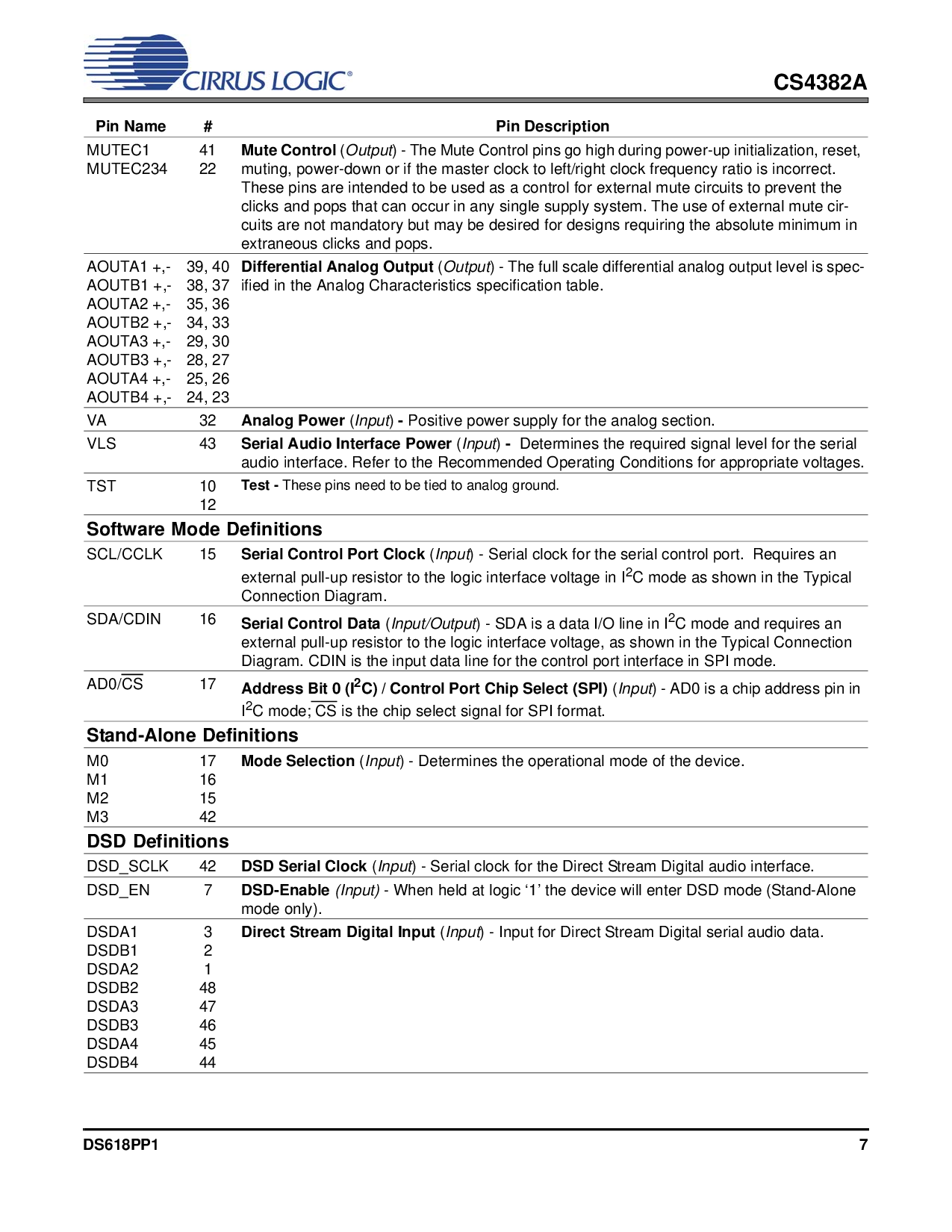

MUTEC1

MUTEC234

41

22

沉默的 控制

(

输出

) - 这 沉默的 控制 管脚 go 高 在 电源-向上 initialization, 重置,

噪声抑制, 电源-向下 或者 如果 这 主控 时钟 至left/正确的 时钟 frequency 比率 是 incorrect.

这些 管脚 是 将 至 是 使用 作 一个 control 为 外部 沉默的 circuits 至 阻止 这

clicks 和 pops 那 能 出现 在 任何 单独的 供应 系统. 这 使用 的 外部 沉默的 cir-

cuits 是 不 mandatory 但是 将 是 desired 为 设计 需要 这 绝对 最小 在

extraneous clicks 和 pops.

aouta1 +,-

aoutb1 +,-

aouta2 +,-

aoutb2 +,-

aouta3 +,-

aoutb3 +,-

aouta4 +,-

aoutb4 +,-

39, 40

38, 37

35, 36

34, 33

29, 30

28, 27

25, 26

24, 23

差别的 相似物 输出

(

输出

) - 这 全部 规模 差别的 相似物 输出 水平的 是 规格-

ified 在 这 相似物 characteristics 规格 表格.

VA 32

相似物 电源

(

输入

)

-

积极的 电源 供应 为 这 相似物 部分.

VLS 43

串行 音频的 接口 电源

(

输入

)

-

确定 这 必需的 信号 水平的 为 这 串行

音频的 接口. 谈及 至 这 推荐 operating 情况 为 适合的 电压.

TST 10

12

测试 -

这些 管脚 需要 至 是 系 至 相似物 地面.

软件 模式 定义

scl/cclk 15

串行 控制 端口 时钟

(

输入

) - 串行 时钟 为 这 串行 控制 端口. 需要 一个

外部 拉-向上 电阻 至 这 逻辑 接口 电压 在 i

2

c 模式 作 显示 在 这 典型

连接 图解.

sda/cdin 16

串行 控制 数据

(

输入/输出

) - sda 是 一个 数据 i/o 线条 在 i

2

c 模式 和 需要 一个

外部 拉-向上 电阻 至 这 逻辑 接口 电压, 作 显示 在 这 典型 连接

图解. cdin 是 这 输入 数据 线条 为 the 控制 端口 接口 在 spi 模式.

ad0/cs

17

地址 位 0 (i

2

c) / 控制 端口 碎片 选择 (spi)

(

输入

) - ad0 是 一个 碎片 地址 管脚 在

I

2

c 模式; cs是 这 碎片 选择 信号 为 spi format.

保卫-alone 定义

M0

M1

M2

M3

17

16

15

42

模式 选择

(

输入

) - 确定 这 运算的 模式 的 这 设备.

dsd 定义

dsd_sclk 42

dsd 串行

时钟

(

输入

) - 串行 时钟 为 这 直接stream 数字的 音频的 接口.

dsd_en 7

dsd-使能

(输入)

- 当 使保持 在 逻辑 ‘1’ 这 de恶行 将 enter dsd 模式 (保卫-alone

模式 仅有的).

DSDA1

DSDB1

DSDA2

DSDB2

DSDA3

DSDB3

DSDA4

DSDB4

3

2

1

48

47

46

45

44

直接 stream 数字的 输入

(

输入

) - 输入 为 直接 stream 数字的 串行 音频的 数据.

管脚 名字 # 管脚 描述