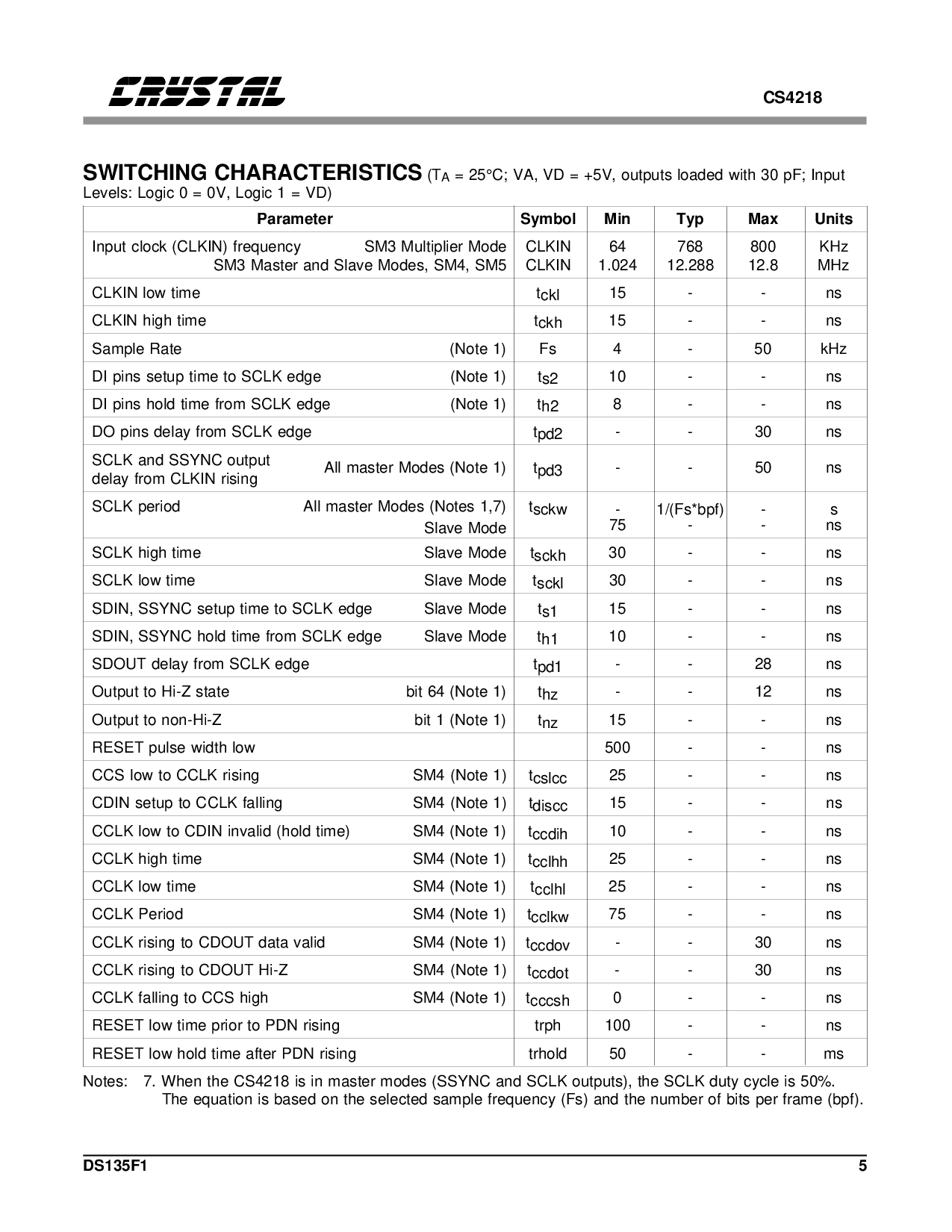

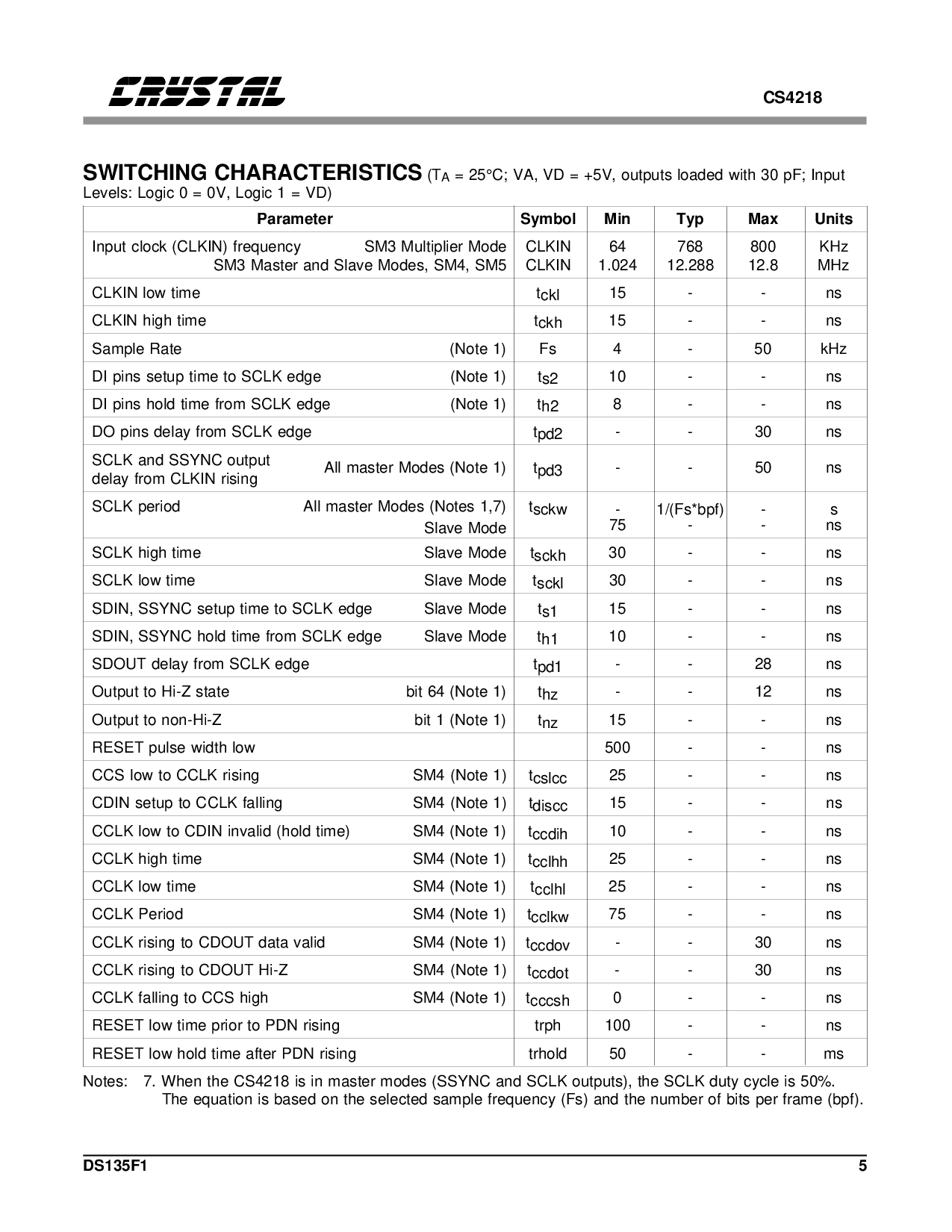

切换 特性

(t

一个

= 25

°

c; va, vd = +5v, 输出 承载 和 30 pf; 输入

水平: 逻辑 0 = 0v, 逻辑 1 = vd)

参数 标识 最小值 典型值 最大值 单位

输入 时钟 (clkin) 频率 sm3 乘法器 模式 CLKIN 64 768 800 KHz

sm3 主控 和 从动装置 模式, sm4, sm5 CLKIN 1.024 12.288 12.8 MHz

clkin 低 时间 t

ckl

15 - - ns

clkin 高 时间 t

ckh

15 - - ns

样本 比率 (便条 1) Fs 4 - 50 kHz

di 管脚 建制 时间 至 sclk 边缘 (便条 1) t

s2

10 - - ns

di 管脚 支撑 时间 从 sclk 边缘 (便条 1) t

h2

8- -ns

做 管脚 延迟 从 sclk 边缘 t

pd2

- - 30 ns

sclk 和 ssync 输出

所有 主控 模式 (便条 1) t

pd3

- - 50 ns

延迟 从 clkin rising

sclk 时期 所有 主控 模式 (注释 1,7) t

sckw - 1/(fs*bpf) - s

从动装置 模式

75 - - ns

sclk 高 时间 从动装置 模式 t

sckh

30 - - ns

sclk 低 时间 从动装置 模式 t

sckl

30 - - ns

sdin, ssync 建制 时间 至 sclk 边缘 从动装置 模式 t

s1

15 - - ns

sdin, ssync 支撑 时间 从 sclk 边缘 从动装置 模式 t

h1

10 - - ns

sdout 延迟 从 sclk 边缘 t

pd1

- - 28 ns

输出 至 hi-z 状态 位 64 (便条 1) t

hz

- - 12 ns

输出 至 非-hi-z 位 1 (便条 1) t

nz

15 - - ns

重置 脉冲波 宽度 低 500 - - ns

ccs 低 至 cclk rising sm4 (便条 1) t

cslcc

25 - - ns

cdin 建制 至 cclk 下落 sm4 (便条 1) t

discc

15 - - ns

cclk 低 至 cdin invalid (支撑 时间) sm4 (便条 1) t

ccdih

10 - - ns

cclk 高 时间 sm4 (便条 1) t

cclhh

25 - - ns

cclk 低 时间 sm4 (便条 1) t

cclhl

25 - - ns

cclk 时期 sm4 (便条 1) t

cclkw

75 - - ns

cclk rising 至 cdout 数据 有效的 sm4 (便条 1) t

ccdov

- - 30 ns

cclk rising 至 cdout hi-z sm4 (便条 1) t

ccdot

- - 30 ns

cclk 下落 至 ccs 高 sm4 (便条 1) t

cccsh

0- -ns

重置 低 时间 较早的 至 pdn rising trph 100 - - ns

重置 低 支撑 时间 之后 pdn rising trhold 50 - - ms

注释: 7. 当 这 cs4218 是 在 主控 模式 (ssync 和 sclk 输出), 这 sclk 职责 循环 是 50%.

这 等式 是 为基础 在 这 选择 样本 频率 (fs) 和 这 号码 的 位 每 框架 (bpf).

CS4218

DS135F1 5