CS4341

8 DS298PP2

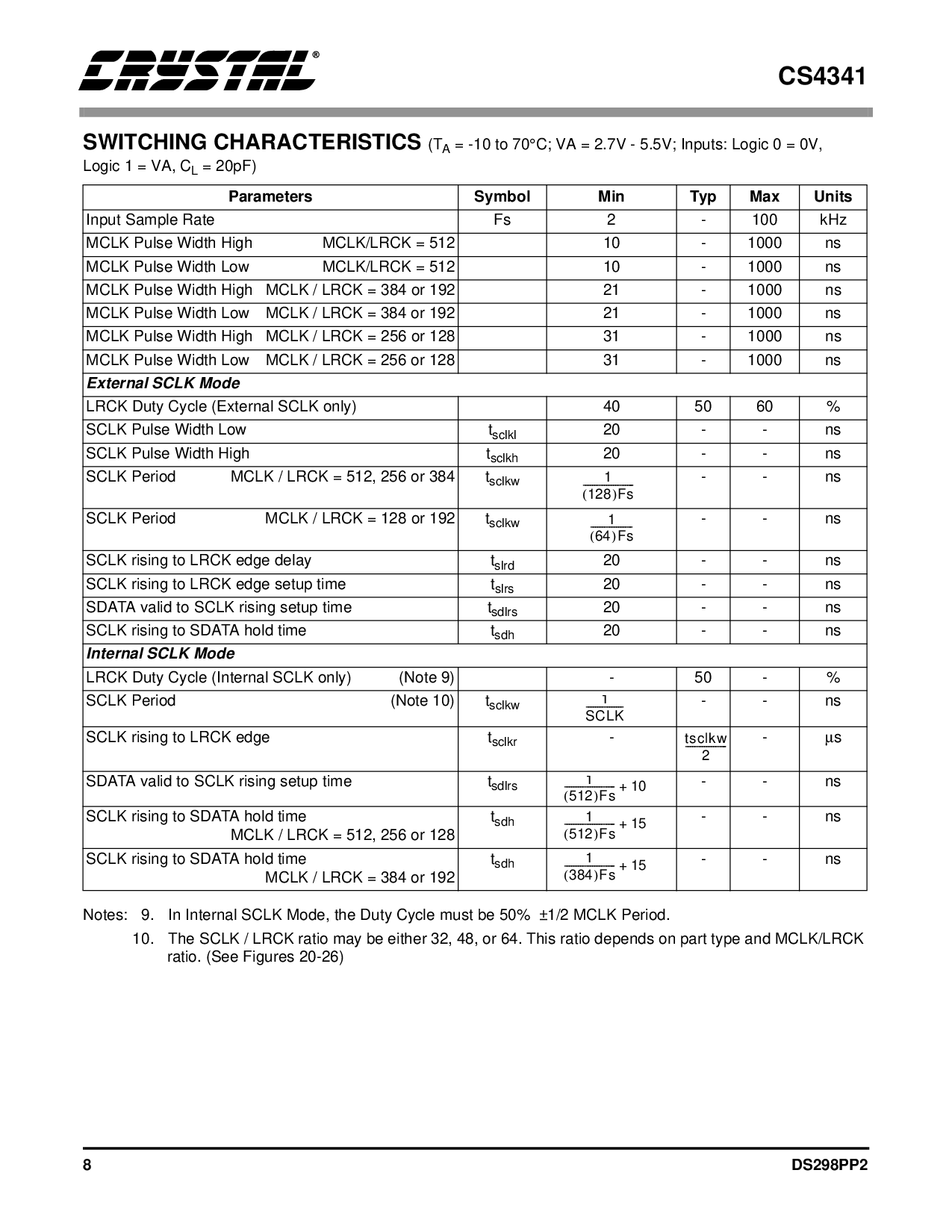

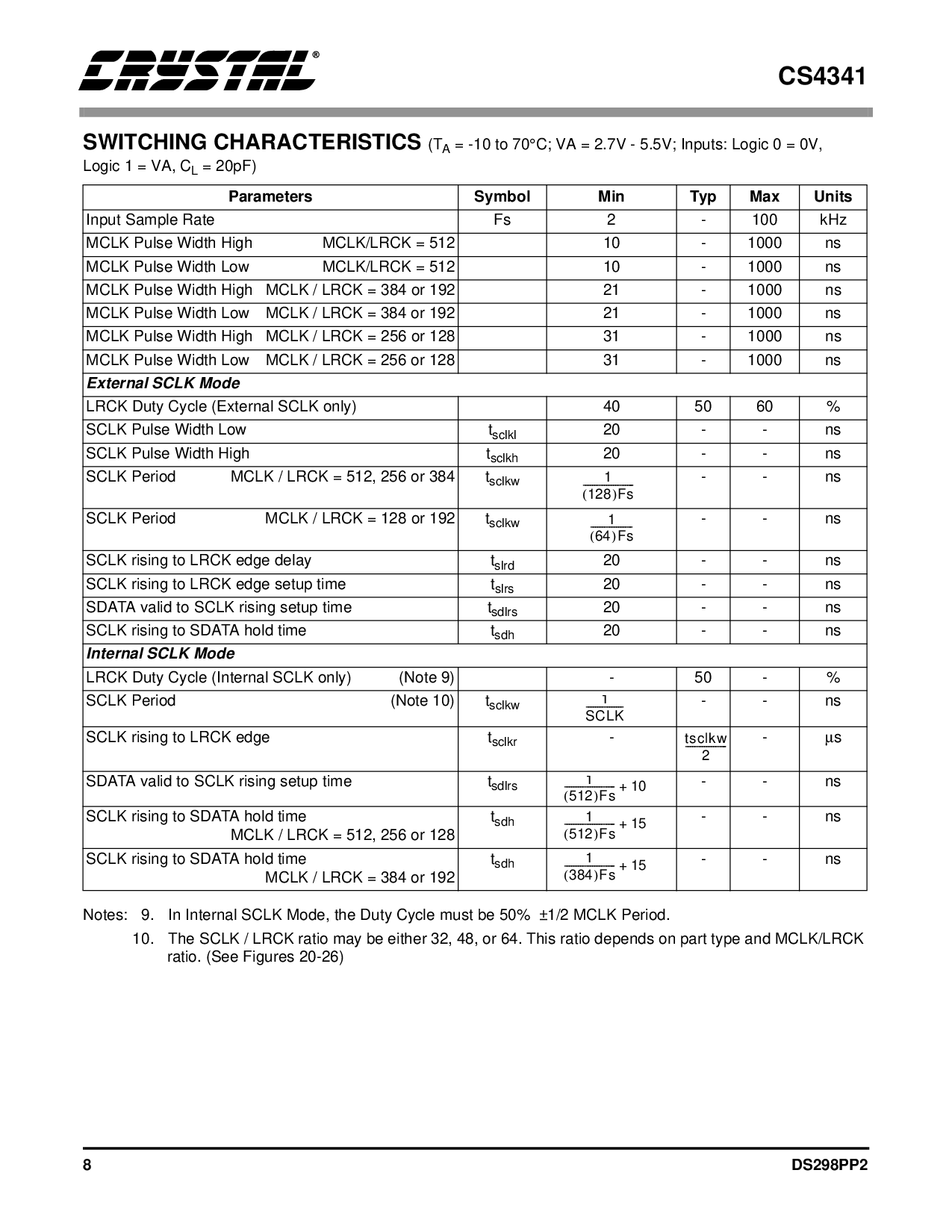

切换 特性

(t

一个

= -10 至 70

°c; va = 2.7v - 5.5v; 输入: 逻辑 0 = 0v,

逻辑 1 = va, c

L

= 20pf)

注释: 9. 在 内部的 sclk 模式, 这 职责 循环 必须 是 50% ±1/2 mclk 时期.

10. 这 sclk / lrck 比率 将 是 也 32, 48, 或者 64. 这个 比率 取决于 在 部分 类型 和 mclk/lrck

比率. (看 计算数量 20-26)

参数 标识 最小值 典型值 最大值 单位

输入 样本 比率 Fs 2 - 100 kHz

mclk 脉冲波 宽度 高 mclk/lrck = 512 10 - 1000 ns

mclk 脉冲波 宽度 低 mclk/lrck = 512 10 - 1000 ns

mclk 脉冲波 宽度 高 mclk / lrck = 384 或者 192 21 - 1000 ns

mclk 脉冲波 宽度 低 mclk / lrck = 384 或者 192 21 - 1000 ns

mclk 脉冲波 宽度 高 mclk / lrck = 256 或者 128 31 - 1000 ns

mclk 脉冲波 宽度 低 mclk / lrck = 256 或者 128 31 - 1000 ns

外部 sclk 模式

lrck 职责 循环 (外部 sclk 仅有的) 40 50 60 %

sclk 脉冲波 宽度 低 t

sclkl

20 - - ns

sclk 脉冲波 宽度 高 t

sclkh

20 - - ns

sclk 时期 mclk / lrck = 512, 256 或者 384 t

sclkw

--ns

sclk 时期 mclk / lrck = 128 或者 192 t

sclkw

--ns

sclk rising 至 lrck 边缘 延迟 t

slrd

20 - - ns

sclk rising 至 lrck 边缘 建制 时间 t

slrs

20 - - ns

sdata 有效的 至 sclk rising 建制 时间 t

sdlrs

20 - - ns

sclk rising 至 sdata 支撑 时间 t

sdh

20 - - ns

内部的 sclk 模式

lrck 职责 循环 (内部的 sclk 仅有的) (便条 9) - 50 - %

sclk 时期 (便条 10) t

sclkw

--ns

sclk rising 至 lrck 边缘 t

sclkr

--

µ

s

sdata 有效的 至 sclk rising 建制 时间 t

sdlrs

--ns

sclk rising 至 sdata 支撑 时间

mclk / lrck = 512, 256 或者 128

t

sdh

--ns

sclk rising 至 sdata 支撑 时间

mclk / lrck = 384 或者 192

t

sdh

--ns

1

128

()

Fs

----------------------

1

64

()

Fs

------------------

1

SCLK

----------------

tsclkw

2

------------------

1

512

()

Fs

----------------------10+

1

512

()

Fs

----------------------15+

1

384

()

Fs

----------------------15+