CYWUSB6932

CYWUSB6934

文档 38-16007 rev. *g 页 5 的 30

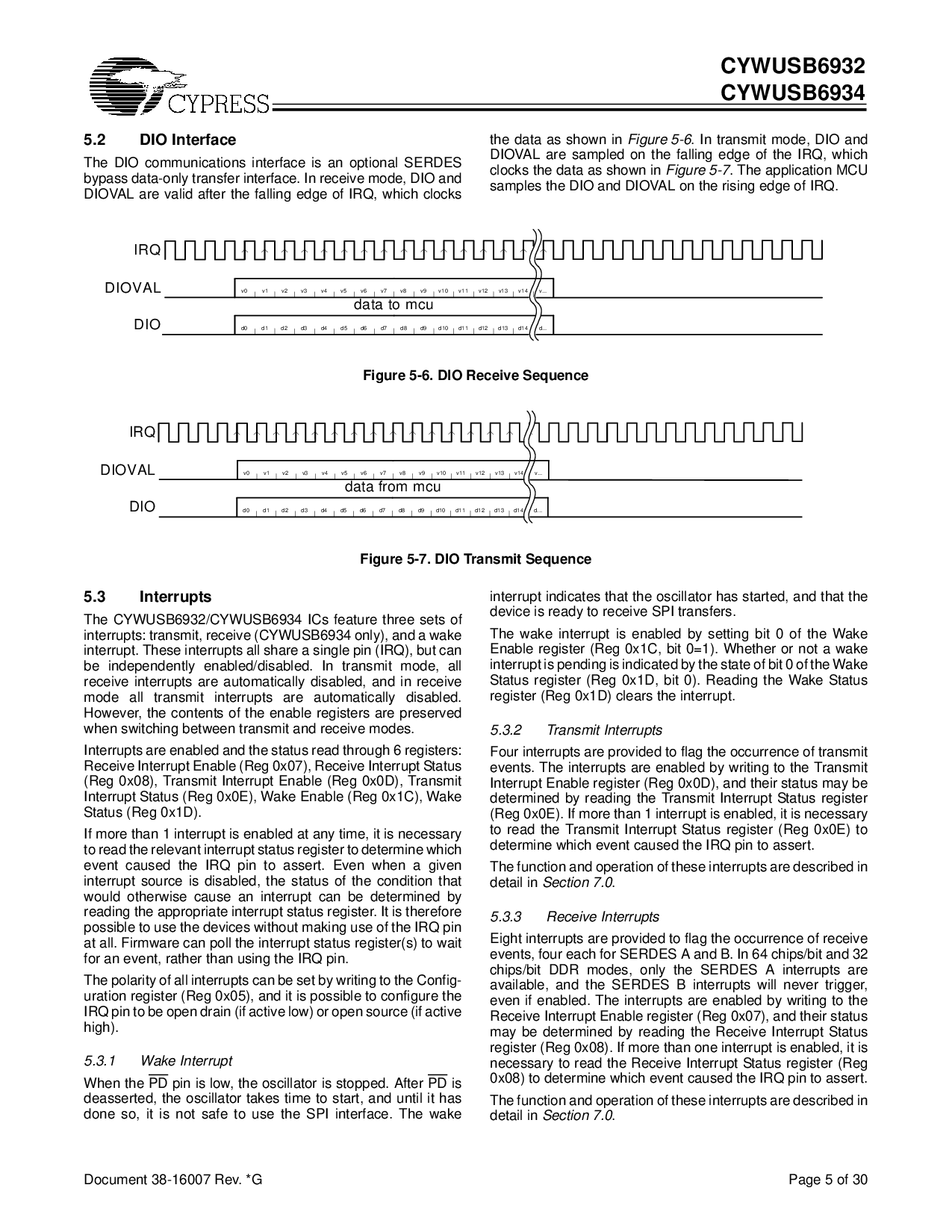

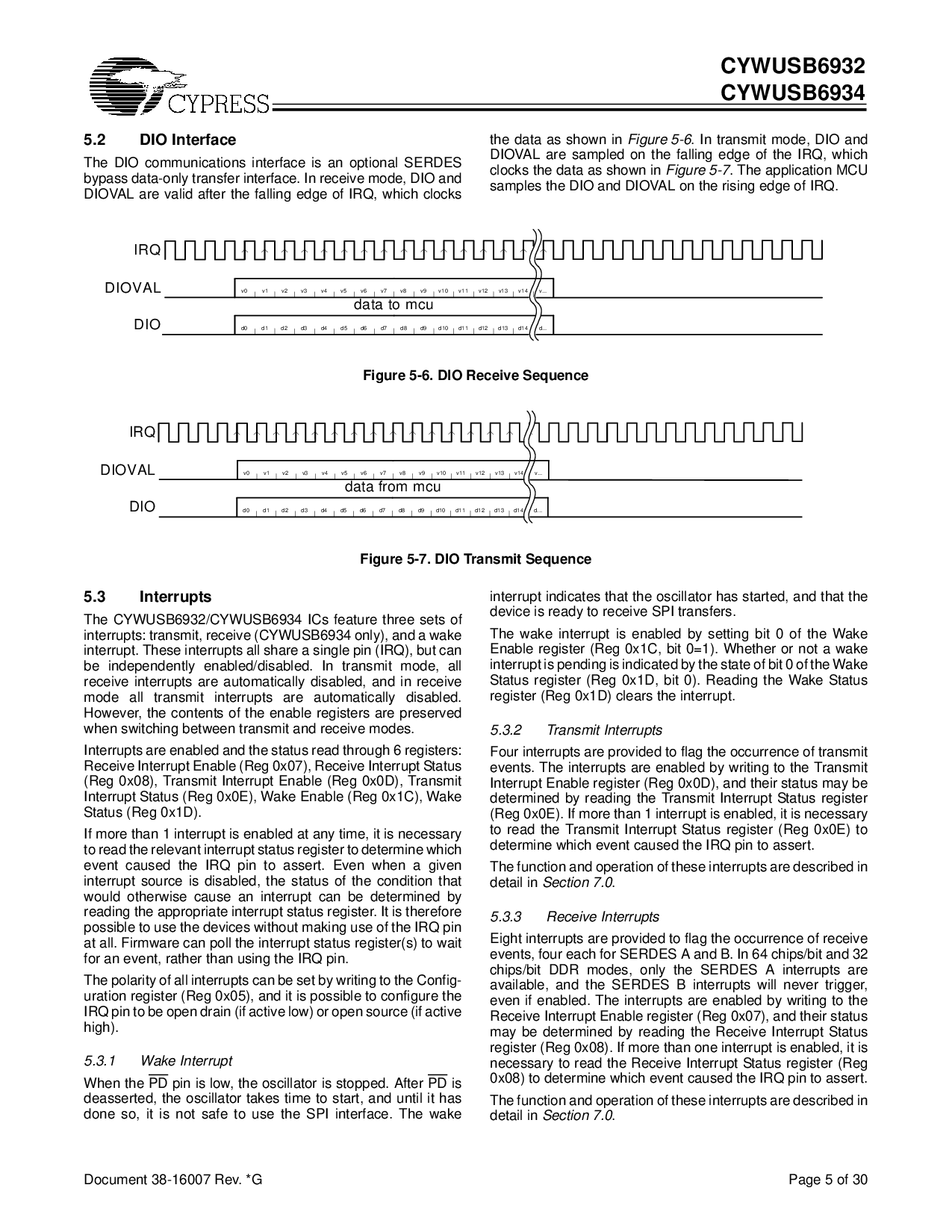

5.2 dio 接口

这 dio communications 接口 是 一个 optional serdes

绕过 数据-仅有的 转移 接口. 在 receive 模式, dio 和

dioval 是 有效的 之后 这 下落 边缘 的 irq, 这个 clocks

这 数据 作 显示 在

图示 5-6

. 在 transmit 模式, dio 和

dioval 是 抽样 在 这 下落 边缘 的 这 irq, 这个

clocks 这 数据 作 显示 在

图示 5-7

. 这 应用 mcu

样本 这 dio 和 dioval 在 这 rising 边缘 的 irq.

5.3 中断

这 cywusb6932/cywusb6934 ics 特性 三 sets 的

中断: transmit, receive (cywusb6934 仅有的), 和 一个 wake

中断. 这些 中断 所有 share 一个 单独的 管脚 (irq), 但是 能

是 independently 使能/无能. 在 transmit 模式, 所有

receive 中断 是 automatically 无能, 和 在 receive

模式 所有 transmit 中断 是 automatically 无能.

不管怎样, 这 内容 的 这 使能 寄存器 是 preserved

当 切换 在 transmit 和 receive 模式.

中断 是 使能 和 这 状态 读 通过 6 寄存器:

receive 中断 使能 (reg 0x07), receive 中断 状态

(reg 0x08), transmit 中断 使能 (reg 0x0d), transmit

中断 状态 (reg 0x0e), wake 使能 (reg 0x1c), wake

状态 (reg 0x1d).

如果 更多 比 1 中断 是 使能 在 任何 时间, 它 是 需要

至 读 这 相关的 中断 状态 寄存器 至 决定 这个

事件 造成 这 irq 管脚 至 assert. 甚至 当 一个 给

中断 源 是 无能, 这 状态 的 这 情况 那

将 否则 导致 一个 中断 能 是 决定 用

读 这 适合的 中断 状态 寄存器. 它 是 因此

可能 至 使用 这 设备 没有 制造 使用 的 这 irq 管脚

在 所有. firmware 能 poll 这 中断 状态 寄存器(s) 至 wait

为 一个 事件, 相当 比 使用 这 irq 管脚.

这 极性 的 所有 中断 能 是 设置 用 writing 至 这 config-

uration 寄存器 (reg 0x05), 和 它 是 可能 至 配置 这

irq 管脚 至 是 打开 流 (如果 起作用的 低) 或者 打开 源 (如果 起作用的

高).

5.3.1 wake 中断

当 这 pd管脚 是 低, 这 振荡器 是 stopped. 之后 pd是

deasserted, 这 振荡器 takes 时间 至 开始, 和 直到 它 有

完毕 所以, 它 是 不 safe 至 使用 这 spi 接口. 这 wake

中断 indicates 那 这 振荡器 有 started, 和 那 这

设备 是 准备好 至 receive spi transfers.

这 wake 中断 是 使能 用 设置 位 0 的 这 wake

使能 寄存器 (reg 0x1c, 位 0=1). whether 或者 不 一个 wake

中断 是 pending 是 表明 用 这 状态 的 位 0 的 这 wake

状态 寄存器 (reg 0x1d, 位 0). 读 这 wake 状态

寄存器 (reg 0x1d) clears 这 中断.

5.3.2 transmit 中断

四 中断 是 提供 至 标记 这 occurrence 的 transmit

events. 这 中断 是 使能 用 writing 至 这 transmit

中断 使能 寄存器 (reg 0x0d), 和 它们的 状态 将 是

决定 用 读 这 transmit 中断 状态 寄存器

(reg 0x0e). 如果 更多 比 1 中断 是 使能, 它 是 需要

至 读 这 transmit 中断 状态 寄存器 (reg 0x0e) 至

决定 这个 事件 造成 这 irq 管脚 至 assert.

这 函数 和 运作 的 这些 中断 是 描述 在

detail 在

部分 7.0

.

5.3.3 receive 中断

第八 中断 是 提供 至 标记 这 occurrence 的 receive

events, 四 各自 为 serdes 一个 和 b. 在 64 碎片/位 和 32

碎片/位 ddr 模式, 仅有的 这 serdes 一个 中断 是

有, 和 这 serdes b 中断 将 从不 触发,

甚至 如果 使能. 这 中断 是 使能 用 writing 至 这

receive 中断 使能 寄存器 (reg 0x07), 和 它们的 状态

将 是 决定 用 读 这 receive 中断 状态

寄存器 (reg 0x08). 如果 更多 比 一个 中断 是 使能, 它 是

需要 至 读 这 receive 中断 状态 寄存器 (reg

0x08) 至 决定 这个 事件 造成 这 irq 管脚 至 assert.

这 函数 和 运作 的 这些 中断 是 描述 在

detail 在

部分 7.0

.

图示 5-6. dio receive sequence

图示 5-7. dio transmit sequence

DIOVAL

DIO

IRQ

d7d6d5d4d3d2

d...d14d13d12d11d10d9d8

d1d0

数据 至 mcu

v7v6v5v4v3v2

v...v14v13v12v11v10

v9v8v1v0

DIOVAL

DIO

IRQ

d7d6d5d4d3d2

d...d14d13d12d11d10d9d8

d1d0

数据 从 mcu

v7v6v5v4v3v2

v...v14v13v12v11v10

v9v8

v1v0