rev. 0

ad5332/ad5333/ad5342/ad5343

–

5

–

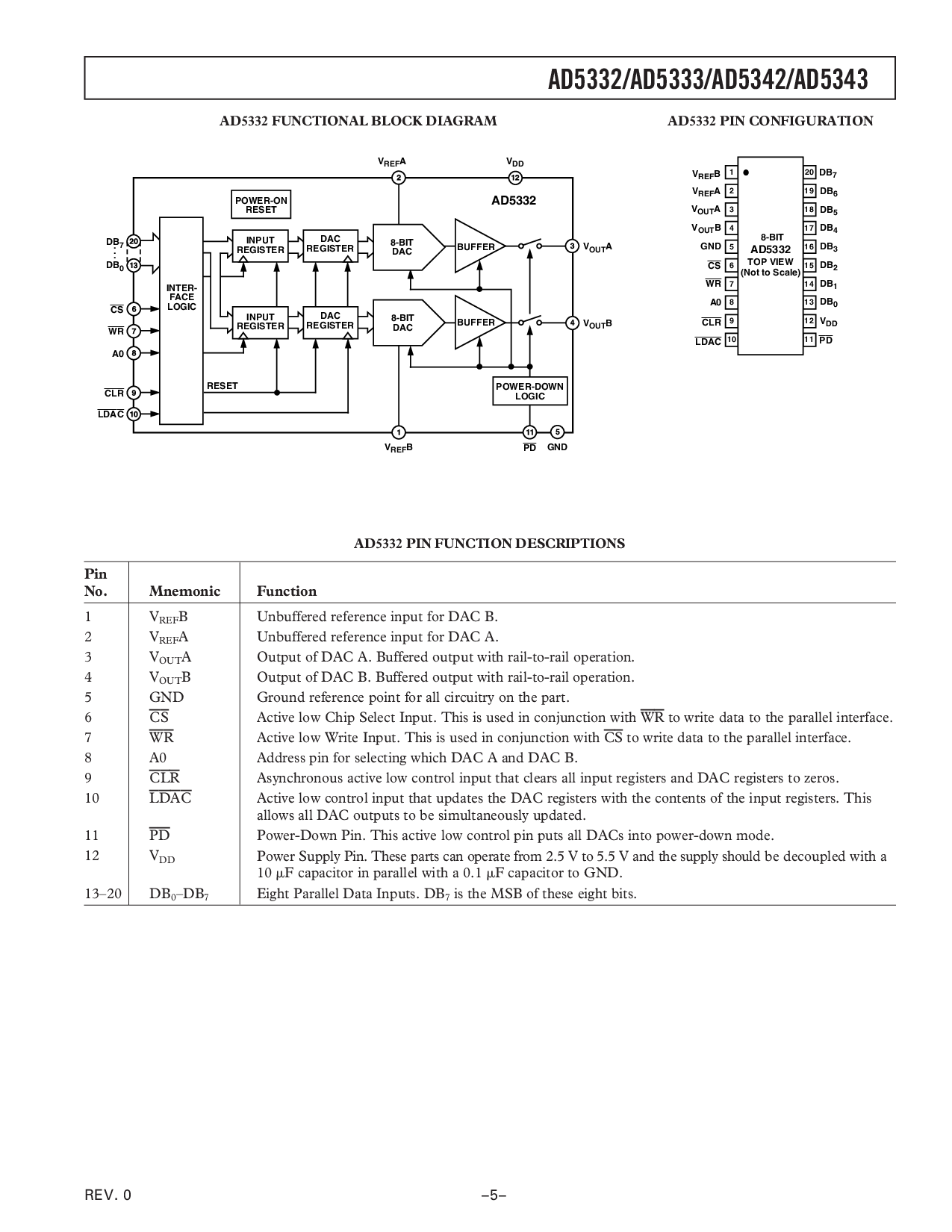

ad5332 函数的 块 图解

电源-在

重置

DAC

寄存器

DAC

寄存器

输入

寄存器

输入

寄存器

inter-

面向

逻辑

DB

7

DB

0

CS

WR

A0

CLR

LDAC

.

.

.

V

REF

一个

重置

V

REF

B

V

输出

一个

缓存区

AD5332

V

输出

B

缓存区

V

DD

电源-向下

逻辑

PD

地

8-位

DAC

8-位

DAC

ad5332 管脚 函数 描述

管脚

非. Mnemonic 函数

1V

REF

B unbuffered 涉及 输入 为 dac b.

2V

REF

一个 unbuffered 涉及 输入 为 dac 一个.

3V

输出

一个 输出 的 dac 一个. 缓冲 输出 和 栏杆-至-栏杆 运作.

4V

输出

B 输出 的 dac b. 缓冲 输出 和 栏杆-至-栏杆 运作.

5 地 地面 涉及 要点 为 所有 电路系统 在 这 部分.

6

CS

起作用的 低 碎片 选择 输入. 这个 是 使用 在 conjunction 和

WR

至 写 数据 至 这 并行的 接口.

7

WR

起作用的 低 写 输入. 这个 是 使用 在 conjunction 和

CS

至 写 数据 至 这 并行的 接口.

8 A0 地址 管脚 为 selecting 这个 dac 一个 和 dac b.

9

CLR

异步的 起作用的 低 控制 输入 那 clears 所有 输入 寄存器 和 dac 寄存器 至 zeros.

10

LDAC

起作用的 低 控制 输入 那 updates 这 dac 寄存器 和 这 内容 的 这 输入 寄存器. 这个

准许 所有 dac 输出 至 是 同时发生地 updated.

11

PD

电源-向下 管脚. 这个 起作用的 低 控制 管脚 puts 所有 dacs 在 电源-向下 模式.

12 V

DD

电源 supply 管脚. 这些 部分 能 运作 从 2.5 v 至 5.5 v 和 这 供应 should 是 decoupled 和 一个

10

f 电容 在 并行的 和 一个 0.1

f 电容 至 地.

13–20 DB

0

–DB

7

第八 并行的 数据 输入. db

7

是 这 msb 的 这些 第八 位.

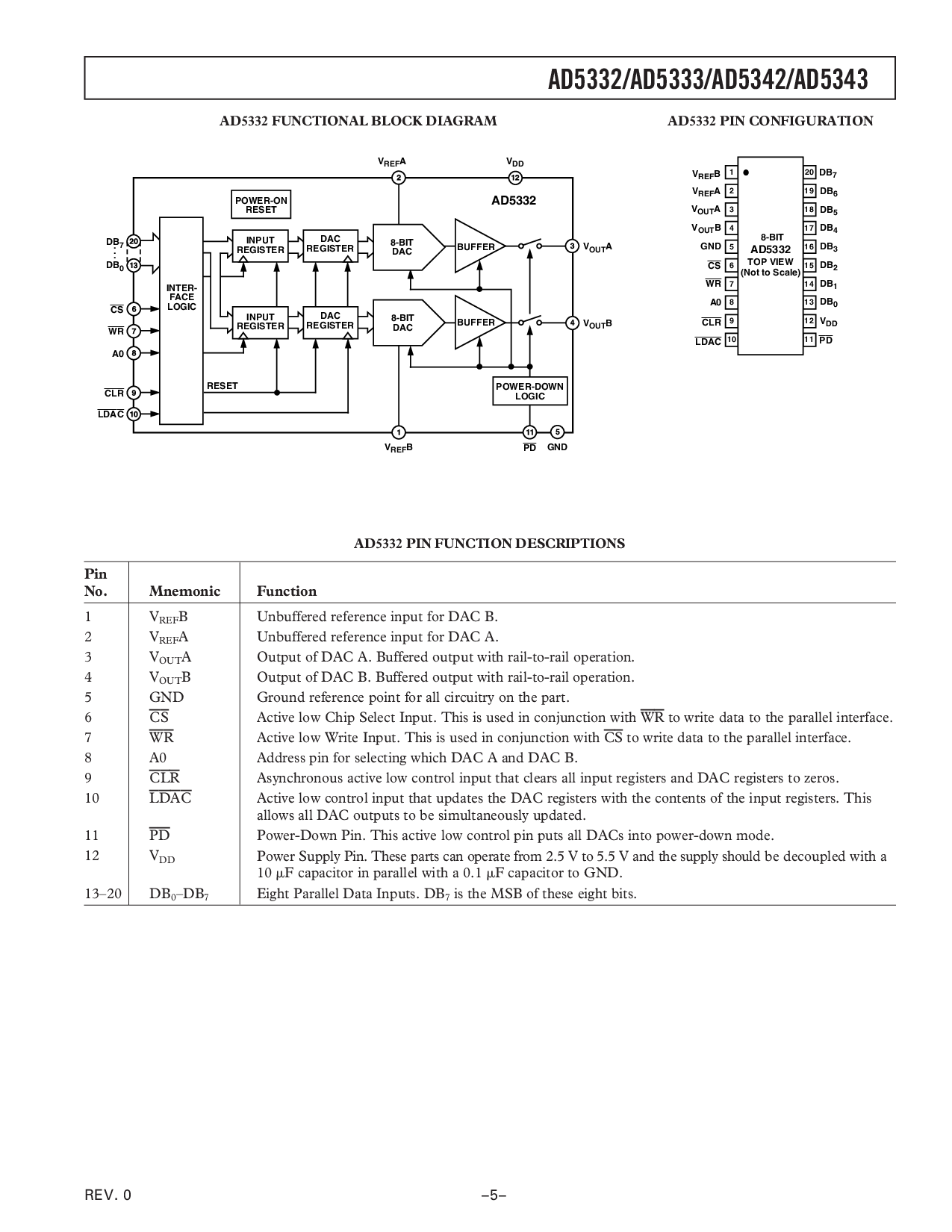

ad5332 管脚 配置

顶 视图

(不 至 规模)

20

19

18

17

16

15

14

13

12

11

1

2

3

4

5

6

7

8

9

10

AD5332

LDAC

A0

WR

CS

地

V

REF

B

V

REF

一个

V

输出

B

V

输出

一个

PD

V

DD

DB

0

DB

1

DB

2

DB

3

DB

4

DB

5

DB

6

DB

7

8-位

CLR