初步的 技术的 数据 ad5601/ad5611/ad5621

rev. prc | 页 13 的 20

一般 描述

d/一个 部分

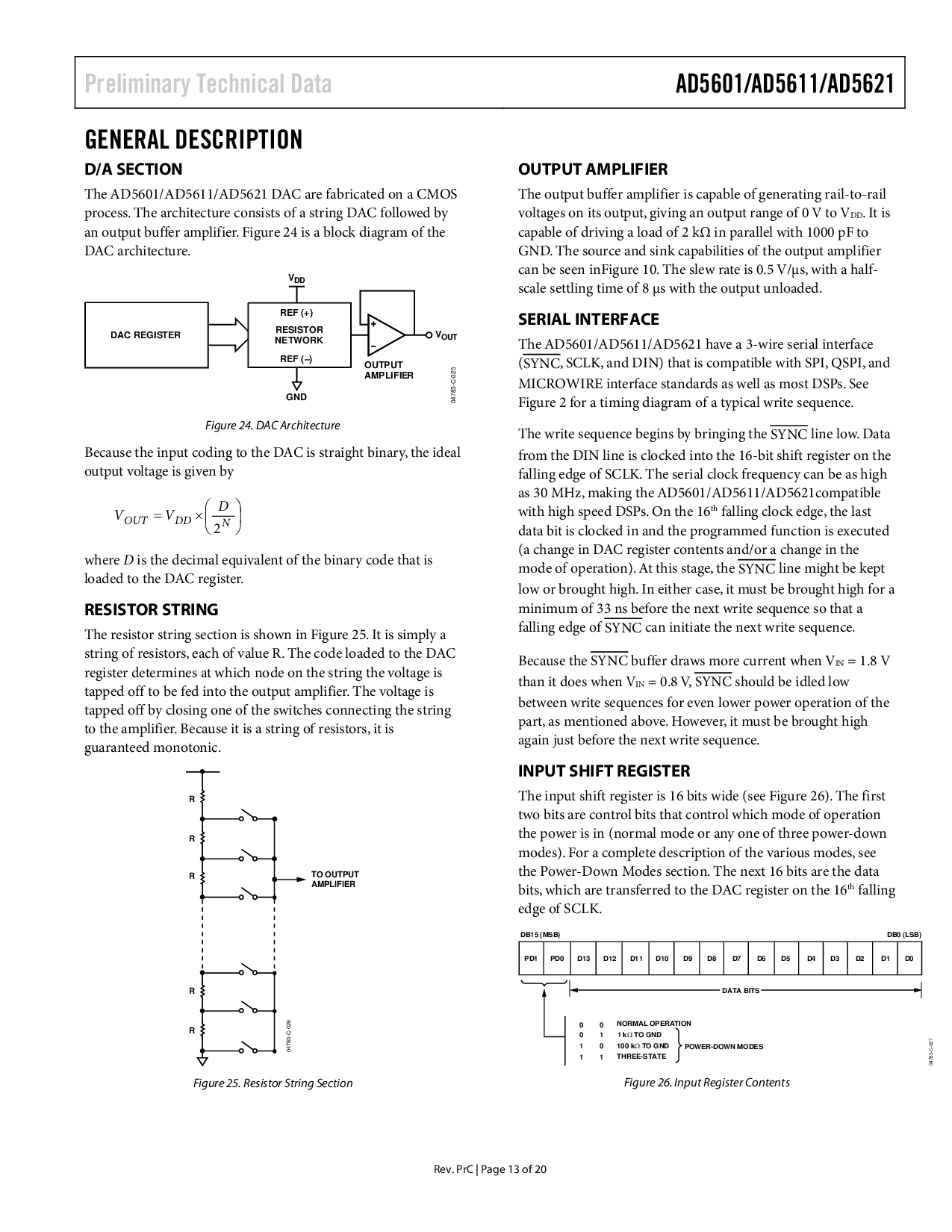

这 ad5601/ad5611/ad5621 dac 是 fabricated 在 一个 cmos

处理. 这 architecture 组成 的 一个 string dac followed 用

一个 输出 缓存区 放大器. 图示 24 是 一个 块 图解 的 这

dac architecture.

V

DD

V

输出

地

电阻

网络

ref (+)

ref (–)

输出

放大器

dac 寄存器

04783-c-025

图示 24. dac architecture

因为 这 输入 编码 至 这 dac 是 笔直地 二进制的, 这 完美的

输出 电压 是 给 用

⎟

⎠

⎞

⎜

⎝

⎛

×=

N

DD

输出

D

VV

2

在哪里

D

是 这 decimal 相等的 的 这 二进制的 代号 那 是

承载 至 这 dac 寄存器.

电阻 string

这 电阻 string 部分 是 显示 在 图示 25. 它 是 simply 一个

string 的 电阻器, 各自 的 值 r. 这 代号 承载 至 这 dac

寄存器 确定 在 这个 node 在 这 string 这 电压 是

抽头的 止 至 是 喂养 在 这 输出 放大器. 这 电压 是

抽头的 止 用 closing 一个 的这 switches 连接 这 string

至 这 放大器. 因为 它 是 一个 string 的 电阻器, 它 是

有保证的 monotonic.

R

R

R

R

R

至 输出

放大器

04783-c-026

图示 25. 电阻 string 部分

输出 放大器

这 输出 缓存区 放大器 是 有能力 的 generating 栏杆-至-栏杆

电压 在 它的 输出, 给 一个 输出 范围 的0 v 至 v

DD

. 它 是

有能力 的 驱动 一个 加载 的 2 kΩ 在 并行的 和 1000 pf 至

地. 这 源 和 下沉 能力 的 这 输出 放大器

能 是 seen infigure 10. 这 回转 比率 是 0.5 v/µs, 和 一个 half-

规模 安排好 时间 的8 µs 和 这 输出 unloaded.

串行 接口

这 ad5601/ad5611/ad5621 有 一个 3-线 串行 接口

(

同步

, sclk, 和DIn)th在is 竞赛atiblew它h spi, qspi, 和

microwire 接口 standards 作 好 作 大多数 dsps. 看

图示 2 为 一个 定时 图解 的 一个 典型 写 sequence.

这 写 sequence begins 用 bringing 这

同步

线条 低. 数据

从 这 din 线条 是 clocked 在 这 16-位 变换 寄存器 在 这

下落 边缘 的 sclk. 这 串行 时钟 频率 能 是 作 高

作 30 mhz, 制造 这 ad5601/ad5611/ad5621compatible

和 高 速 dsps. 在 这 16

th

下落 时钟 边缘, 这 last

数据 位 是 clocked 在 和 这 编写程序 函数 是 executed

(一个 改变 在 dac 寄存器 内容 和/或者 一个 改变 在 这

模式 的运作). 在 这个 平台, 这

同步

线条 might 是 保持

低 或者 brought 高. 在 也 情况, 它 必须 是 brought 高 为 一个

最小 的 33 ns 在之前 这 next 写 sequence 所以 那 一个

下落 边缘 的

同步

能 initiate 这 next 写 sequence.

因为 这

同步

缓存区 牵引 更多 电流 当 v

在

= 1.8 v

比 它 做 当 v

在

= 0.8 v,

同步

应当 是 idled 低

在 写 sequences 为 甚至 更小的 电源 运作 的 这

部分, 作 提到 在之上. 不管怎样, 它 必须 是 brought 高

又一次 just 在之前 这 next 写 sequence.

输入 变换 寄存器

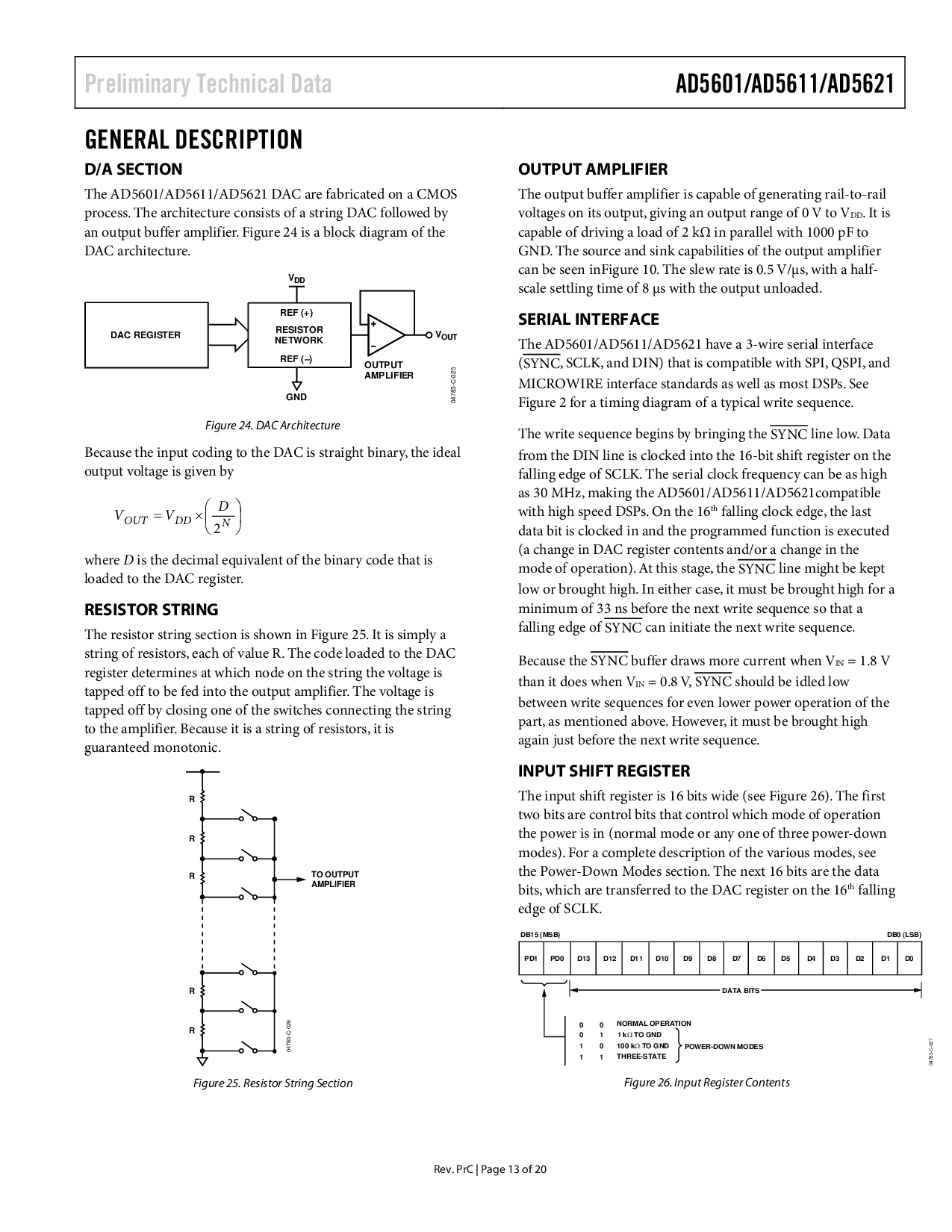

这 输入 变换 寄存器 是 16 位 宽 (看 图示 26). 这 第一

二 位 是 控制 位 那 控制 这个 模式 的 运作

这 电源 是 在 (正常的 模式 或者 任何 一个 的 三 电源-向下

模式). 为 一个 完全 描述 的 这 各种各样的 模式, 看

这 电源-向下 模式 部分. 这 next 16 位 是 这 数据

位, 这个 是 transferred 至 这 dac 寄存器 在 这 16

th

下落

边缘 的 sclk.

数据 位

db15 (msb) db0 (lsb)

PD1 PD0 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

正常的 运作

1 k

Ω

至 地

100 k

Ω

至 地

三-状态

电源-向下 模式

0

0

1

1

0

1

0

1

04783-c-027

图示 26. 输入 寄存器 内容