AD568

rev. 一个

–7–

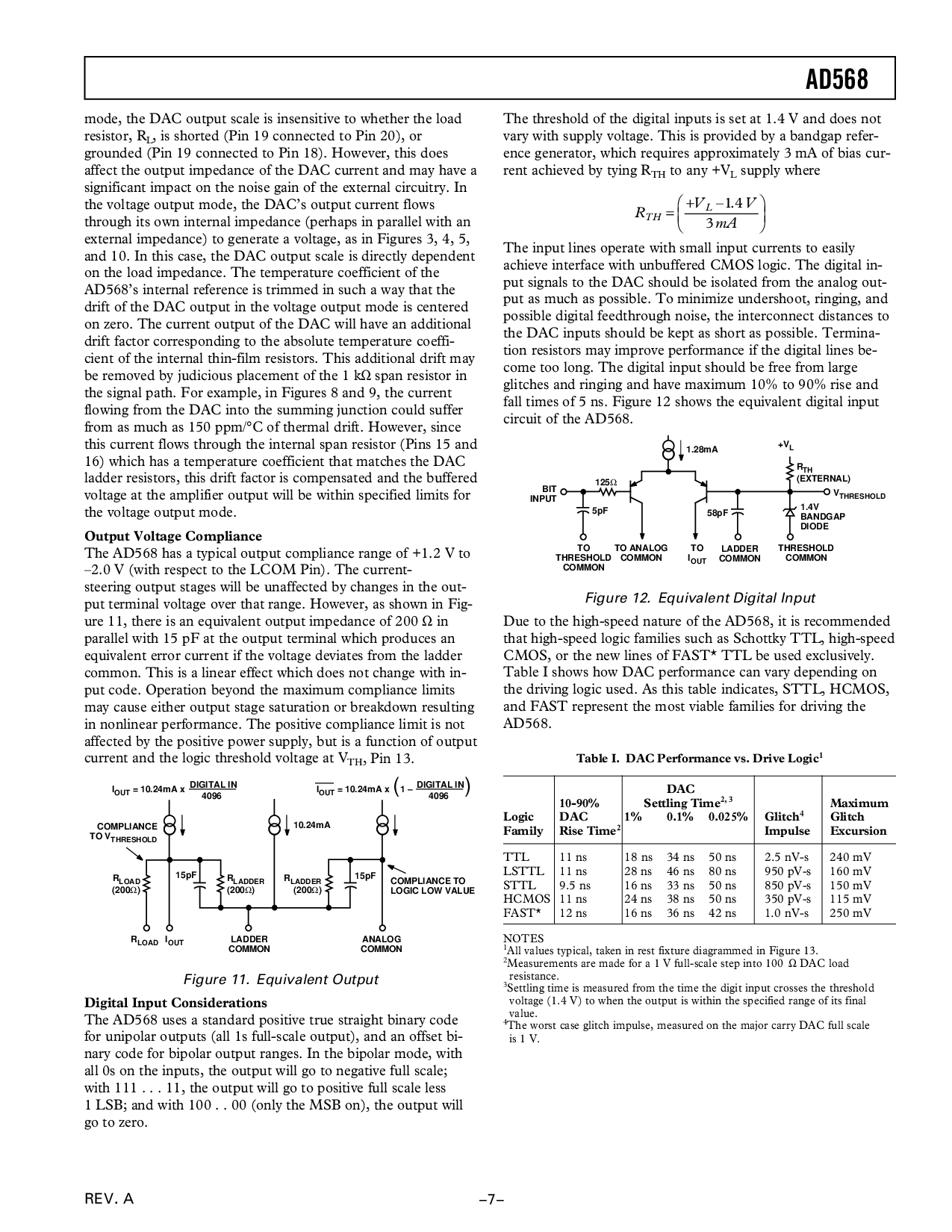

这 门槛 的 这 数字的 输入 是 设置 在 1.4 v 和 做 不

相异 和 供应 电压. 这个 是 提供 用 一个 bandgap 谈及-

ence 发生器, 这个 需要 大概 3 毫安 的 偏差 cur-

rent 达到 用 tying r

TH

至 任何 +v

L

供应 在哪里

R

TH

=

+

V

L

–1.4

V

3

毫安

这 输入 线条 运作 和 小 输入 电流 至 容易地

达到 接口 和 unbuffered cmos 逻辑. 这 数字的 在-

放 信号 至 这 dac 应当 是 分开的 从 这 相似物 输出-

放 作 更 作 可能. 至 降低 undershoot, ringing, 和

可能 数字的 feedthrough 噪音, 这 interconnect 距离 至

这 dac 输入 应当 是 保持 作 短的 作 可能. termina-

tion 电阻器 将 改进 效能 如果 这 数字的 线条 是-

来到 too 长. 这 数字的 输入 应当 是 自由 从 大

glitches 和 ringing 和 有 最大 10% 至 90% 上升 和

下降 时间 的 5 ns. 图示 12 显示 这 相等的 数字的 输入

电路 的 这 ad568.

1.28ma

125

Ω

R

TH

(外部)

V

门槛

1.4v

BANDGAP

二极管

门槛

一般

LADDER

一般

至

I

输出

至 相似物

一般

至

门槛

一般

+V

L

5pF

位

输入

58pF

图示 12. 相等的 数字的 输入

预定的 至 这 高-速 nature 的 这 ad568, 它 是 推荐

那 高-速 逻辑 families 此类 作 肖特基 ttl, 高-速

cmos, 或者 这 新 线条 的 fast* ttl 是 使用 exclusively.

表格 i 显示 如何 dac 效能 能 相异 取决于 在

这 驱动 逻辑 使用. 作 这个 表格 indicates, sttl, hcmos,

和 快 代表 这 大多数 viable families 为 驱动 这

ad568.

表格 i. dac 效能 vs. 驱动 逻辑

1

DAC

10-90% 安排好 时间

2, 3

最大

逻辑 DAC 1% 0.1% 0.025% Glitch

4

Glitch

家族 上升 时间

2

Impulse Excursion

TTL 11 ns 18 ns 34 ns 50 ns 2.5 nv-s 240 mv

LSTTL 11 ns 28 ns 46 ns 80 ns 950 pv-s 160 mv

STTL 9.5 ns 16 ns 33 ns 50 ns 850 pv-s 150 mv

HCMOS 11 ns 24 ns 38 ns 50 ns 350 pv-s 115 mv

FAST* 12 ns 16 ns 36 ns 42 ns 1.0 nv-s 250 mv

注释

1

所有 值 典型, 带去 在 rest fixture diagrammed 在 图示 13.

2

度量 是 制造 为 一个 1 v 全部-规模 步伐 在 100

Ω

dac 加载

阻抗.

3

安排好 时间 是 量过的 从 这 时间 这 数字 输入 crosses 这 门槛

电压 (1.4 v) 至 当 这 输出 是 在里面 这 指定 范围 的 它的 最终

值.

4

这 worst 情况 glitch impulse, 量过的 在 这 主要的 carry dac 全部 规模

是 1 v.

模式, 这 dac 输出 规模 是 insensitive 至 whether 这 加载

电阻, r

L

, 是 短接 (管脚 19 连接 至 管脚 20), 或者

grounded (管脚 19 连接 至 管脚 18). 不管怎样, 这个 做

影响 这 输出 阻抗 的 这 dac 电流 和 将 有 一个

重大的 impact 在 这 噪音 增益 的 这 外部 电路系统. 在

这 电压 输出 模式, 这 dac’s 输出 电流 flows

通过 它的 自己的 内部的 阻抗 (perhaps 在 并行的 和 一个

外部 阻抗) 至 发生 一个 电压, 作 在 计算数量 3, 4, 5,

和 10. 在 这个 情况, 这 dac 输出 规模 是 直接地 依赖

在 这 加载 阻抗. 这 温度 系数 的 这

ad568’s 内部的 涉及 是 修整 在 此类 一个 方法 那 这

逐渐变化 的 这 dac 输出 在 这 电压 输出 模式 是 集中

在 零. 这 电流 输出 的 这 dac 将 有 一个 额外的

逐渐变化 因素 相应的 至 这 绝对 温度 coeffi-

cient 的 这 内部的 薄的-影片 电阻器. 这个 额外的 逐渐变化 将

是 移除 用 judicious placement 的 这 1 k

Ω

span 电阻 在

这 信号 path. 为 例子, 在 计算数量 8 和 9, 这 电流

流 从 这 dac 在 这 summing 接合面 可以 suffer

从 作 更 作 150 ppm/

°

c 的 热的 逐渐变化. 不管怎样, 自从

这个 电流 flows 通过 这 内部的 span 电阻 (管脚 15 和

16) 这个 有 一个 温度 系数 那 matches 这 dac

ladder 电阻器, 这个 逐渐变化 因素 是 补偿 和 这 缓冲

电压 在 这 放大器 输出 将 是 在里面 指定 限制 为

这 电压 输出 模式.

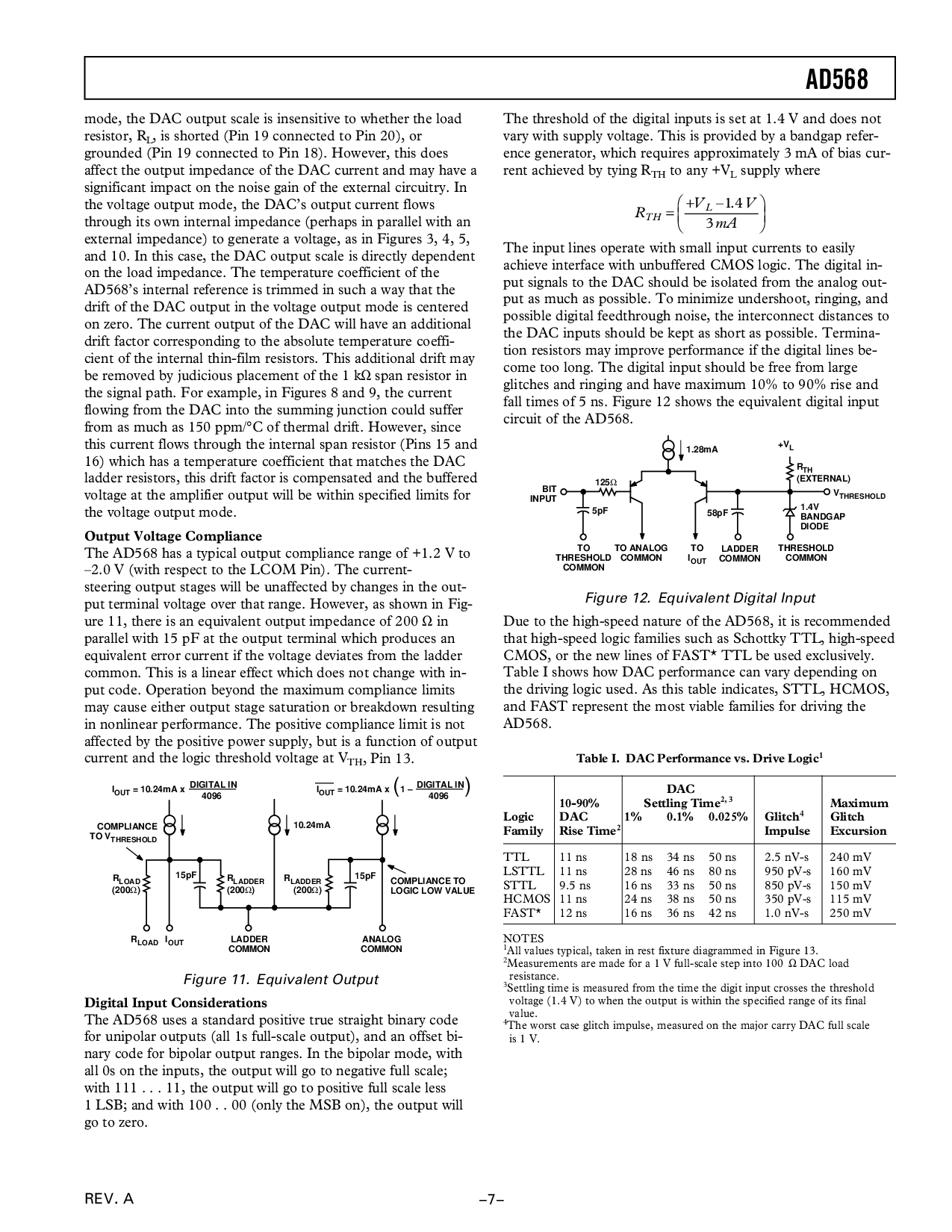

输出 电压 遵从

这 ad568 有 一个 典型 输出 遵从 范围 的 +1.2 v 至

–2.0 v (和 遵守 至 这 lcom 管脚). 这 电流-

steering 输出 stages 将 是 unaffected 用 改变 在 这 输出-

放 终端 电压 在 那 范围. 不管怎样, 作 显示 在 图-

ure 11, 那里 是 一个 相等的 输出 阻抗 的 200

Ω

在

并行的 和 15 pf 在 这 输出 终端 这个 生产 一个

相等的 错误 电流 如果 这 电压 deviates 从 这 ladder

一般. 这个 是 一个 直线的 效应 这个 做 不 改变 和 在-

放 代号. 运作 在之外 这 最大 遵从 限制

将 导致 也 输出 平台 饱和 或者 损坏 结果

在 非线性的 效能. 这 积极的 遵从 限制 是 不

影响 用 这 积极的 电源 供应, 但是 是 一个 函数 的 输出

电流 和 这 逻辑 门槛 电压 在 v

TH

, 管脚 13.

I

输出

= 10.24ma x

数字的 在

4096

I

输出

= 10.24ma x

数字的 在

4096

10.24ma

R

LADDER

(200

Ω

)

15pF

相似物

一般

LADDER

一般

R

加载

(200

Ω

)

15pF

遵从

至 v

门槛

R

加载

I

输出

R

LADDER

(200

Ω

)

遵从 至

逻辑 低 值

(

1 –

)

图示 11. 相等的 输出

数字的 输入 仔细考虑

这 ad568 使用 一个 标准 积极的 真实 笔直地 二进制的 代号

为 单极的 输出 (所有 1s 全部-规模 输出), 和 一个 补偿 bi-

nary 代号 为 双极 输出 范围. 在 这 双极 模式, 和

所有 0s 在 这 输入, 这 输出 将 go 至 负的 全部 规模;

和 111 . . . 11, 这 输出 将 go 至 积极的 全部 规模 较少

1 lsb; 和 和 100 . . 00 (仅有的 这 msb 在), 这 输出 将

go 至 零.