ad7705/ad7706

–13–rev. 一个

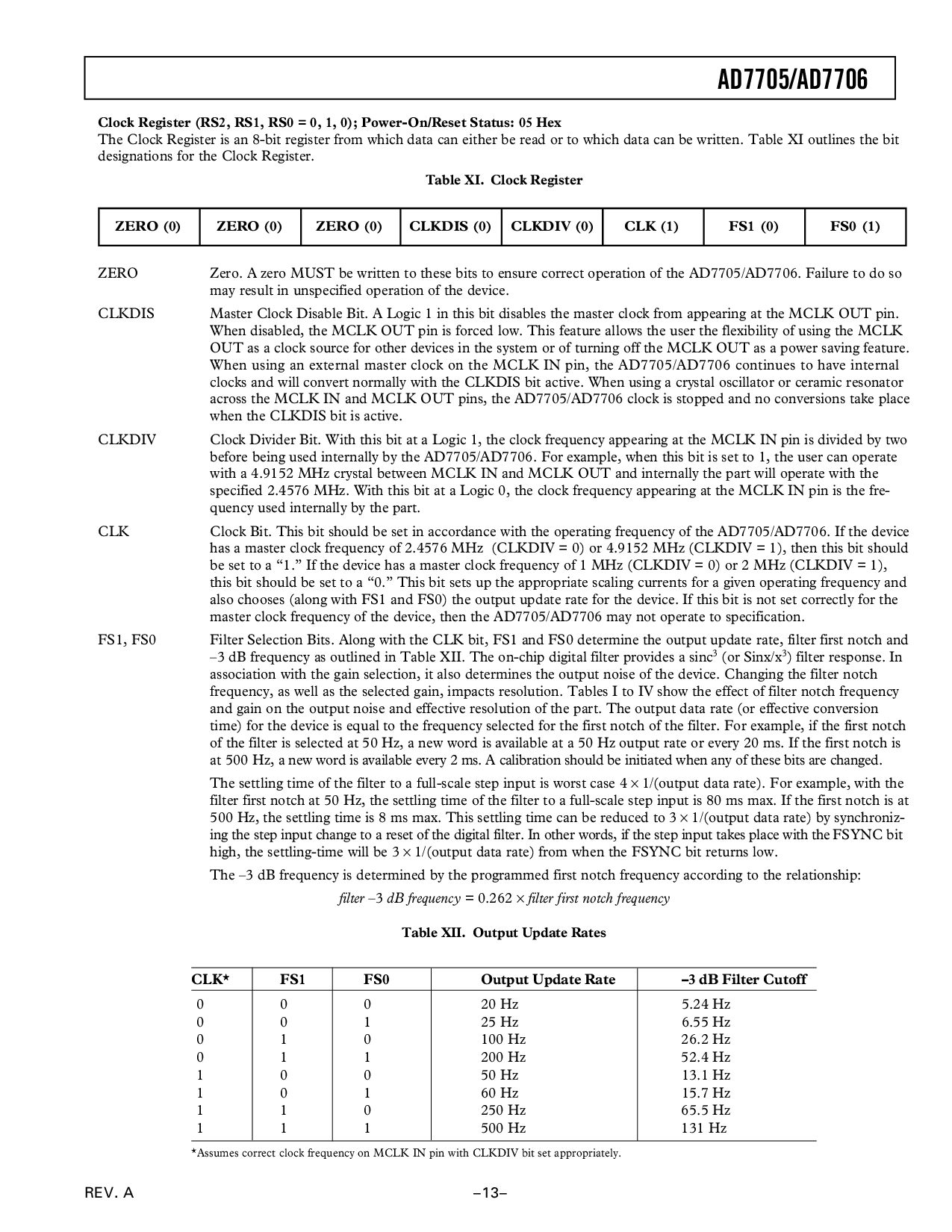

时钟 寄存器 (rs2, rs1, rs0 = 0, 1, 0); power-on/reset status: 05␣ 十六进制

这 时钟 寄存器 是 一个 8-位 寄存器 从 这个 数据 能 也 是 读 或者 至 这个 数据 能 是 写. 表格 xi 轮廓 这 位

designations 为 这 时钟 寄存器.

表格 xi. 时钟 寄存器

零 (0) 零 (0) 零 (0) clkdis (0) clkdiv (0) clk (1) FS1(0) FS0(1)

零 零. 一个 零 必须 是 写 至 这些 位 至 确保 准确无误的 运作 的 这 ad7705/ad7706. 失败 至 做 所以

将 结果 在 未说明的 运作 的 这 设备.

CLKDIS 主控 时钟 使不能运转 位. 一个 逻辑 1 在 这个 位 使不能运转 这 主控 时钟 从 appearing 在 这 mclk 输出 管脚.

当 无能, 这 mclk 输出 管脚 是 强迫 低. 这个 特性 准许 这 用户 这 flexibility 的 使用 这 mclk

输出 作 一个 时钟 源 为 其它 设备 在 这 系统 或者 的 turning 止 这 mclk 输出 作 一个 电源 节省 特性.

当 使用 一个 外部 主控 时钟 在 这 mclk 在 管脚, 这 ad7705/ad7706 持续 至 有 内部的

clocks 和 将 转变 正常情况下 和 这 clkdis 位 起作用的. 当 使用 一个 结晶 振荡器 或者 陶瓷的 共振器

横过 这 mclk 在 和 mclk 输出 管脚, 这 ad7705/ad7706 时钟 是 stopped 和 非 conversions 引领 放置

当 这 clkdis 位 是 起作用的.

CLKDIV 时钟 分隔物 位. 和 这个 位 在 一个 逻辑 1, 这 时钟 频率 appearing 在 这 mclk 在 管脚 是 分隔 用 二

在之前 正在 使用 内部 用 这 ad7705/ad7706. 为 例子, 当 这个 位 是 设置 至 1, 这 用户 能 运作

和 一个 4.9152 mhz 结晶 在 mclk 在 和 mclk 输出 和 内部 这 部分 将 运作 和 这

指定 2.4576 mhz. 和 这个 位 在 一个 逻辑 0, 这 时钟 频率 appearing 在 这 mclk 在 管脚 是 这 fre-

quency 使用 内部 用 这 部分.

CLK 时钟 位. 这个 位 应当 是 设置 在 一致 和 这 运行 频率 的 这 ad7705/ad7706. 如果 这 设备

有 一个 主控 时钟 频率 的 2.4576 mhz (clkdiv = 0) 或者 4.9152 mhz (clkdiv = 1), 然后 这个 位 应当

是 设置 至 一个 “1.” 如果 这 设备 有 一个 主控 时钟 频率 的 1 mhz (clkdiv = 0) 或者 2 mhz (clkdiv = 1),

这个 位 应当 是 设置 至 一个 “0.” 这个 位 sets 向上 这 适合的 范围调整 电流 为 一个 给 运行 频率 和

也 chooses (along 和 fs1 和 fs0) 这 输出 更新 比率 为 这 设备. 如果 这个 位 是 不 设置 correctly 为 这

主控 时钟 频率 的 这 设备, 然后 这 ad7705/ad7706 将 不 运作 至 规格.

fs1, fs0 过滤 选择 位. along 和 这 clk 位, fs1 和 fs0 决定 这 输出 更新 比率, 过滤 第一 notch 和

–3 db 频率 作 概述 在 表格 xii. 这 在-碎片 数字的 过滤 提供 一个 sinc

3

(或者 sinx/x

3

) 过滤 回馈. 在

协会 和 这 增益 选择, 它 也 确定 这 输出 噪音 的 这 设备. changing 这 过滤 notch

频率, 作 好 作 这 选择 增益, impacts 决议. tables i 至 iv 显示 这 效应 的 过滤 notch 频率

和 增益 在 这 输出 噪音 和 有效的 决议 的 这 部分. 这 输出 数据 比率 (或者 有效的 转换

时间) 为 这 设备 是 equal 至 这 频率 选择 为 这 第一 notch 的 这 过滤. 为 例子, 如果 这 第一 notch

的 这 过滤 是 选择 在 50 hz, 一个 新 文字 是 有 在 一个 50 hz 输出 比率 或者 每 20 ms. 如果 这 第一 notch 是

在 500 hz, 一个新 文字 是 有 每 2 ms. 一个 校准 应当 是 initiated 当 任何 的 这些 位 是 changed.

这 安排好 时间 的 这 过滤 至 一个 全部-规模 步伐 输入 是 worst 情况 4

×

1/(输出 数据 比率). 为 例子, 和 这

过滤 第一 notch 在 50 hz, 这 安排好 时间 的 这 过滤 至 一个 全部-规模 步伐 输入 是 80 ms 最大值 如果 这 第一 notch 是 在

500 hz, 这 安排好 时间 是 8 ms 最大值 这个 安排好 时间 能 是 减少 至 3

×

1/(输出 数据 比率) 用 synchroniz-

ing 这 步伐 输入 改变 至 一个 重置 的 这 数字的 过滤. 在 其它 words, 如果 这 步伐 输入 takes 放置 和 这 fsync 位

高, 这 安排好-时间 将 是 3

×

1/(输出 数据 比率) 从 当 这 fsync 位 returns 低.

这 –3 db 频率 是 决定 用 这 编写程序 第一 notch 频率 符合 至 这 relationship:

过滤 –

3

db 频率 =

0.262

×

过滤 第一 notch 频率

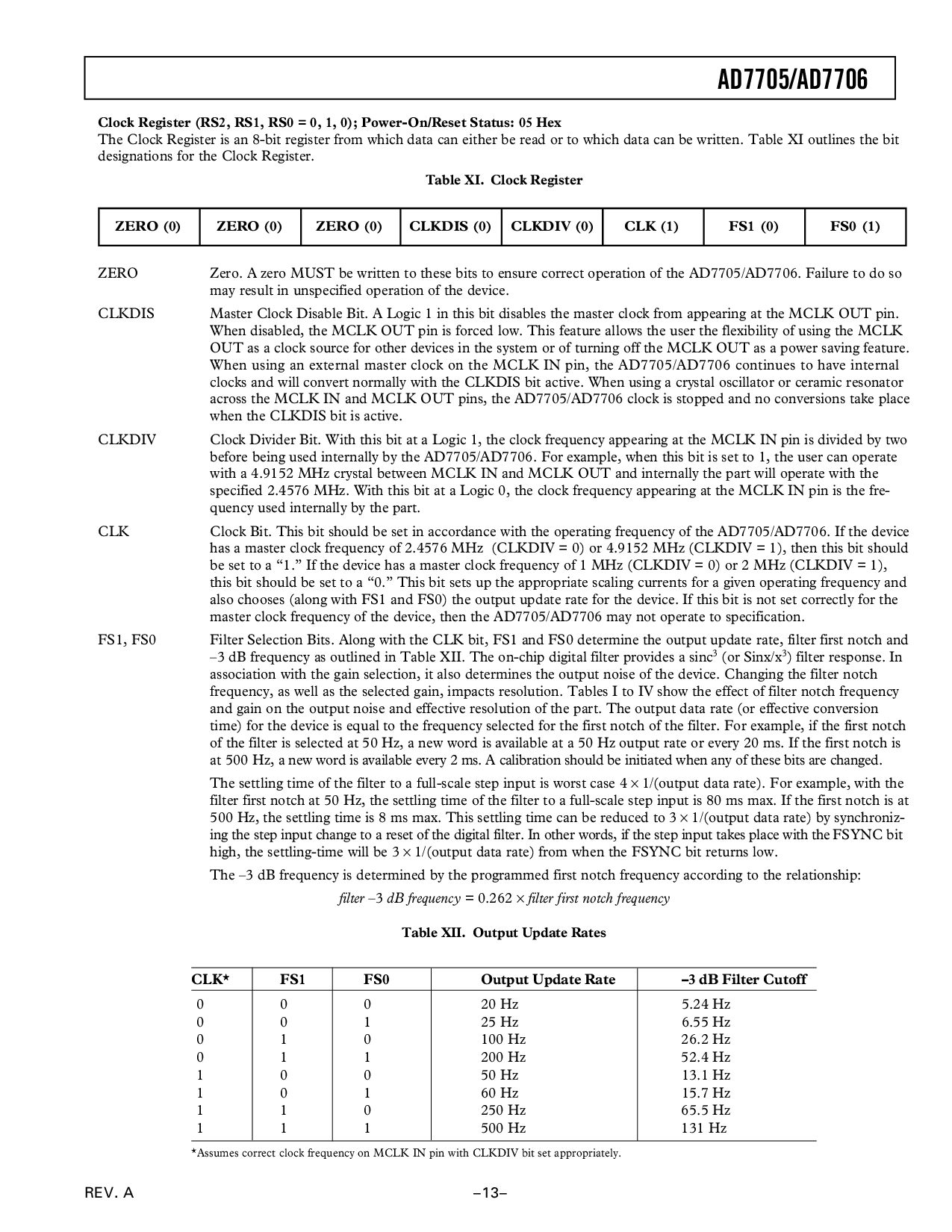

表格 xii. 输出 更新 比率

CLK* FS1 FS0 输出 更新 比率 –3 db 过滤 截止

0 0 0 20 hz 5.24 hz

0 0 1 25 hz 6.55 hz

0 1 0 100 hz 26.2 hz

0 1 1 200 hz 52.4 hz

1 0 0 50 hz 13.1 hz

1 0 1 60 hz 15.7 hz

1 1 0 250 hz 65.5 hz

1 1 1 500 hz 131 hz

*assumes 准确无误的 时钟 频率 在 mclk 在 管脚 和 clkdiv 位 设置 appropriately.