rev. 0

AD9753

–9–

函数的 描述

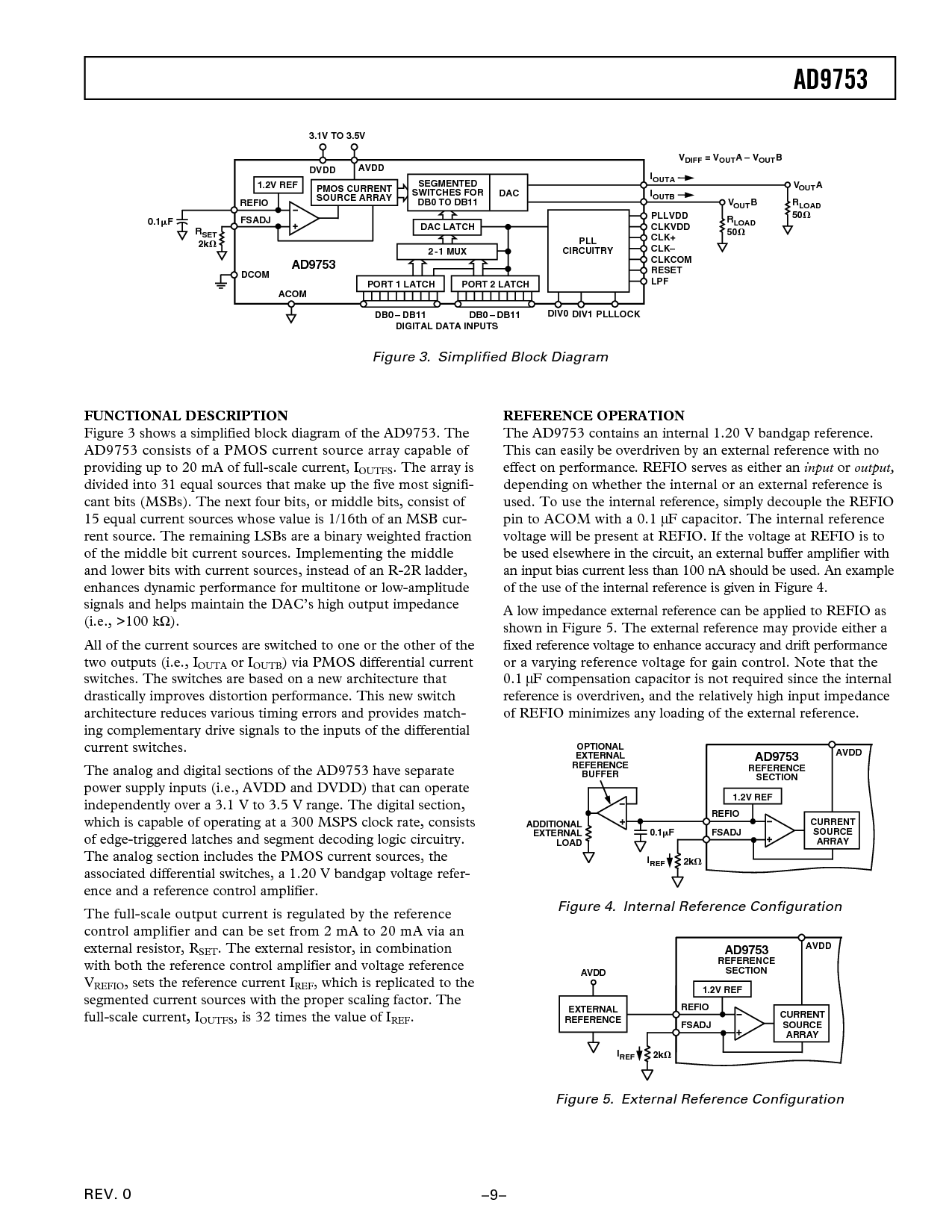

图示 3 显示 一个 simplified 块 图解 的 这 ad9753. 这

ad9753 组成 的 一个 pmos 电流 源 排列 有能力 的

供应 向上 至 20 毫安 的 全部-规模 电流, i

OUTFS

. 这 排列 是

分隔 在 31 equal 来源 那 制造 向上 这 five 大多数 signifi-

cant 位 (msbs). 这 next 四 位, 或者 middle 位, 组成 的

15 equal 电流 来源 谁的 值 是 1/16th 的 一个 msb cur-

rent 源. 这 remaining lsbs 是 一个 二进制的 weighted fraction

的 这 middle 位 电流 来源. implementing 这 middle

和 更小的 位 和 电流 来源, instead 的 一个 r-2r ladder,

enhances 动态 效能 为 multitone 或者 低-振幅

信号 和 helps 维持 这 dac’s 高 输出 阻抗

(i.e., >100 k

Ω

).

所有 的 这 电流 来源 是 切换 至 一个 或者 这 其它 的 这

二 输出 (i.e., i

OUTA

或者 i

OUTB

) 通过 pmos 差别的 电流

switches. 这 switches 是 为基础 在 一个 新 architecture 那

drastically 改进 扭曲量 效能. 这个 新 转变

architecture 减少 各种各样的 定时 errors 和 提供 相一致-

ing complementary 驱动 信号 至 这 输入 的 这 差别的

电流 switches.

这 相似物 和 数字的 sections 的 这 ad9753 有 独立的

电源 供应 输入 (i.e., avdd 和 dvdd) 那 能 运作

independently 在 一个 3.1 v 至 3.5 v 范围. 这 数字的 部分,

这个 是 有能力 的 运行 在 一个 300 msps 时钟 比率, 组成

的 边缘-triggered latches 和 段 解码 逻辑 电路系统.

这 相似物 部分 包含 这 pmos 电流 来源, 这

有关联的 差别的 switches, 一个 1.20 v bandgap 电压 谈及-

ence 和 一个 涉及 控制 放大器.

这 全部-规模 输出 电流 是 管制 用 这 涉及

控制 放大器 和 能 是 设置 从 2 毫安 至 20 毫安 通过 一个

外部 电阻, r

设置

. 这 外部 电阻, 在 结合体

和 两个都 这 涉及 控制 放大器 和 电压 涉及

V

REFIO

, sets 这 涉及 电流 i

REF

, 这个 是 replicated 至 这

segmented 电流 来源 和 这 恰当的 范围调整 因素. 这

全部-规模 电流, i

OUTFS

, 是 32 时间 这 值 的 i

REF

.

AD9753

I

OUTA

I

OUTB

SEGMENTED

switches 为

db0 至 db11

DAC

FSADJ

REFIO

1.2v ref

DIV0

PLLLOCK

数字的 数据 输入

0.1

F

R

设置

2k

R

加载

50

DB0

–

DB11

DCOM

pmos 电流

源 排列

AVDD

3.1v 至 3.5v

DVDD

2 -1 mux

端口 1 获得

dac 获得

ACOM

端口 2 获得

DIV1

PLL

电路系统

PLLVDD

CLKVDD

CLK+

CLK

–

CLKCOM

重置

LPF

DB0

–

DB11

V

输出

B R

加载

50

V

输出

一个

V

DIFF

= v

输出

一个

–

V

输出

B

图示 3. simplified 块 图解

涉及 运作

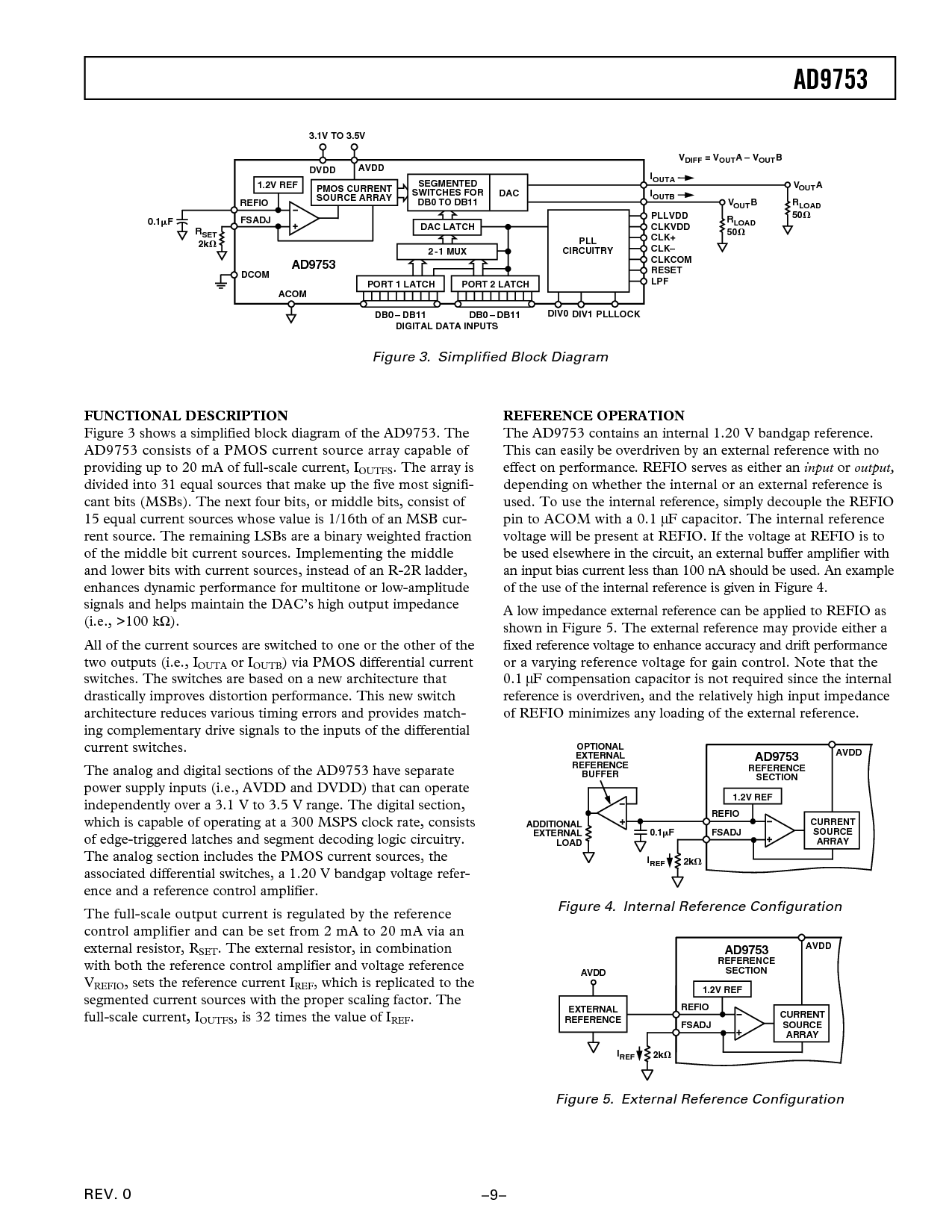

这 ad9753 包含 一个 内部的 1.20 v bandgap 涉及.

这个 能 容易地 是 过载 用 一个 外部 涉及 和 非

效应 在 效能. refio serves 作 也 一个

输入

或者

输出,

取决于 在 whether 这 内部的 或者 一个 外部 涉及 是

使用. 至 使用 这 内部的 涉及, simply 分离 这 refio

管脚 至 acom 和 一个 0.1

µ

f 电容. 这 内部的 涉及

电压 将 是 呈现 在 refio. 如果 这 电压 在 refio 是 至

是 使用 elsewhere 在 这 电路, 一个 外部 缓存区 放大器 和

一个 输入 偏差 电流 较少 比 100 na 应当 是 使用. 一个 例子

的 这 使用 的 这 内部的 涉及 是 给 在 图示 4.

一个 低 阻抗 外部 涉及 能 是 应用 至 refio 作

显示 在 图示 5. 这 外部 涉及 将 提供 也 一个

fixed 涉及 电压 至 增强 精度 和 逐渐变化 效能

或者 一个 varying 涉及 电压 为 增益 控制. 便条 那 这

0.1

µ

f 补偿 电容 是 不 必需的 自从 这 内部的

涉及 是 过载, 和 这 相当地 高 输入 阻抗

的 refio 降低 任何 加载 的 这 外部 涉及.

1.2v ref

AVDD

I

REF

电流

源

排列

REFIO

FSADJ

2k

0.1

F

AD9753

涉及

部分

额外的

外部

加载

OPTIONAL

外部

涉及

缓存区

图示 4. 内部的 涉及 配置

1.2v ref

AVDD

I

REF

电流

源

排列

REFIO

FSADJ

2k

AD9753

涉及

部分

外部

涉及

AVDD

图示 5. 外部 涉及 配置