rev. 0

AD9772

–7–

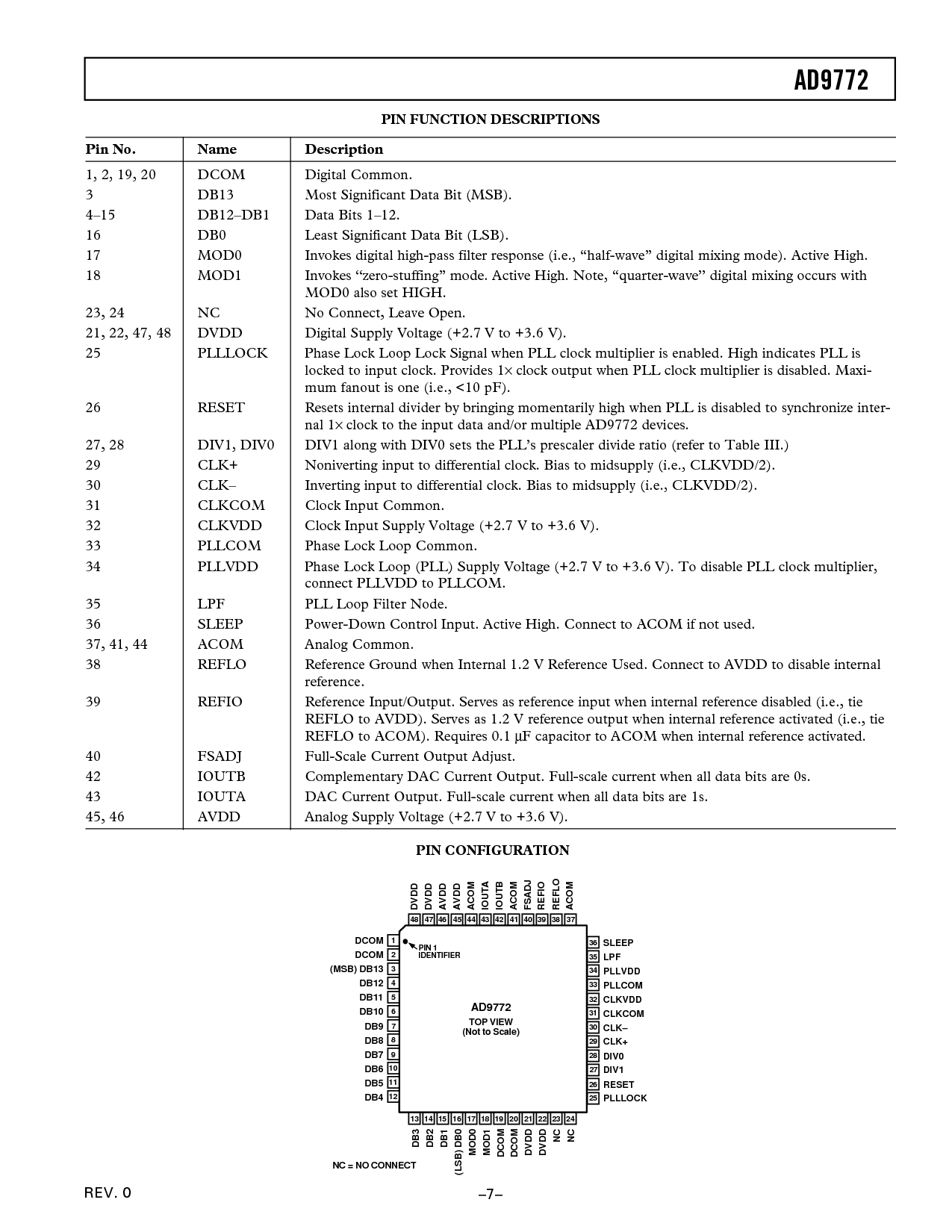

管脚 函数 描述

管脚 非. 名字 描述

1, 2, 19, 20 DCOM 数字的 一般.

3 DB13 大多数 重大的 数据 位 (msb).

4–15 DB12–DB1 数据 位 1–12.

16 DB0 least 重大的 数据 位 (lsb).

17 MOD0 invokes 数字的 高-通过 过滤 回馈 (i.e., “half-wave” 数字的 混合 模式). 起作用的 high.

18 MOD1 invokes “zero-stuffing” 模式. 起作用的 高. 便条, “quarter-wave” 数字的 混合 occurs 和

mod0 也 设置 高.

23, 24 NC 非 连接, leave 打开.

21, 22, 47, 48 DVDD 数字的 供应 电压 (+2.7 v 至 +3.6 v).

25 PLLLOCK 阶段 锁 循环 锁 信号 当 pll 时钟 乘法器 是 使能. 高 indicates pll 是

锁 至 输入 时钟. 提供 1

×

时钟 输出 当 pll 时钟 乘法器 是 无能. maxi-

mum 输出 是 一个 (i.e., <10 pf).

26 重置 resets 内部的 分隔物 用 bringing 短促地 高 当 pll 是 无能 至 同步 inter-

nal 1

×

时钟 至 这 输入 数据 和/或者 多样的 ad9772 设备.

27, 28 div1, div0 div1 along 和 div0 sets 这 pll’s 预分频器 分隔 比率 (谈及 至 表格 iii.)

29 CLK+ noniverting 输入 至 差别的 时钟. 偏差 至 midsupply (i.e., clkvdd/2).

30 CLK– 反相的 输入 至 差别的 时钟. 偏差 至 midsupply (i.e., clkvdd/2).

31 CLKCOM 时钟 输入 一般.

32 CLKVDD 时钟 输入 供应 电压 (+2.7 v 至 +3.6 v).

33 PLLCOM 阶段 锁 循环 一般.

34 PLLVDD 阶段 锁 循环 (pll) 供应 电压 (+2.7 v 至 +3.6 v). 至 使不能运转 pll 时钟 multiplier,

连接 pllvdd 至 pllcom.

35 LPF pll 循环 过滤 node.

36 睡眠 电源-向下 控制 输入. 起作用的 高. 连接 至 acom 如果 不 使用.

37, 41, 44 ACOM 相似物 一般.

38 REFLO 涉及 地面 当 内部的 1.2 v 涉及 使用. 连接 至 avdd 至 使不能运转 内部的

涉及.

39 REFIO 涉及 输入/输出. serves 作 涉及 输入 当 内部的 涉及 无能 (i.e., 系

reflo 至 avdd). serves 作 1.2 v 涉及 输出 当 内部的 涉及 使活动 (i.e., 系

reflo 至 acom). 需要 0.1

µ

f 电容 至 acom 当 内部的 涉及 使活动.

40 FSADJ 全部-规模 电流 输出 调整.

42 IOUTB complementary dac 电流 输出. 全部-规模 电流 当 所有 数据 位 是 0s.

43 IOUTA dac 电流 输出. 全部-规模 电流 当 所有 数据 位 是 1s.

45, 46 AVDD 相似物 供应 电压 (+2.7 v 至 +3.6 v).

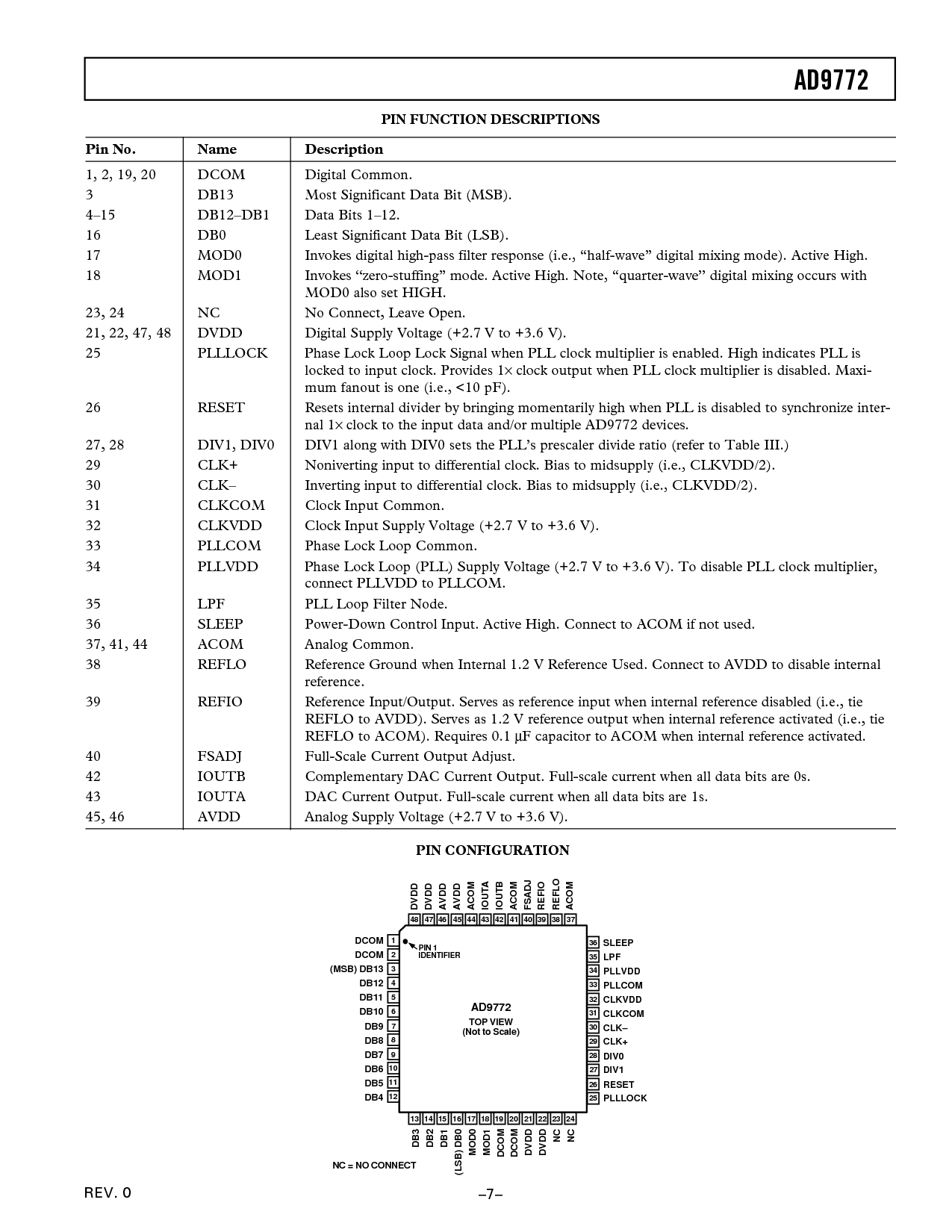

管脚 配置

36

35

34

33

32

31

30

29

28

27

26

25

13 14 15 16 17 18 19 20 21 22 23 24

1

2

3

4

5

6

7

8

9

10

11

12

48 47 46 45 44 39 38 3743 42 41 40

管脚 1

IDENTIFIER

顶 视图

(不 至 规模)

睡眠

LPF

PLLVDD

PLLCOM

CLKVDD

CLKCOM

CLK–

DCOM

DCOM

(msb) db13

DB12

DB11

DB10

DB9

nc = 非 连接

DB8

DB7

DB6

DB5

CLK+

DIV0

DIV1

重置

AD9772

DB4

PLLLOCK

DVDD

DVDD

AVDD

AVDD

ACOM

IOUTA

IOUTB

ACOM

FSADJ

REFIO

REFLO

ACOM

DB3

DB2

DB1

(lsb) db0

MOD0

MOD1

DCOM

DCOM

DVDD

DVDD

NC

NC