rev. 0

AD9752

–12–

在 summary, 这 ad9752 achieves 这 最佳的 扭曲量 和

噪音 效能 下面 这 下列的 情况:

(1) 差别的 运作.

(2) 积极的 电压 摆动 在 iouta 和 ioutb 限制 至

+0.5 v.

(3) I

OUTFS

设置 至 20 毫安.

(4) 相似物 供应 (avdd) 设置 在 5.0 v.

(5) 数字的 供应 (dvdd) 设置 在 3.0 v 至 3.3 v 和 appro-

priate 逻辑 水平.

便条 那 这 交流 效能 的 这 ad9752 是 典型

下面 这 在之上 提到 运行 情况.

数字的 输入

这 ad9752’s 数字的 输入 组成 的 12 数据 输入 管脚 和 一个

时钟 输入 管脚. 这 12-位 并行的 数据 输入 follow 标准

积极的 二进制的 编码 在哪里 db11 是 这 大多数 重大的 位

(msb) 和 db0 是 这 least 重大的 位 (lsb). iouta

生产 一个 全部-规模 输出 电流 当 所有 数据 位 是 在

逻辑 1. ioutb 生产 一个 complementary 输出 和 这

全部-规模 电流 分割 在 这 二 输出 作 一个 函数 的

这 输入 代号.

这 数字的 接口 是 执行 使用 一个 边缘-triggered

主控 从动装置 获得. 这 dac 输出 是 updated 下列的 这

rising 边缘 的 这 时钟 作 显示 在 图示 1 和 是 设计 至

支持 一个 时钟 比率 作 高 作 125 msps. 这 时钟 能 是

运作 在 任何 职责 循环 那 满足 这 指定 获得 脉冲波-

宽度. 这 建制 和 支撑 时间 能 也 是 varied 在里面 这

时钟 循环 作 长 作 这 指定 最小 时间 是 符合;

虽然 这 location 的 这些 转变 edges 将 影响 数字的

feedthrough 和 扭曲量 效能.

最好的 效能 是

典型地 达到 当 这 输入 数据 transitions 在 这 下落 边缘

的 一个 50% 职责 循环 时钟

.

这 数字的 输入 是 cmos 兼容 和 逻辑 门槛,

V

门槛

设置 至 大概 half 这 数字的 积极的 供应

(dvdd) 或者

V

门槛

= dvdd

/2 (

±

20%)

这 内部的 数字的 电路系统 的 这 ad9752 是 有能力 的 operating

在 一个 数字的 供应 范围 的 2.7 v 至 5.5 v. 作 一个 结果, 这

数字的 输入 能 也 accommodate ttl 水平 当 dvdd 是

设置 至 accommodate 这 最大 高 水平的 电压 的 这 ttl

驱动器 v

oh(最大值)

. 一个 dvdd 的 3 v 至 3.3 v 将 典型地 确保

恰当的 兼容性 和 大多数 ttl 逻辑 families. 图示 23

显示 这 相等的 数字的 输入 电路 为 这 数据 和 时钟

输入. 这 睡眠 模式 输入 是 类似的 和 这 例外 那

它 包含 一个 起作用的 拉-向下 电路, 因此 ensuring 那 这

ad9752 仍然是 使能 如果 这个 输入 是 left disconnected.

DVDD

数字的

输入

图示 23. 相等的 数字的 输入

自从 这 ad9752 是 有能力 的 正在 updated 向上 至 125 msps,

这 质量 的 这 时钟 和 数据 输入 信号 是 重要的 在

实现 这 最佳的 效能. 这 驱动器 的 这 数字的

数据 接口 电路系统 应当 是 指定 至 满足 这 迷你-

mum 建制 和 支撑 时间 的 这 ad9752 作 好 作 它的 re-

quired 最小值/最大值 输入 逻辑 水平的 门槛. 典型地, 这

选择 的 这 slowest 逻辑 家族 那 satisfies 这 在之上 con-

ditions 将 结果 在 这 最低 数据 feedthrough 和 噪音.

数字的 信号 paths 应当 是 保持 短的 和 run 长度

matched 至避免 传播 延迟 mismatch. 这 嵌入 的

一个 低 值 电阻 网络 (i.e., 20

Ω

至 100

Ω

) 在 这

ad9752 数字的 输入 和 驱动器 输出 将 是 helpful 在 reduc-

ing 任何 overshooting 和 ringing 在 这 数字的 输入 那 con-

tribute 至 数据 feedthrough. 为 变长 run 长度 和 高 数据

更新 比率, strip 线条 技巧 和 恰当的 末端 resis-

tors 应当 是 考虑 至 维持 “clean” 数字的 输入. 也,

运行 这 ad9752 和 减少 逻辑 swings 和 一个 corre-

sponding 数字的 供应 (dvdd) 将 也 减少 数据 feedthrough.

这 外部 时钟 驱动器 电路系统 应当 提供 这 ad9752

和 一个 低 jitter 时钟 输入 meeting 这 最小值/最大值 逻辑 水平

当 供应 快 edges. 快 时钟 edges 将 帮助 降低

任何 jitter 那 将 manifest 它自己 作 阶段 噪音 在 一个 recon-

structed 波形. 因此, 这 时钟 输入 应当 是 驱动 用

这 fastest 逻辑 家族 合适的 为 这 应用.

便条, 这 时钟 输入 可以 也 是 驱动 通过 一个 sine 波, 这个 是

集中 周围 这数字的 门槛 (i.e., dvdd/2), 和 满足

这 最小值/最大值 逻辑 门槛. 这个 将 典型地 结果 在 一个 slight

降级 在 这 阶段 噪音, 这个 变为 更多 noticeable

在 高等级的 抽样 比率 和 输出 发生率. 也, 在 高等级的

抽样 比率, 这 20% 容忍 的 这 数字的 逻辑 门槛

应当 是 考虑 自从 它 将 影响 这 有效的 时钟 职责

循环 和 subsequently 截 在 这 必需的 数据 建制 和

支撑 时间.

输入 时钟/数据 定时 relationship

snr 在 一个 dac 是 依赖 在 这 relationship 在 这

位置 的 这 时钟 edges 和 这 要点 在 时间 在 这个 这

输入 数据 改变. 这 ad9752 是 积极的 边缘 triggered, 和

所以 exhibits snr 敏锐的 当 这 数据 转变 是 关闭 至

这个 边缘. 在 一般, 这 goal 当 应用 这 ad9752 是 至

制造 这 数据 transitions shortly 之后 这 积极的 时钟 边缘.

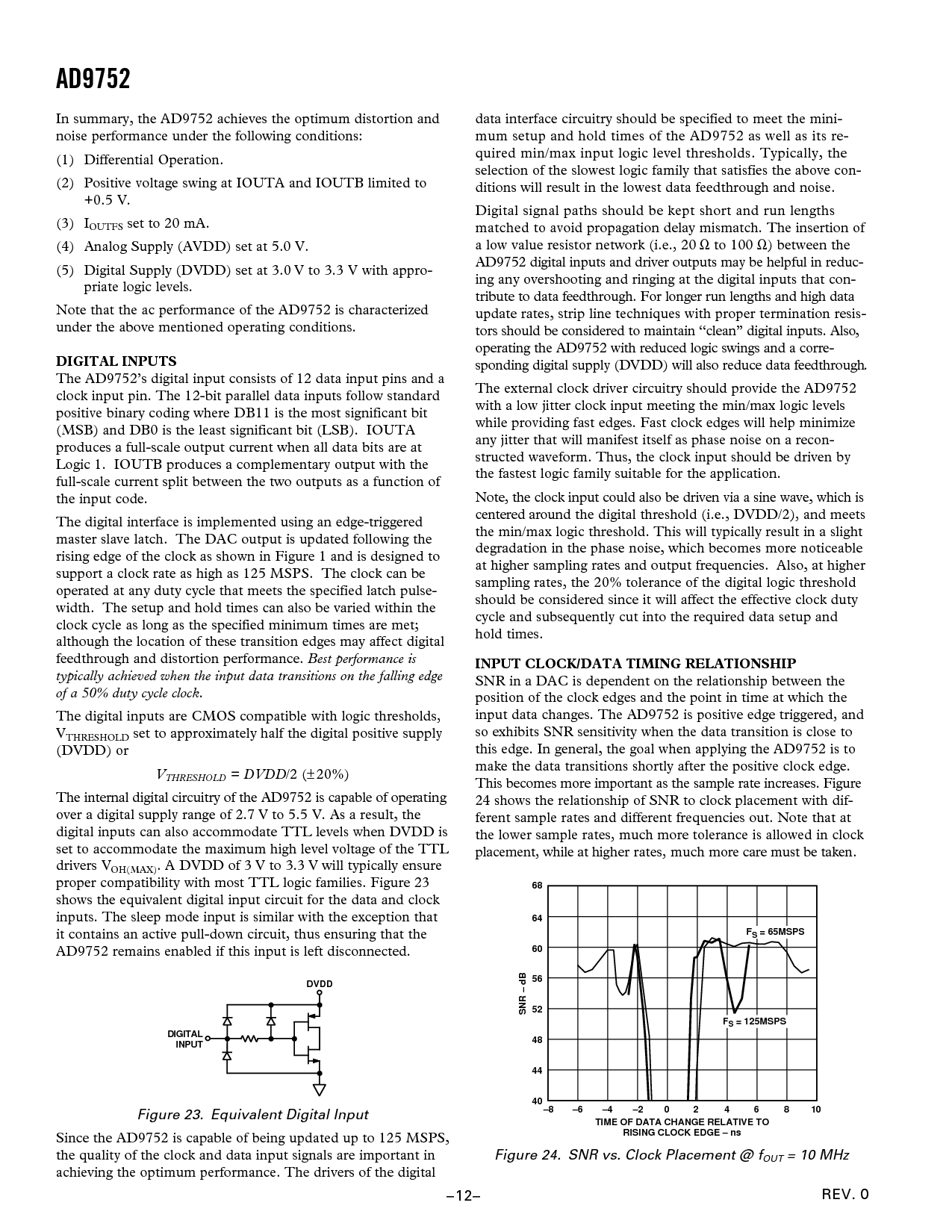

这个 变为 更多 重要的 作 这 样本 比率 增加. 图示

24 显示 这 relationship 的 snr 至 时钟 placement 和 dif-

ferent 样本 比率 和 不同的 发生率 输出. 便条 那 在

这 更小的 样本 比率, 更 更多 容忍 是 允许 在 时钟

placement, 当 在 higher 比率, 更更多 小心 必须 是 带去.

时间 的 数据 改变 相关的 至

rising 时钟 边缘 – ns

68

40

–8 10–6 –4 –2 0 2 4 6 8

64

60

56

52

48

snr – db

44

F

S

= 65msps

F

S

= 125msps

图示 24. snr vs. 时钟 placement @ f

输出

= 10 mhz