AD9859

rev. 0 | 页 7 的 24

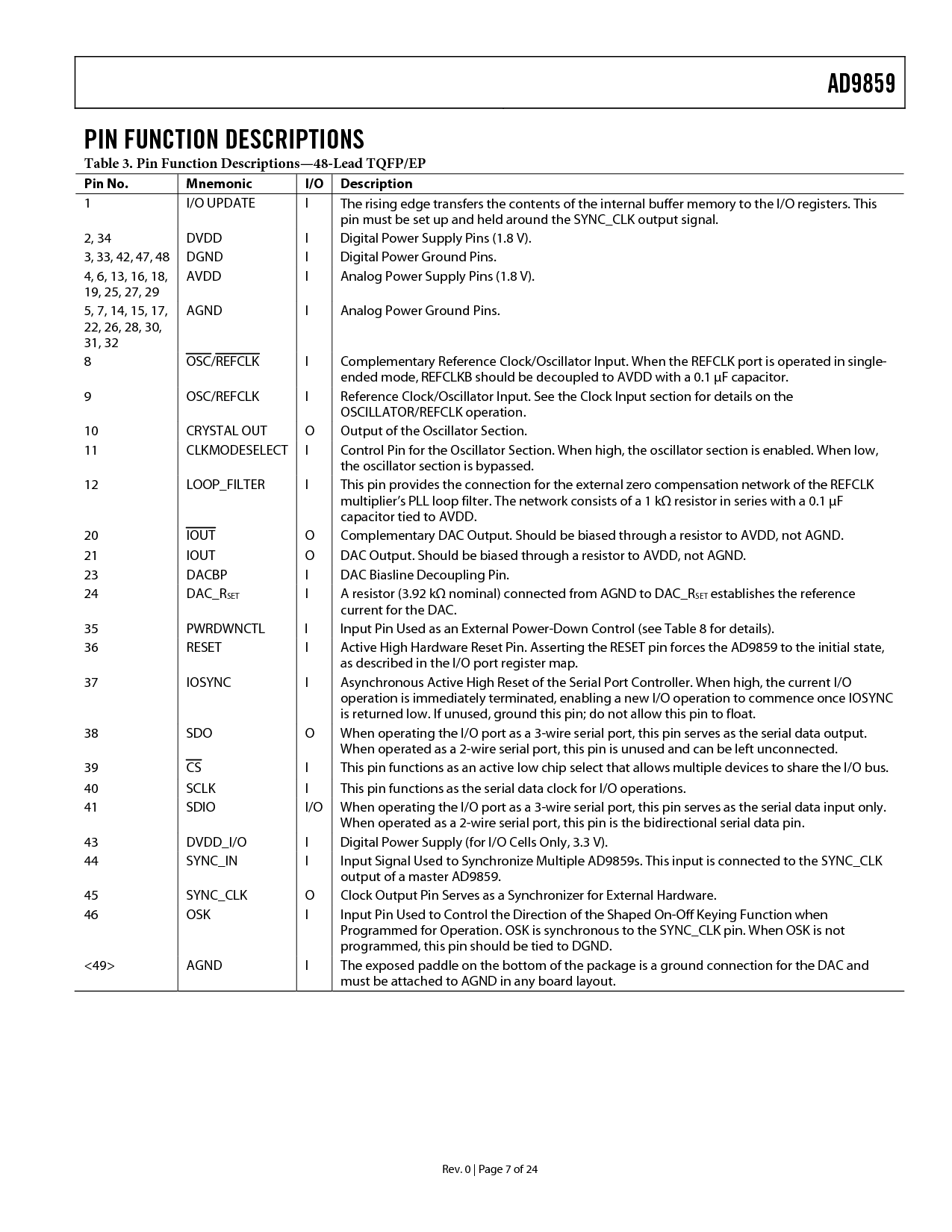

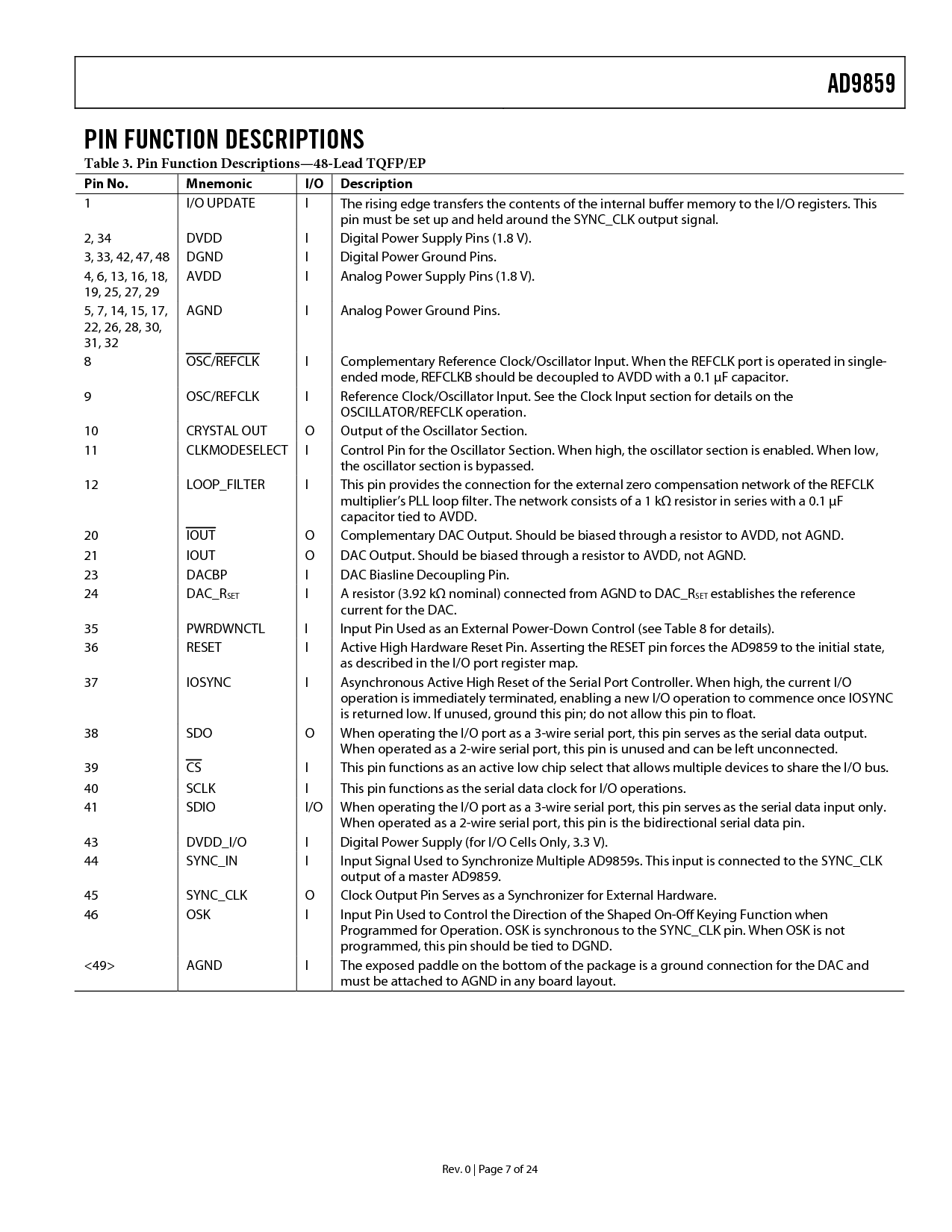

管脚 函数 描述

表格 3. 管脚 函数 descriptions—48-含铅的 tqfp/ep

管脚 非. Mnemonic i/o 描述

1 i/o 更新 i

这 rising 边缘 transfers 这 内容 的 这 内部的 缓存区 记忆 至 这 i/o 寄存器. 这个

管脚 必须 是 设置 向上 和 使保持 around 这 同步_clk 输出 信号.

2, 34 DVDD I 数字的 电源 供应 管脚 (1.8 v).

3, 33, 42, 47, 48 DGND I 数字的 电源 地面 管脚.

4, 6, 13, 16, 18,

19, 25, 27, 29

AVDD I 相似物 电源 供应 管脚 (1.8 v).

5, 7, 14, 15, 17,

22, 26, 28, 30,

31, 32

AGND I 相似物 电源 地面 管脚.

8

OSC

/refclk

I

complementary 涉及 时钟/振荡器 输入.当 这 refclk 端口 是 运作 在 单独的-

结束 模式, refclkb 应当 是 decoupled 至 avdd 和 一个 0.1 µf 电容.

9 osc/refclk i

涉及 时钟/振荡器 输入. 看 the 时钟 输入 部分 为 详细信息 在 这

振荡器/refclk 运作.

10 结晶 输出 O 输出 的 这 振荡器 部分.

11 clkmodeselect i

控制 管脚 为 这 振荡器 部分. 当 高,这 振荡器 部分 是 使能. 当 低,

这 振荡器 部分 是 绕过.

12 循环_过滤 i

这个 管脚 提供 这 连接 为 这 external 零 补偿 网络 的 这 refclk

乘法器’s pll 循环 过滤. 这 网络 组成的 一个 1 kΩ 电阻 在 序列 和 一个 0.1 µf

电容 系 至 avdd.

20

IOUT

O complementary dac 输出. 应当 是 偏差ed 通过 一个 电阻 至 avdd, 不 agnd.

21 IOUT O dac 输出. 应当 是 片面的通过 一个 电阻 至 avdd, 不 agnd.

23 DACBP I dac biasline 解耦 管脚.

24 dac_r

设置

I

一个 电阻 (3.92 kΩ 名义上的) 连接 从 agnd 至 dac_r

设置

establishes 这 涉及

电流 为 这 dac.

35 PWRDWNCTL I 输入 管脚 使用 作一个 外部 电源-向下 内容rol (看 表格 8 为 详细信息).

36 重置 i

起作用的 高 硬件 重置 管脚. asserting 这 re设置 管脚 forces 这 ad9859 至 这 最初的 状态,

作 描述 在 这 i/o 端口 寄存器 编排.

37 iosync i

异步的 起作用的 高 重置的 这 串行 端口 控制. 当 高, 这 电流 i/o

运作 是 立即 terminated, enabling一个 新 i/o 运作 至 commence once iosync

是 returned 低. 如果 unused, 地面 这个管脚; 做 不 准许 这个 管脚 至 float.

38 sdo O

当 运行 这 i/o 端口 作 一个 3-线 串行 port, 这个 管脚 serves 作这 串行 数据 输出.

当 运作 作 一个 2-线 串行 端口, 这个管脚 是 unused 和 能 是 left unconnected.

39

CS

I 这个 管脚 功能 作 一个 起作用的 低 碎片 选择那 准许 多样的 设备 至 share 这 i/o 总线.

40 SCLK I 这个 管脚 功能 作 这 串行 数据 时钟 为 i/o 行动.

41 sdioi/o

当 运行 这 i/o 端口 作 一个 3-线 串行 端口, 这个 管脚 serves 作 这串行 数据 输入 仅有的.

当 运作 作 一个 2-线 串行 端口, 这个 管脚 是 这 双向的 串行 数据 管脚.

43 dvdd_i/o I 数字的 电源 供应 (为 i/o cells 仅有的, 3.3 v).

44 同步_在 i

输入 信号 使用 至 同步 多样的 ad9859s. 这个 输入 是 连接 至 这 同步_clk

输出 的 一个 主控 ad9859.

45 同步_clk O 时钟 输出 管脚 serves 作一个 synchronizer 为 外部 硬件.

46 osk I

输入 管脚 使用 至 控制 这 方向 的这 shaped 在-止 keying 函数 当

编写程序 为 运作. osk 是 同步的 至 这 同步_clk 管脚. 当 osk 是 不

编写程序, 这个 管脚 应当 是 系 至 dgnd.

<49> agnd I

这 exposed paddle 在 这 bottom 的 这 包装age 是 一个 地面 连接 为 这 dac 和

必须 是 连结 至 agnd 在 任何 板 布局.