sbas279c −8月 2003 − 修订 october 2004

www.德州仪器.com

7

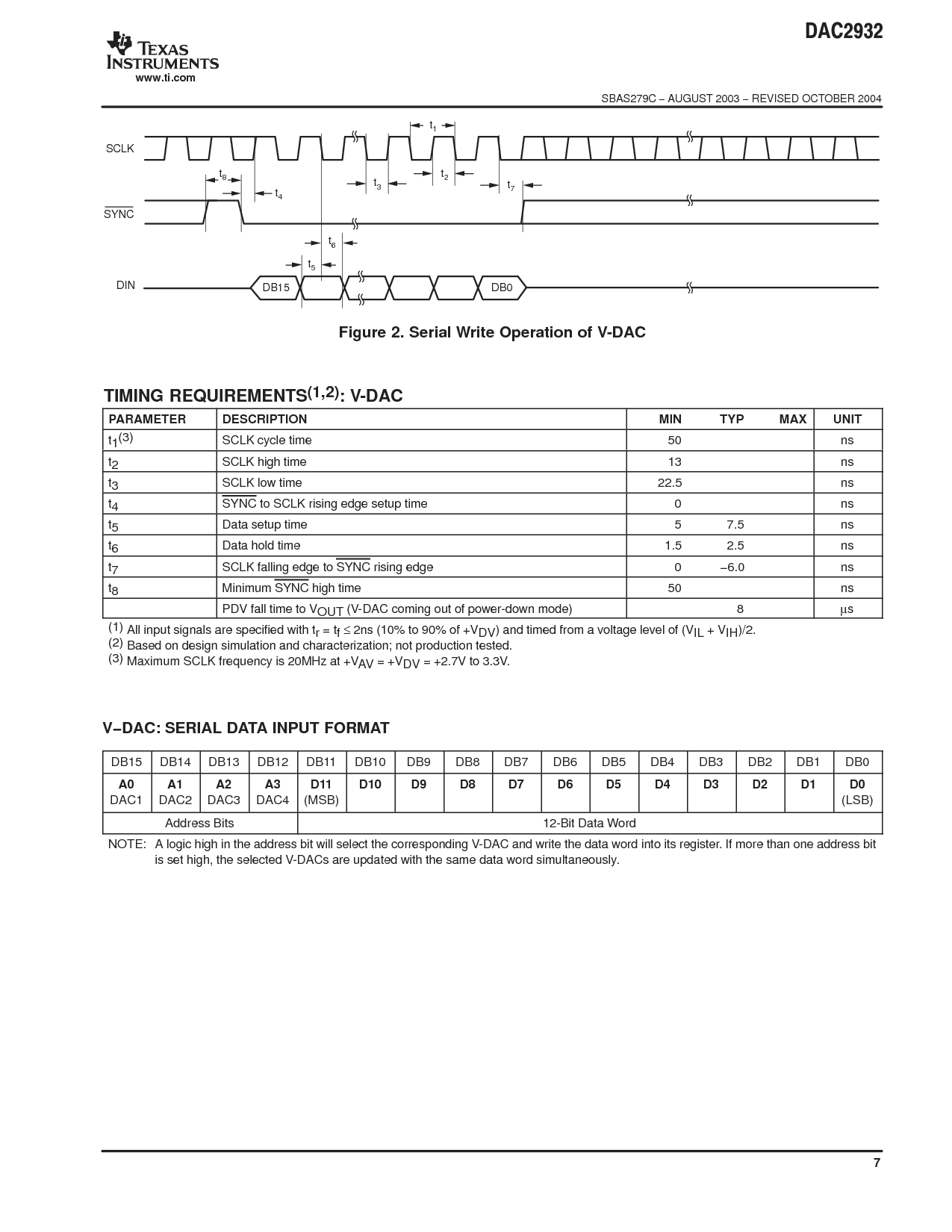

SCLK

DB15 DB0

同步

DIN

t

1

t

2

t

7

t

3

t

4

t

8

t

5

t

6

图示 2. 串行 写 运作 的 v-dac

定时 (所需的)东西

(1,2)

: v-dac

参数 描述 最小值 典型值 最大值 单位

t

1

(3)

sclk 循环 时间 50 ns

t

2

sclk 高 时间 13 ns

t

3

sclk 低 时间 22.5 ns

t

4

同步至 sclk rising 边缘 建制 时间 0 ns

t

5

数据 建制 时间 5 7.5 ns

t

6

数据 支撑 时间 1.5 2.5 ns

t

7

sclk 下落 边缘 至 同步rising 边缘 0 −6.0 ns

t

8

最小 同步高 时间 50 ns

pdv 下降 时间 至 v

输出

(v-dac coming 输出 的 电源-向下 模式) 8

µ

s

(1)

所有 输入 信号 是 指定 和 t

r

= t

f

≤

2ns (10% 至 90% 的 +v

DV

) 和 安排时间 从 一个 电压 水平的 的 (v

IL

+ v

IH

)/2.

(2)

为基础 在 设计 simulation 和 描绘; 不 生产 测试.

(3)

最大 sclk 频率 是 20mhz 在 +v

AV

= +v

DV

= +2.7v 至 3.3v.

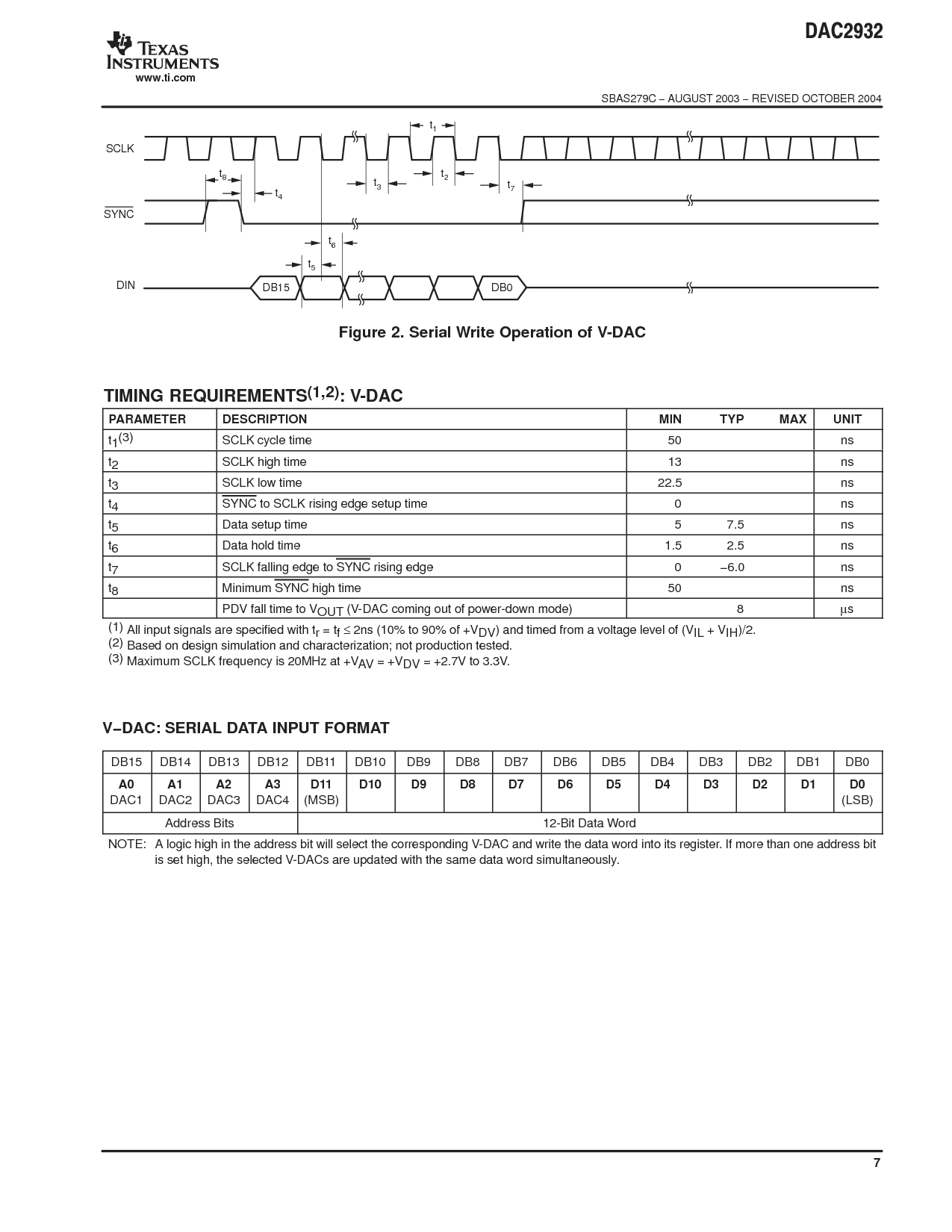

v−dac: 串行 数据 输入 format

DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

A0

DAC1

A1

DAC2

A2

DAC3

A3

DAC4

D11

(msb)

D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

(lsb)

地址 位 12-位 数据 文字

便条: 一个逻辑 高 在 这 地址 位 将 选择 这 相应的 v-dac 和 写 这 数据 文字 在 它的 寄存器. 如果 更多 比 一个 一个ddress 位

是 设置 高, 这 选择 v-dacs 是 updated 和 这 一样 数据 文字 同时发生地.