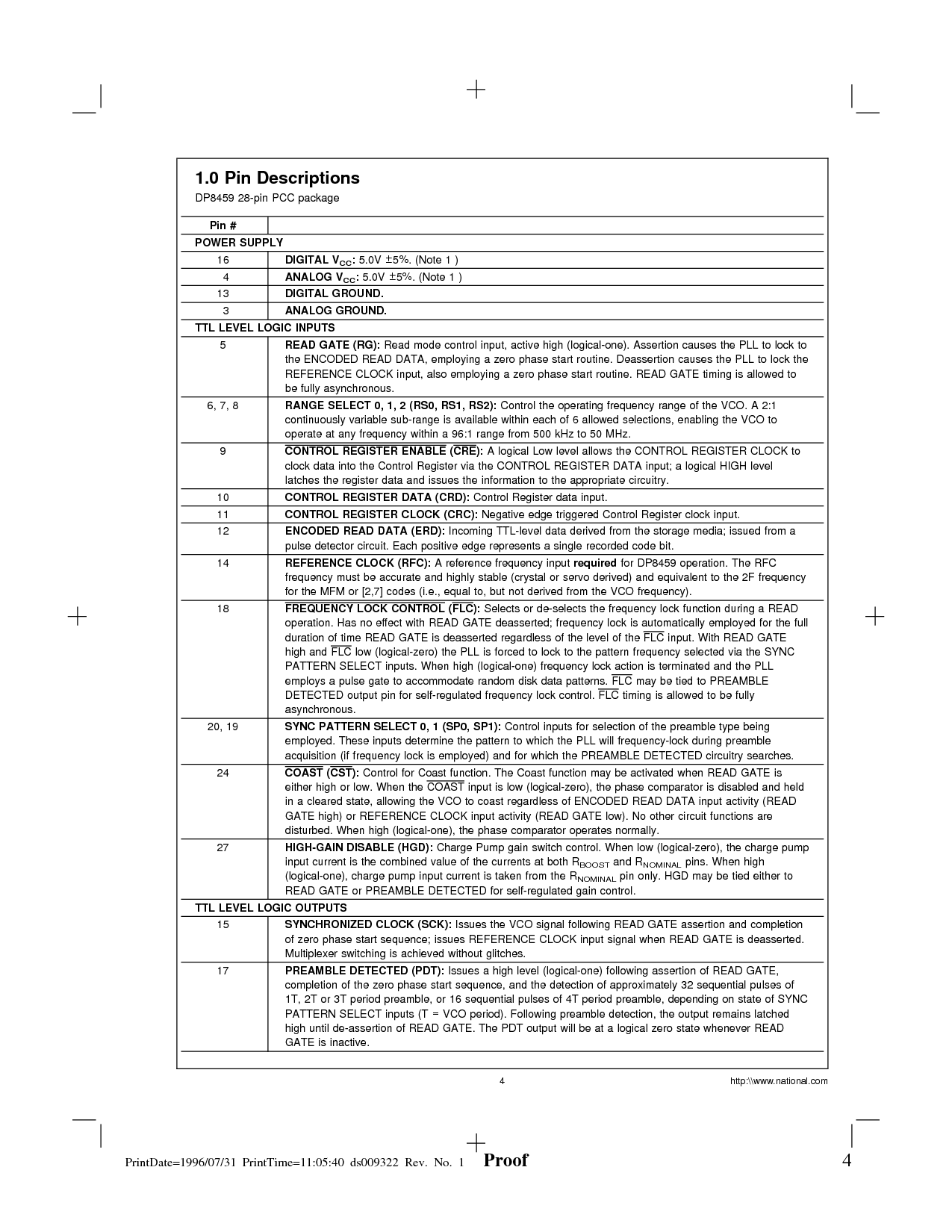

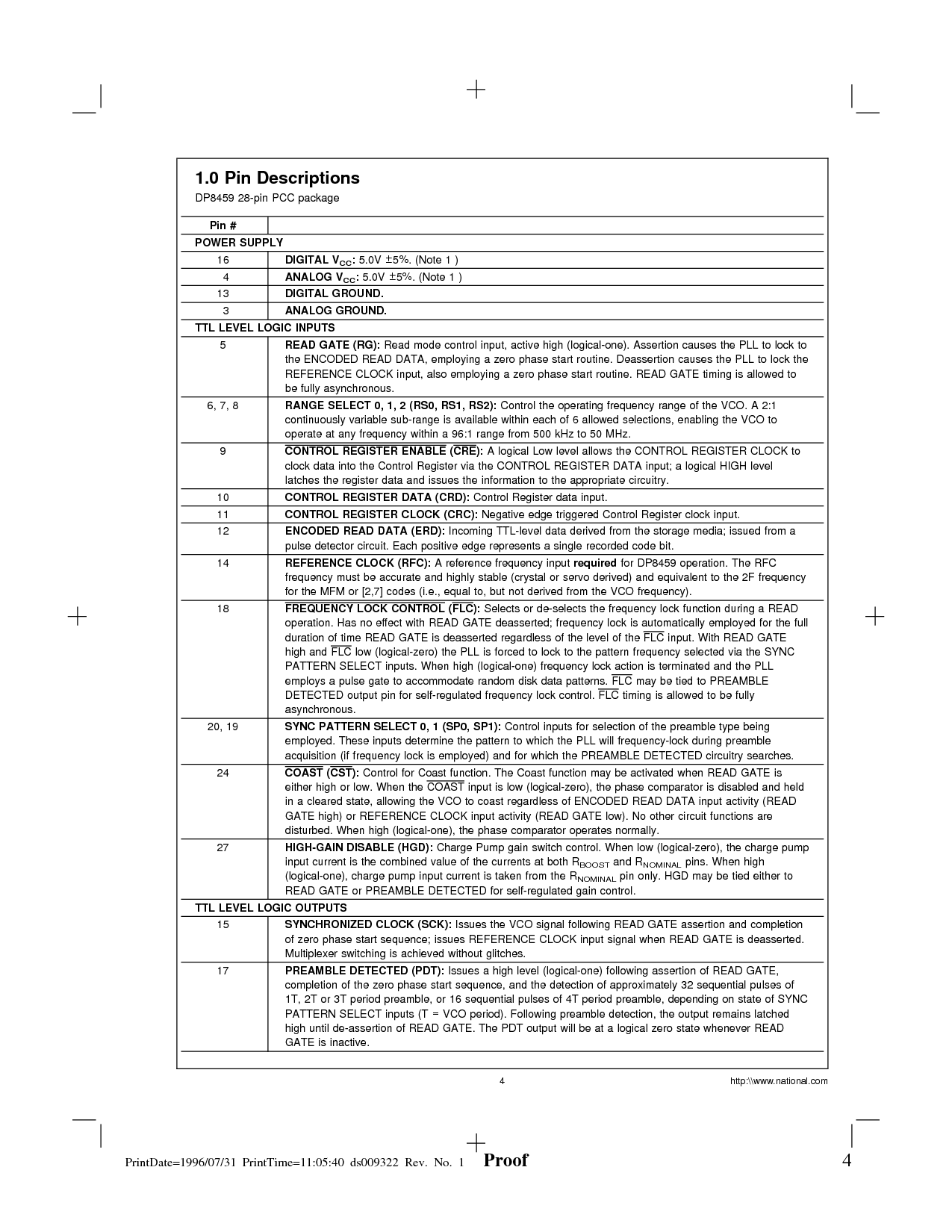

1.0 管脚 描述

DP8459 28-管脚 PCC 包装

管脚

#

电源 供应

16

数字的 V

CC

:

5.0v

±

5

%

. (便条 1 )

4

相似物 V

CC

:

5.0v

±

5

%

. (便条 1 )

13

数字的 地面.

3

相似物 地面.

TTL 水平的 逻辑 输入

5

读 门 (rg):

读 模式 控制 输入, 起作用的 高 (logical-一个). Assertion 导致 这 PLL 至 锁 至

这 ENCODED 读 数据, employing 一个 零 阶段 开始 routine. Deassertion 导致 这 PLL 至 锁 这

涉及 时钟 输入, 也 employing 一个 零 阶段 开始 routine. 读 门 定时 是 允许 至

是 全部地 异步的.

6, 7, 8

范围 选择 0, 1, 2 (rs0, rs1, rs2):

控制 这 运行 频率 范围 的 这 vco. 一个 2:1

continuously 能变的 sub-范围 是 有 在里面 各自 的 6 允许 selections, enabling 这 VCO 至

运作 在 任何 频率 在里面 一个 96:1 范围 从 500 kHz 至 50 mhz.

9

控制 寄存器 使能 (cre):

一个 logical 低 水平的 准许 这 控制 寄存器 时钟 至

时钟 数据 在 这 控制 寄存器 通过 这 控制 寄存器 数据 输入; 一个 logical 高 水平的

latches 这 寄存器 数据 和 issues 这 信息 至 这 适合的 电路系统.

10

控制 寄存器 数据 (crd):

控制 寄存器 数据 输入.

11

控制 寄存器 时钟 (crc):

负的 边缘 triggered 控制 寄存器 时钟 输入.

12

ENCODED 读 数据 (erd):

新当选的 ttl-水平的 数据 获得 从 这 存储 媒介; issued 从 一个

脉冲波 探测器 电路. 各自 积极的 边缘 代表 一个 单独的 recorded 代号 位.

14

涉及 时钟 (rfc):

一个 涉及 频率 输入

必需的

为 DP8459 运作. 这 RFC

频率 必须 是 精确 和 高级地 稳固的 (结晶 或者 伺服 获得) 和 相等的 至 这 2F 频率

为 这 MFM 或者 [2,7] 代号 (i.e., equal 至, 但是 不 获得 从 这 VCO 频率).

18

频率 锁 控制 (flc):

选择 或者 de-选择 这 频率 锁 函数 在 一个 读

运作. 有 非 效应 和 读 门 deasserted; 频率 锁 是 automatically 运用 为 这 全部

持续时间 的 时间 读 门 是 deasserted regardless 的 这 水平的 的 这 FLC 输入. 和 读 门

高 和 FLC 低 (logical-零) 这 PLL 是 强迫 至 锁 至 这 模式 频率 选择 通过 这 同步

模式 选择 输入. 当 高 (logical-一个) 频率 锁 action 是 terminated 和 这 PLL

雇用 一个 脉冲波 门 至 accommodate 随机的 disk 数据 patterns. FLC 将 是 系 至 PREAMBLE

发现 输出 管脚 为 自-管制 频率 锁 控制. FLC 定时 是 允许 至 是 全部地

异步的.

20, 19

同步 模式 选择 0, 1 (sp0, sp1):

控制 输入 为 选择 的 这 preamble 类型 正在

运用. 这些 输入 决定 这 模式 至 这个 这 PLL 将 频率-锁 在 preamble

acquisition (如果 频率 锁 是 运用) 和 为 这个 这 PREAMBLE 发现 电路系统 searches.

24

COAST (cst):

控制 为 Coast 函数. 这 Coast 函数 将 是 使活动 当 读 门 是

也 高 或者 低. 当 这 COAST 输入 是 低 (logical-零), 这 阶段 比较器 是 无能 和 使保持

在 一个 cleared 状态, 准许 这 VCO 至 coast regardless 的 ENCODED 读 数据 输入 activity (读

门 高) 或者 涉及 时钟 输入 activity (读 门 低). 非 其它 电路 功能 是

disturbed. 当 高 (logical-一个), 这 阶段 比较器 运作 正常情况下.

27

高-增益 使不能运转 (hgd):

承担 打气 增益 转变 控制. 当 低 (logical-零), 这 承担 打气

输入 电流 是 这 联合的 值 的 这 电流 在 两个都 R

BOOST

和 R

名义上的

管脚. 当 高

(logical-一个), 承担 打气 输入 电流 是 带去 从 这 R

名义上的

管脚 仅有的. HGD 将 是 系 也 至

读 门 或者 PREAMBLE 发现 为 自-管制 增益 控制.

TTL 水平的 逻辑 输出

15

同步 时钟 (sck):

Issues 这 VCO 信号 下列的 读 门 assertion 和 completion

的 零 阶段 开始 sequence; issues 涉及 时钟 输入 信号 当 读 门 是 deasserted.

多路调制器 切换 是 达到 没有 glitches.

17

PREAMBLE 发现 (pdt):

Issues 一个 高 水平的 (logical-一个) 下列的 assertion 的 读 门,

completion 的 这 零 阶段 开始 sequence, 和 这 发现 的 大概 32 sequential 脉冲 的

1t, 2T 或者 3T 时期 preamble, 或者 16 sequential 脉冲 的 4T 时期 preamble, 取决于 在 状态 的 同步

模式 选择 输入 (t

=

VCO 时期). 下列的 preamble 发现, 这 输出 仍然是 latched

高 直到 de-assertion 的 读 门. 这 PDT 输出 将 是 在 一个 logical 零 状态 whenever 读

门 是 inactive.

打印日期=1996/07/31 打印时间=11:05:40 ds009322 rev. 非. 1

Proof

4

4 http:\\www.国家的.com