rev. 一个 日期:12/11/03 sp3222eb/3232eb 真实 +3.0 至 +5.5v rs-232 transceivers © 版权 2003 sipex 公司

10

接受者

这 接受者 转变 eia/tia-232 水平 至

ttl 或者 cmos 逻辑 输出 水平. 这

sp3222eb 接受者 有 一个 反相的 触发-状态

输出. 这些 接受者 输出 (rxout) 是 触发-

陈述 当 这 使能 控制 en = 高. 在

这 关闭 模式, 这 接受者 能 是 起作用的

或者 inactive. en 有 非 效应 在 txout. 这

真实 表格 逻辑 的 这

SP3222EB

驱动器 和

接受者 输出 能 是 建立 在

表格 2

.

自从 接受者 输入 是 通常地 从 一个 transmis-

sion 线条 在哪里 长 缆索 长度 和 系统

干扰 能 降级 这 信号, 这 输入

有 一个 典型 hysteresis 余裕 的 300mv. 这个

确保 那 这 接受者 是 virtually 不受影响 至

嘈杂的 传递 线条. 应当 一个 输入 是 left

unconnected, 一个 5k

Ω

pulldown 电阻 至 地面

将 commit 这 输出 的 这 接受者 至 一个 高

状态.

承担 打气

这 承担 打气 是 一个

Sipex

–patented 设计

(5,306,954) 和 使用 一个 唯一的 approach com-

pared 至 older less–efficient 设计. 这 承担

打气 安静的 需要 四 外部 电容, 但是

使用 一个 four–phase 电压 shifting 技巧 至

attain 对称的 5.5v 电源 供应. 这

内部的 电源 供应 组成 的 一个 管制

双 承担 打气 那 提供 输出 电压

5.5v regardless 的 这 输入 电压 (v

CC

) 在

这 +3.0v 至 +5.5v 范围.

在 大多数 circumstances, 解耦 这 电源

供应 能 是 达到 adequately 使用 一个 0.1

µ

F

绕过 电容 在 c5 (谈及 至

计算数量 8

和

9

).

在 产品 那 是 敏感的 至 电源-sup-

ply 噪音, 分离 v

CC

至 地面 和 一个 capaci-

tor 的 这 一样 值 作 承担-打气 电容

c1. physically 连接 绕过 电容 作

关闭 至 这 ic 作 可能.

这 承担 pumps 运作 在 一个 discontinuous

模式 使用 一个 内部的 振荡器. 如果 这 输出

电压 是 较少 比 一个 巨大 的 5.5v, 这

承担 pumps 是 使能. 如果 这 输出 电压

超过 一个 巨大 的 5.5v, 这 承担 pumps

是 无能. 这个 振荡器 控制 这 四

阶段 的 这 电压 shifting. 一个 描述 的

各自 阶段 跟随.

阶段 1

— v

SS

承担 存储 — 在 这个 阶段 的

这 时钟 循环, 这 积极的 一侧 的 电容

C

1

和 c

2

是 initially charged 至 v

CC

. c

l

+

是

然后 切换 至 地 和 这 承担 在 c

1

–

是

transferred 至 c

2

–

. 自从 c

2

+

是 连接 至

V

CC

, 这 电压 潜在的 横过 电容 c

2

是 now 2 时间 v

CC

.

阶段 2

— v

SS

转移 — 阶段 二 的 这 时钟 con-

nects 这 负的 终端 的 c

2

至 这 v

SS

存储 电容 和 这 积极的 终端 的 c

2

至 地. 这个 transfers 一个 负的 发生

电压 至 c

3

. 这个 发生 电压 是 regu-

lated 至 一个 最小 电压 的 -5.5v. simulta-

neous 和 这 转移 的 这 电压 至 c

3

, 这

积极的 一侧 的 电容 c

1

是 切换 至 v

CC

和 这 负的 一侧 是 连接 至 地.

阶段 3

— v

DD

承担 存储 — 这 第三 阶段 的 这

时钟 是 完全同样的 至 这 第一 阶段 — 这 承担

transferred 在 c

1

生产 –v

CC

在 这 负的

终端 的 c

1

, 这个 是 应用 至 这 负的

一侧 的 电容 c

2

. 自从 c

2

+

是 在 v

CC

, 这

电压 潜在的 横过 c

2

是 2 时间 v

CC

.

阶段 4

— v

DD

转移 — 这 fourth 阶段 的 这 时钟

connects 这 负的 终端 的 c

2

至 地,

和 transfers 这个 积极的 发生 电压

横过 c

2

至 c

4

, 这 v

DD

存储 电容.

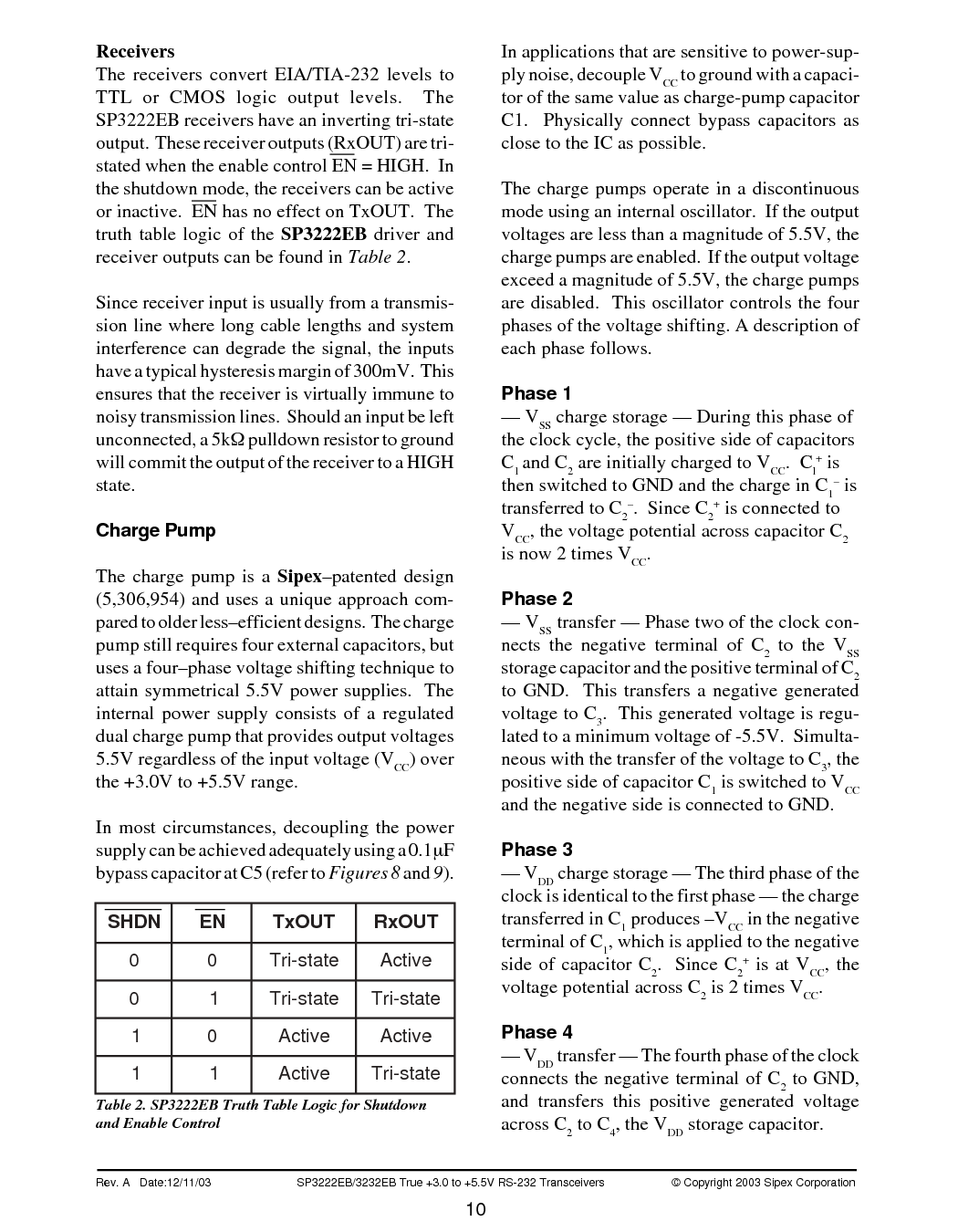

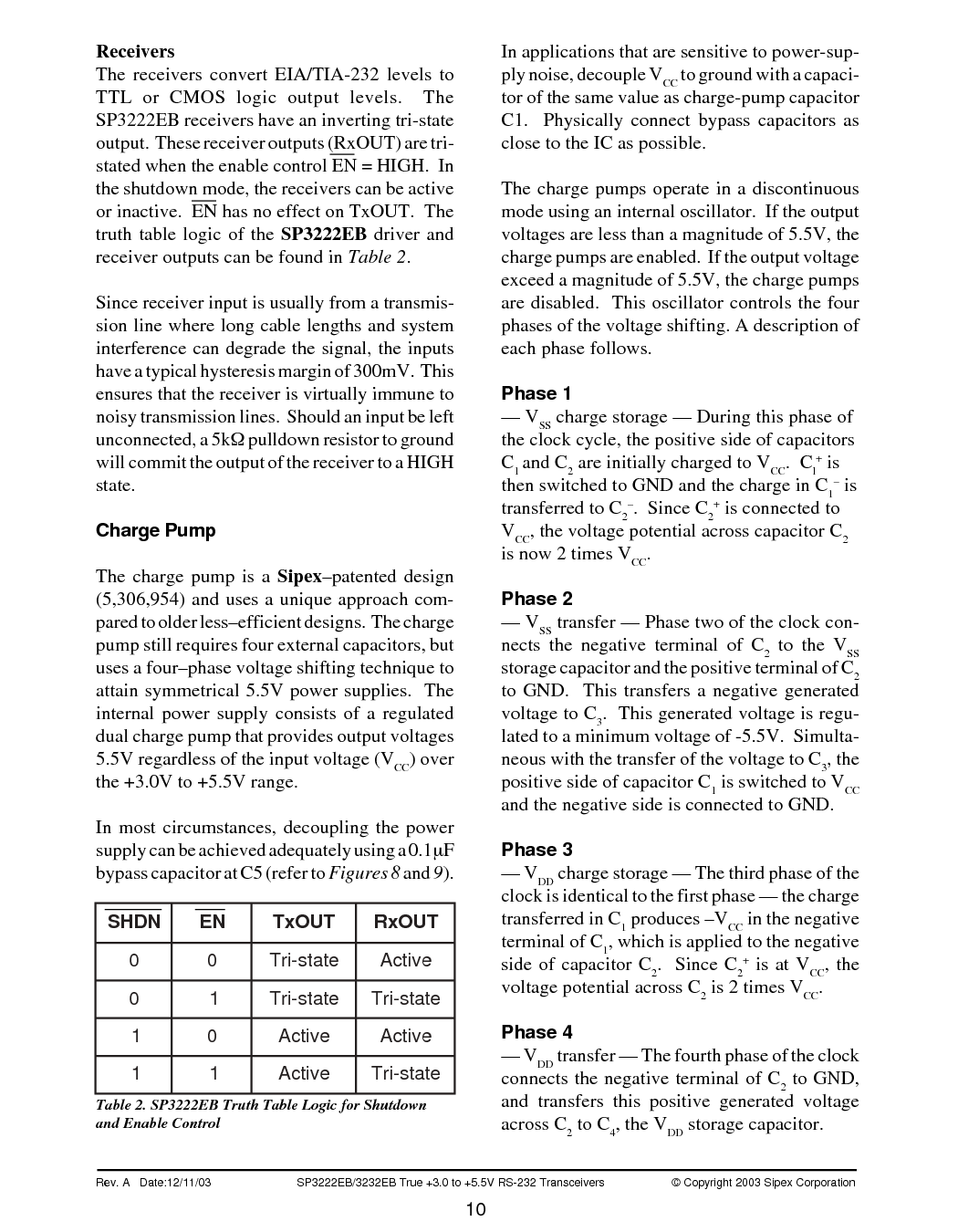

表格 2. sp3222eb 真实 表格 逻辑 为 关闭

和 使能 控制

NDHSNETUOxTTUOxR

00 etats-irTevitcA

01 etats-irTetats-irt

10 evitcAevitcA

11 evitcAetats-irt