FM25L16

rev. 2.0

三月. 2005 页 2 的 14

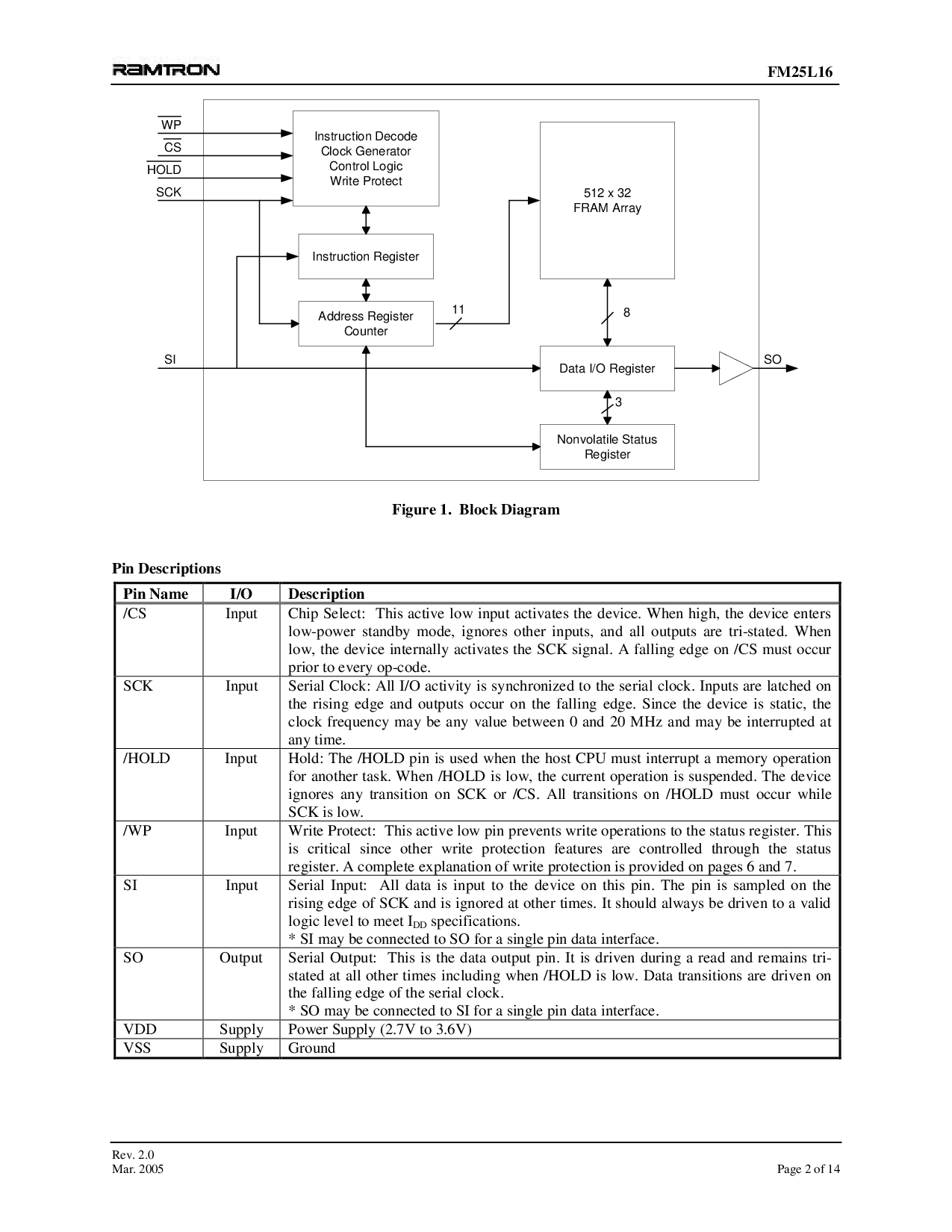

操作指南 decode

时钟 发生器

控制 逻辑

写 保护

操作指南 寄存器

地址 寄存器

计数器

512 x 32

fram 排列

11

数据 i/o 寄存器

8

nonvolatile 状态

寄存器

3

WP

CS

支撑

SCK

所以SI

图示 1. 块 图解

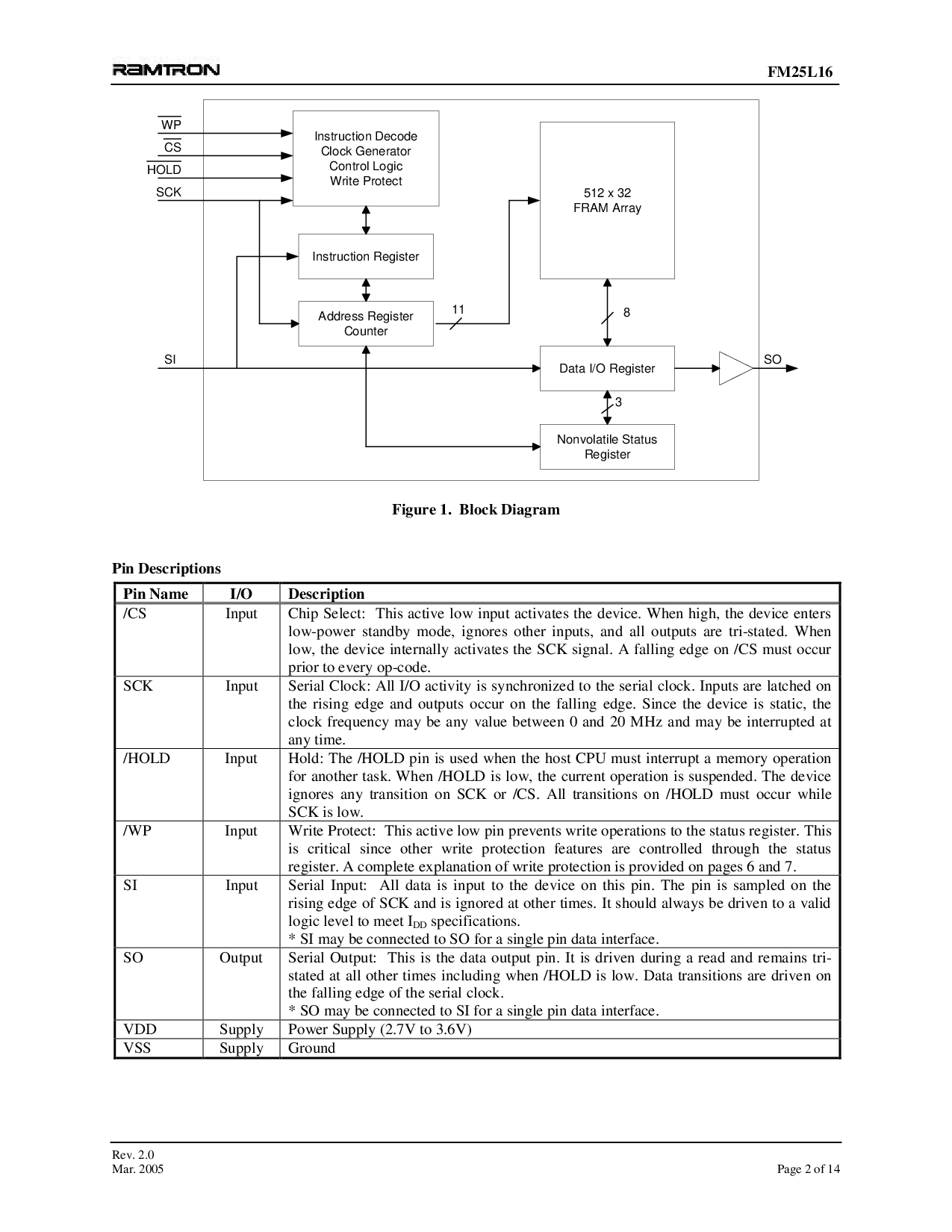

管脚 描述

管脚 名字 i/o 描述

/cs 输入 碎片 选择: 这个 起作用的 低 输入 activates 这 设备. 当 高, 这 设备 enters

低-电源 备用物品 模式, ignores 其它 输入, 和 所有 输出 是 触发-陈述. 当

低, 这 设备 内部 activates 这 sck 信号. 一个 下落 边缘 在 /cs 必须 出现

较早的 至 每 运算-代号.

SCK 输入 串行 时钟: 所有 i/o activity 是 同步 至 这 串行 时钟. 输入 是 latched 在

这 rising 边缘 和 输出 出现 在 这 下落 边缘. 自从 这 设备 是 静态的, 这

时钟 频率 将 是 任何 值 在 0 和 20 mhz 和 将 是 interrupted 在

任何 时间.

/支撑 输入 支撑: 这 /支撑 管脚 是 使用 当 这 host cpu 必须 中断 一个 记忆 运作

为 另一 task. 当 /支撑 是 低, 这 电流 运作 是 suspended. 这 设备

ignores 任何 转变 在 sck 或者 /cs. 所有 transitions 在 /支撑 必须 出现 当

sck 是 低.

/wp 输入 写 保护: 这个 起作用的 低 管脚 阻止 写 行动 至 这 状态 寄存器. 这个

是 核心的 自从 其它 写 保护 特性 是 控制 通过 这 状态

寄存器. 一个 完全 explanation 的 写 保护 是 提供 在 页 6 和 7.

SI 输入 串行 输入: 所有 数据 是 输入 至 这 设备 在 这个 管脚. 这 管脚 是 抽样 在 这

rising 边缘 的 sck 和 是 ignored 在 其它 时间. 它 应当 总是 是 驱动 至 一个 有效的

逻辑 水平的 至 满足 i

DD

规格.

* si 将 是 连接 至 所以 为 一个 单独的 管脚 数据 接口.

所以 输出 串行 输出: 这个 是 这 数据 输出 管脚. 它 是 驱动 在 一个 读 和 仍然是 触发-

陈述 在 所有 其它 时间 包含 当 /支撑 是 低. 数据 transitions 是 驱动 在

这 下落 边缘 的 这 串行 时钟.

* 所以 将 是 连接 至 si 为 一个 单独的 管脚 数据 接口.

VDD 供应 电源 供应 (2.7v 至 3.6v)

vss 供应 地面