µ

pd72001-11, 72001-a8

9

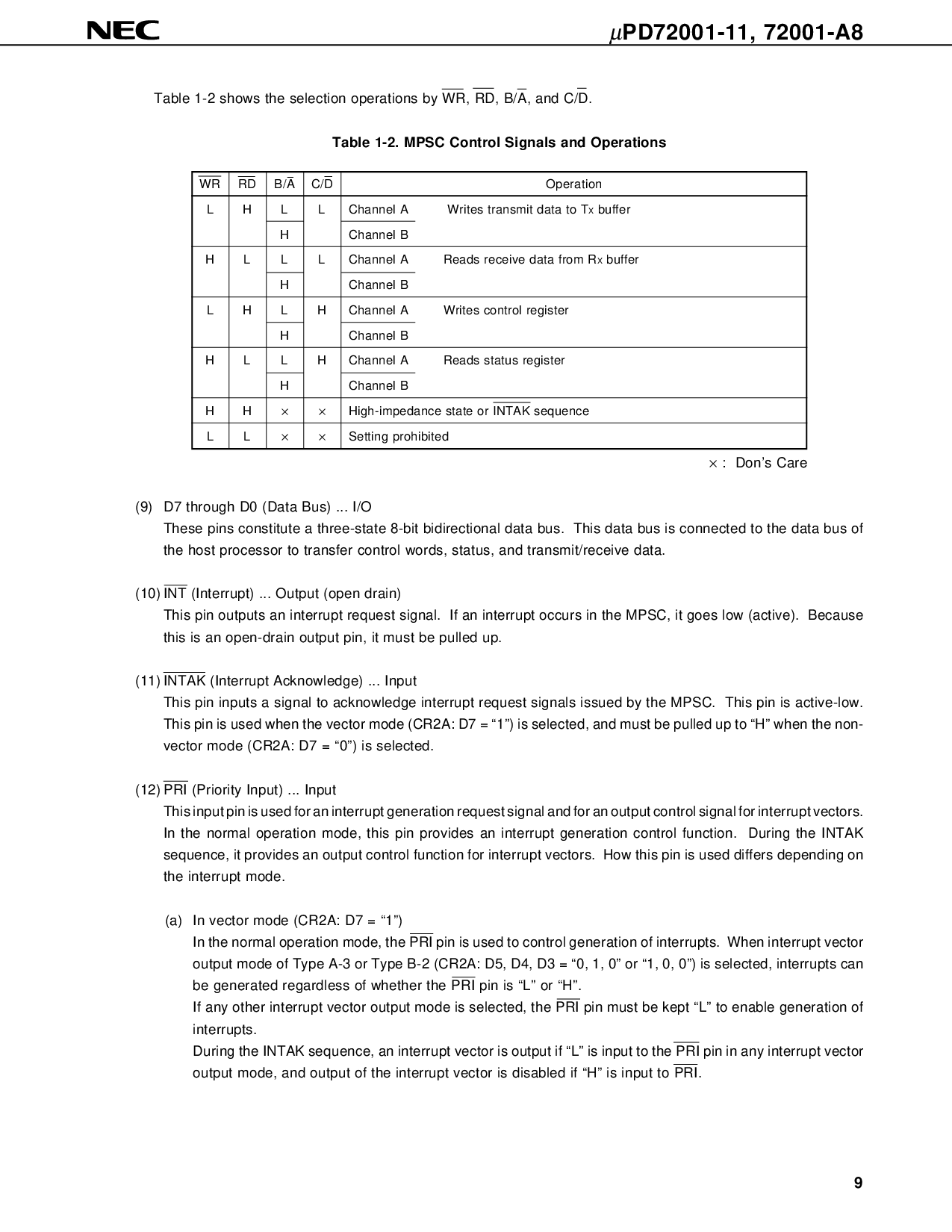

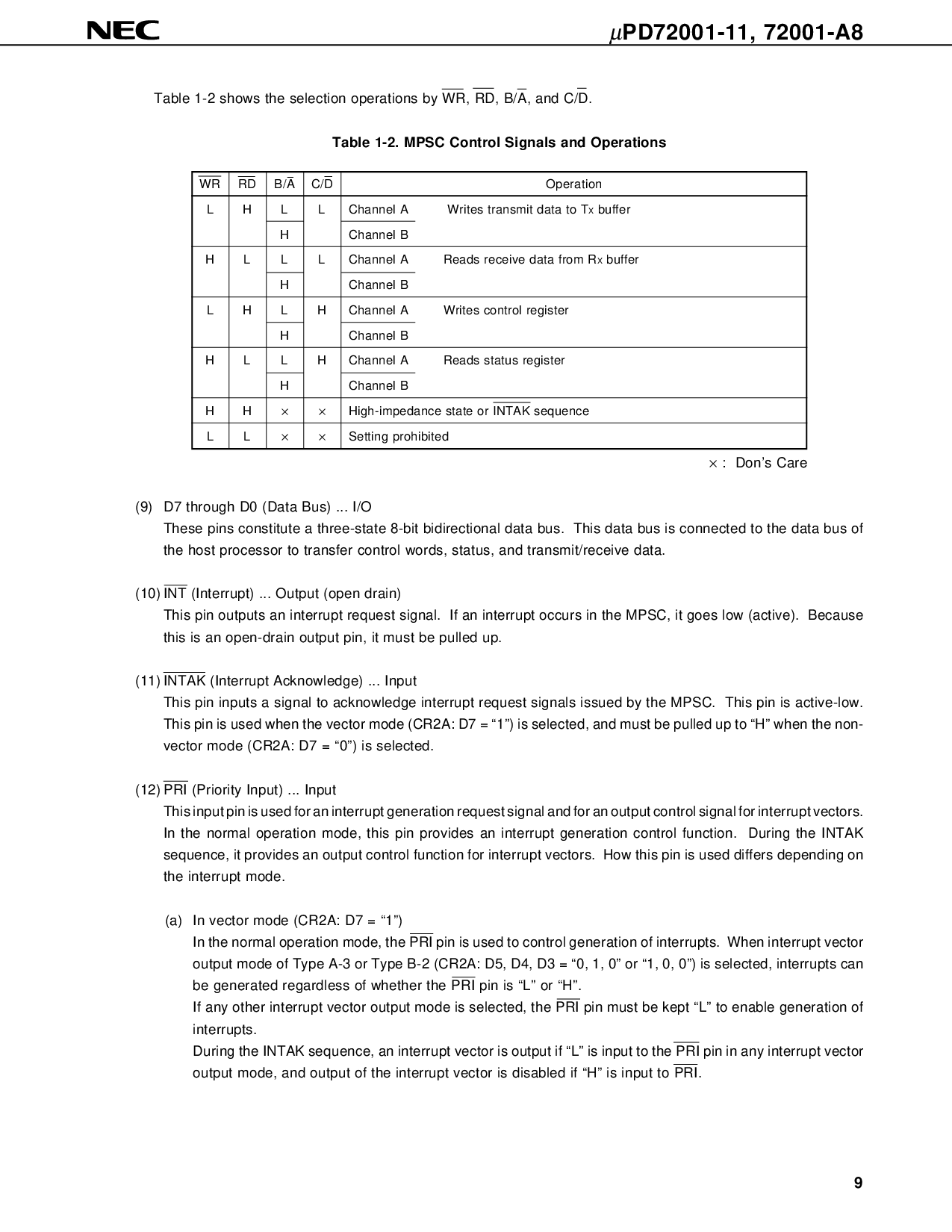

表格 1-2 显示 这 选择 行动 用 wr, rd, b/一个, 和 c/d.

表格 1-2. mpsc 控制 信号 和 行动

WR RD b/一个 c/d 运作

L H L L 频道 一个 写 transmit 数据 至 t

X

缓存区

H 频道 b

H L L L 频道 一个 读 receive 数据 从 r

X

缓存区

H 频道 b

L H L H 频道 一个 写 控制 寄存器

H 频道 b

H L L H 频道 一个 读 状态 寄存器

H 频道 b

HH

××

高-阻抗 状态 或者 intak sequence

LL

××

设置 prohibited

×

: don’s 小心

(9) d7 通过 d0 (数据 总线) ... i/o

这些 管脚 组成 一个 三-状态 8-位 双向的 数据 总线. 这个 数据 总线 是 连接 至 这 数据 总线 的

这 host 处理器 至 转移 控制 words, 状态, 和 transmit/receive 数据.

(10) int (中断) ... 输出 (打开 流)

这个 管脚 输出 一个 中断 要求 信号. 如果 一个 中断 occurs 在 这 mpsc, 它 变得 低 (起作用的). 因为

这个 是 一个 打开-流 输出 管脚, 它 必须 是 牵引的 向上.

(11) intak (中断 acknowledge) ... 输入

这个 管脚 输入 一个 信号 至 acknowledge 中断 要求 信号 issued 用 这 mpsc. 这个 管脚 是 起作用的-低.

这个 管脚 是 使用 当 这 vector 模式 (cr2a: d7 = “1”) 是 选择, 和 必须 是 牵引的 向上 至 “h” 当 这 非-

vector 模式 (cr2a: d7 = “0”) 是 选择.

(12) pri (priority 输入) ... 输入

这个 输入 管脚 是 使用 为 一个 中断 一代 要求 信号 和 为 一个 输出 控制 信号 为 中断 vectors.

在 这 正常的 运作 模式, 这个 管脚 提供 一个 中断 一代 控制 函数. 在 这 intak

sequence, 它 提供 一个 输出 控制 函数 为 中断 vectors. 如何 这个 管脚 是 使用 differs 取决于 在

这 中断 模式.

(一个) 在 vector 模式 (cr2a: d7 = “1”)

在 这 正常的 运作 模式, 这 pri 管脚 是 使用 至 控制 一代 的 中断. 当 中断 vector

输出 模式 的 类型 一个-3 或者 类型 b-2 (cr2a: d5, d4, d3 = “0, 1, 0” 或者 “1, 0, 0”) 是 selected, 中断 能

是 发生 regardless 的 whether 这 pri 管脚 是 “l” 或者 “h”.

如果 任何 其它 中断 vector 输出 模式 是 选择, 这 pri 管脚 必须 是 保持 “l” 至 使能 一代 的

中断.

在 这 intak sequence, 一个 中断 vector 是 输出 如果 “l” 是 输入 至 这 pri 管脚 在 任何 中断 vector

输出 模式, 和 输出 的 这 中断 vector 是 无能 如果 “h” 是 输入 至 pri.