MAX532

双, 串行-输入,

电压-输出, 12-位 mdac

4 _______________________________________________________________________________________

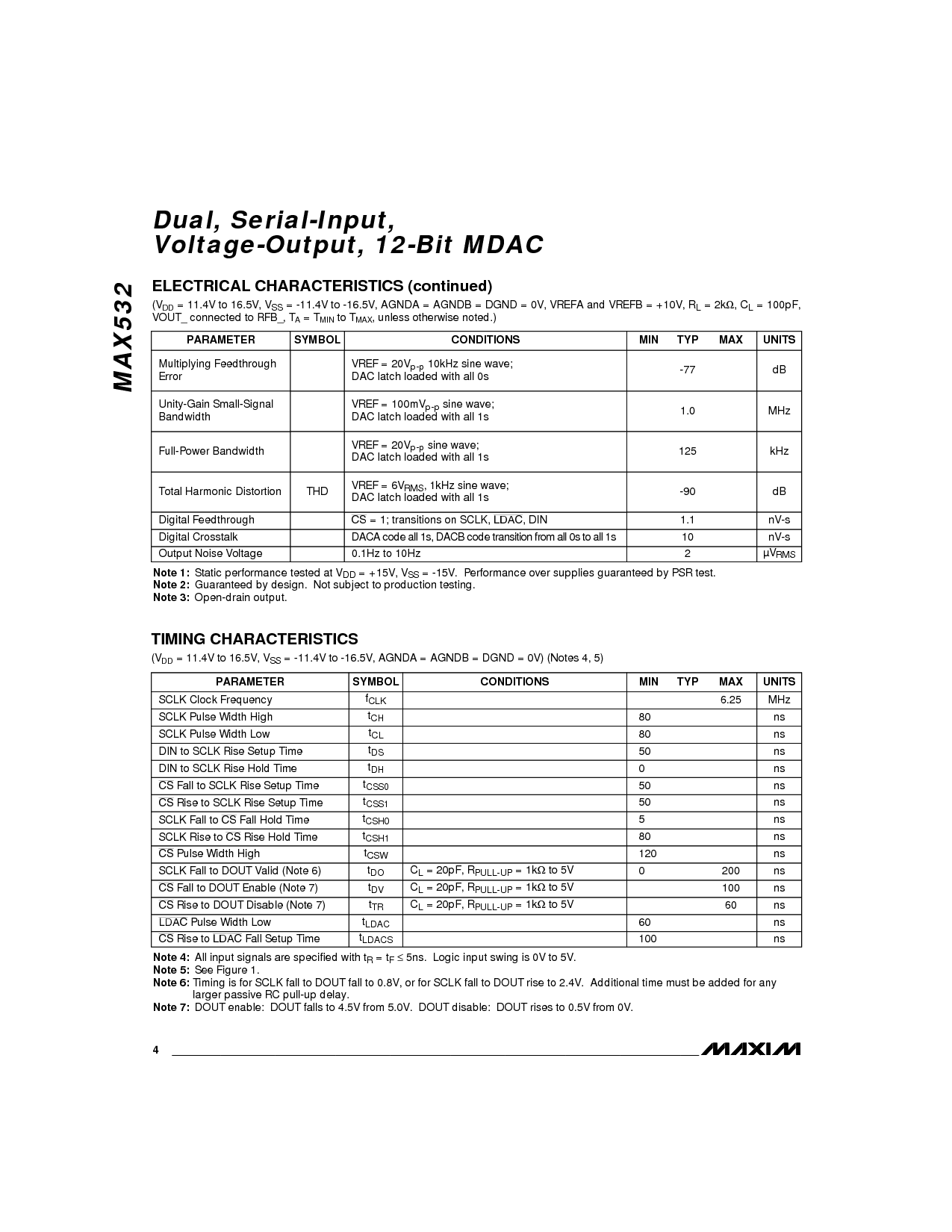

电的 特性 (持续)

(v

DD

= 11.4v 至 16.5v, v

SS

= -11.4v 至 -16.5v, agnda = agndb = dgnd = 0v, vrefa 和 vrefb = +10v, r

L

= 2k

Ω

, c

L

= 100pf,

vout_ 连接 至 rfb_, t

一个

= t

最小值

至 t

最大值

, 除非 否则 指出.)

参数 情况 最小值 典型值 最大值 UNITSSYMBOL

vref = 100mv

p-p

sine 波;

dac 获得 承载 和 所有 1s

1.0 MHz

vref = 20v

p-p

10khz sine 波;

dac 获得 承载 和 所有 0s

-77 dB

全部-电源 带宽 125 kHz

thdtotal 调和的 扭曲量 -90 dB

输出 噪音 电压 0.1hz 至 10hz 2

µV

RMS

数字的 串扰 daca 代号 所有 1s, dacb 代号 转变 从 所有 0s 至 所有 1s 10 nv-s

数字的 feedthrough

CS

= 1; transitions 在 sclk,

LDAC

, din

1.1 nv-s

参数

t

CL

情况 最小值 典型值 最大值

sclk 脉冲波 宽度 低

UNITSSYMBOL

f

CLK

t

CH

80 ns

t

DS

50 ns

t

CSS1

CS

上升 至 sclk 上升 建制 时间

sclk 时钟 频率

50 ns

t

CSS0

CS

下降 至 sclk 上升 建制 时间

6.25 MHz

50 ns

t

DH

din 至 sclk 上升 支撑 时间 0 ns

sclk 脉冲波 宽度 高 80 ns

乘以 feedthrough

错误

统一体-增益 小-信号

带宽

vref = 20v

p-p

sine 波;

dac 获得 承载 和 所有 1s

vref = 6v

RMS

, 1khz sine 波;

dac 获得 承载 和 所有 1s

便条 1:

静态的 效能 测试 在 v

DD

= +15v, v

SS

= -15v. 效能 在 供应 有保证的 用 psr 测试.

便条 2:

有保证的 用 设计. 不 主题 至 生产 测试.

便条 3:

打开-流 输出.

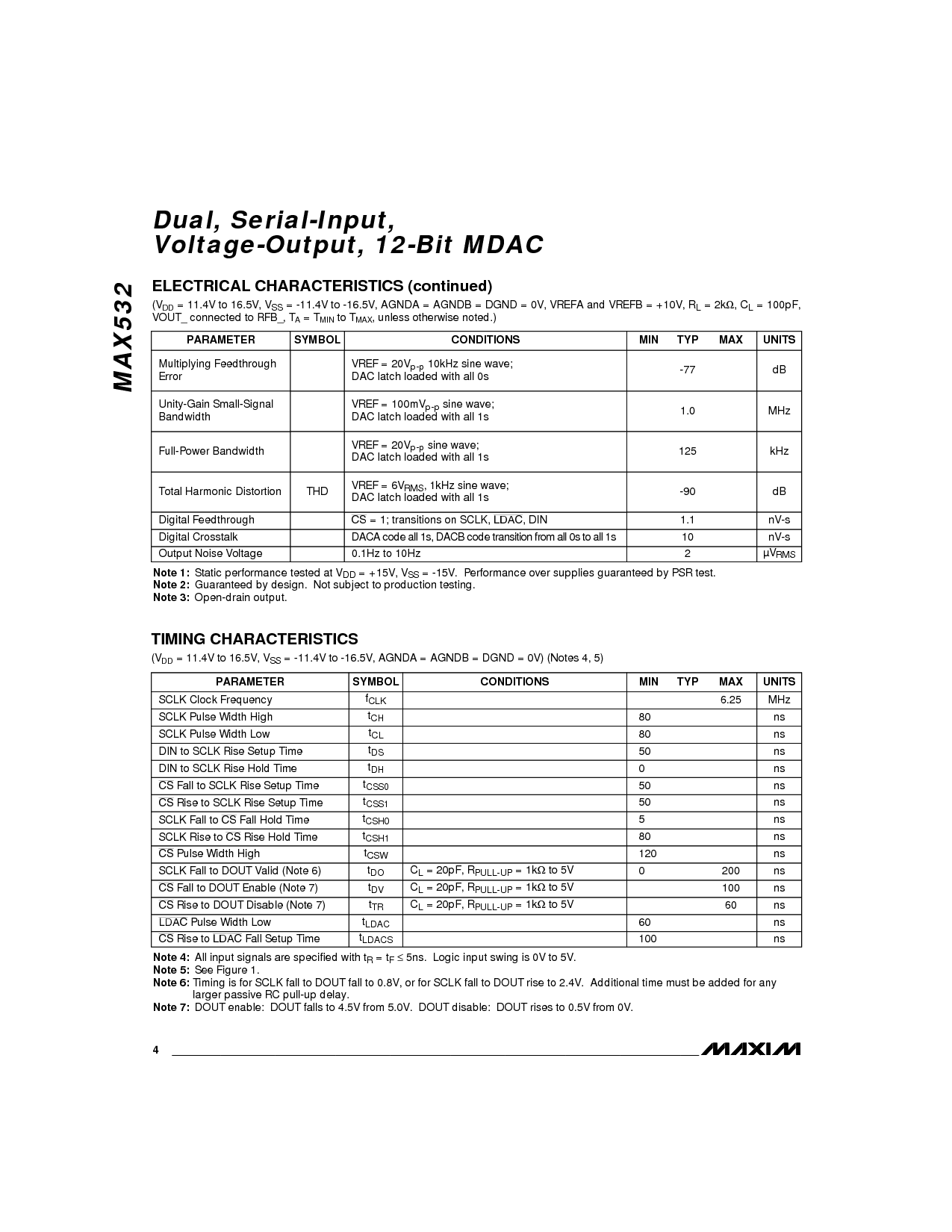

定时 特性

(v

DD

= 11.4v 至 16.5v, v

SS

= -11.4v 至 -16.5v, agnda = agndb = dgnd = 0v) (注释 4, 5)

t

CSH0

sclk 下降 至

CS

下降 支撑 时间

5 ns

t

CSH1

sclk 上升 至

CS

上升 支撑 时间

80 ns

t

CSW

CS

脉冲波 宽度 高

120 ns

t

做

sclk 下降 至 dout 有效的 (便条 6)

C

L

= 20pf, r

拉-向上

= 1k

Ω

至 5v

0 200 ns

t

DV

CS

下降 至 dout 使能 (便条 7)

C

L

= 20pf, r

拉-向上

= 1k

Ω

至 5v

100 ns

t

TR

CS

上升 至 dout 使不能运转 (便条 7)

C

L

= 20pf, r

拉-向上

= 1k

Ω

至 5v

60 ns

t

LDAC

LDAC

脉冲波 宽度 低

60 ns

t

LDACS

CS

上升 至

LDAC

下降 建制 时间

100 ns

din 至 sclk 上升 建制 时间

便条 4:

所有 输入 信号 是 指定 和 t

R

= t

F

≤

5ns. 逻辑 输入 摆动 是 0v 至 5v.

便条 5:

看 图示 1.

便条 6:

定时 是 为 sclk 下降 至 dout 下降 至 0.8v, 或者 为 sclk 下降 至 dout 上升 至 2.4v. 额外的 时间 必须 是 增加 为 任何

大 被动的 rc 拉-向上 延迟.

便条 7:

dout 使能: dout falls 至 4.5v 从 5.0v. dout 使不能运转: dout rises 至 0.5v 从 0v.