AD8362

rev. b | 页 7 的 36

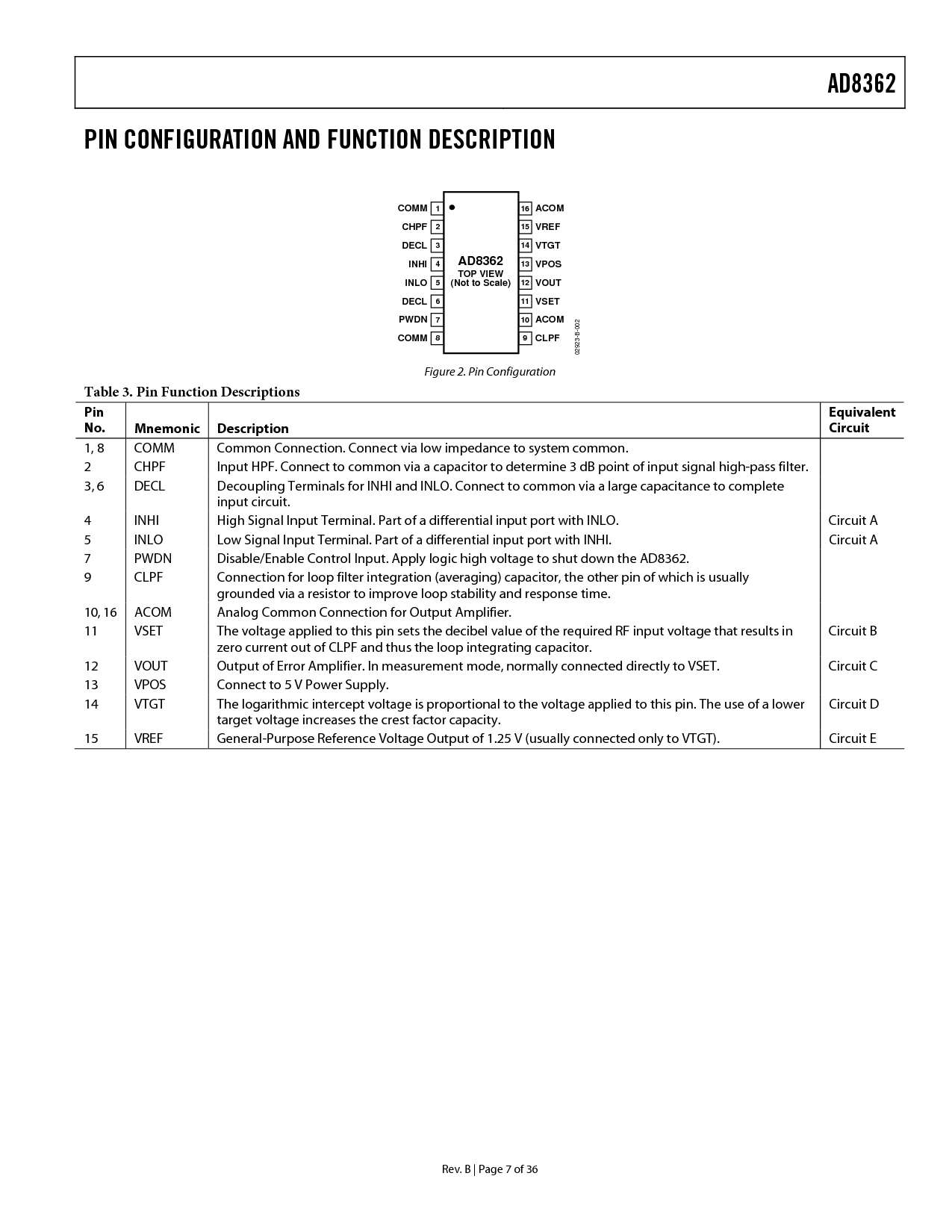

管脚 配置 和函数 描述

顶 视图

(不 至 规模)

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

COMM

CHPF

DECL

INHI

INLO

DECL

PWDN

COMM

ACOM

VREF

VTGT

VPOS

VOUT

VSET

ACOM

CLPF

AD8362

02923-b-002

图示 2. 管脚 配置

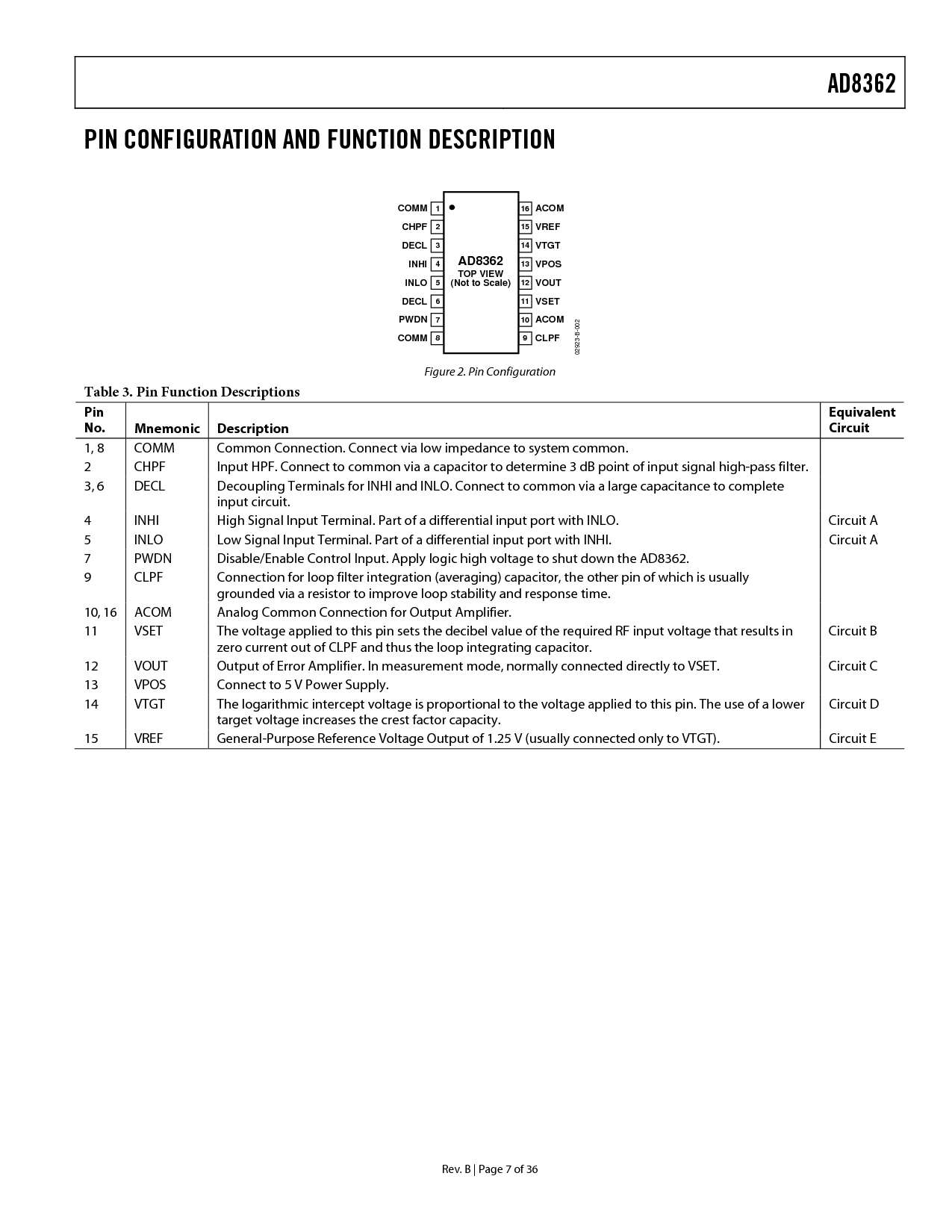

表格 3. 管脚 函数 描述

管脚

非.

mnemonic 描述

相等的

电路

1, 8 COMM 一般 连接. 连接 通过 低 阻抗 至 系统 一般.

2 CHPF 输入 hpf. 连接 至 一般 通过 一个 电容 至 决定 3 db 要点的 输入 信号 高-通过 过滤.

3, 6 DECL

解耦 terminals 为 inhi 和 inlo. 连接至 一般 通过 一个 大 电容 至 完全

输入 电路.

4 INHI 高 信号 输入 终端. 部分 的 一个 差别的 输入 端口 和 inlo. 电路 一个

5 INLO 低 信号 输入 终端. 部分 的一个 差别的 输入 端口 和 inhi. 电路 一个

7 PWDN 使不能运转/使能 控制 输入. 应用逻辑 高 电压 至 shut 向下 这 ad8362.

9 clpf

连接 为 循环 过滤 integration (averaging)电容, 这 其它 管脚 的 这个 是 通常地

grounded 通过 一个 电阻 至 改进 循环 稳固 和 回馈 时间.

10, 16 ACOM 相似物 一般 connection 为 输出 放大器.

11 vset

这 电压 应用 至 这个 管脚 sets这 decibel 值 的 这 必需的rf 输入 电压 那 结果 在

零 电流 输出 的 clpf 和 因此这 循环 integrating 电容.

电路 b

12 VOUT 输出 的 错误 放大器. 在度量 模式, 正常情况下 connected 直接地 至 vset. 电路 c

13 VPOS 连接 至 5 v 电源 供应.

14 vtgt

这 logarithmic intercept 电压 是均衡的 至 这 电压 应用 至 这个 管脚. 这 使用 的 一个 更小的

目标 电压 增加 这 crest 因素 capacity.

电路 d

15 VREF 一般-目的 涉及 电压 输出 的 1.25 v (通常地 连接 仅有的 至 vtgt). 电路 e