5

fn9034.2

12月 27, 2004

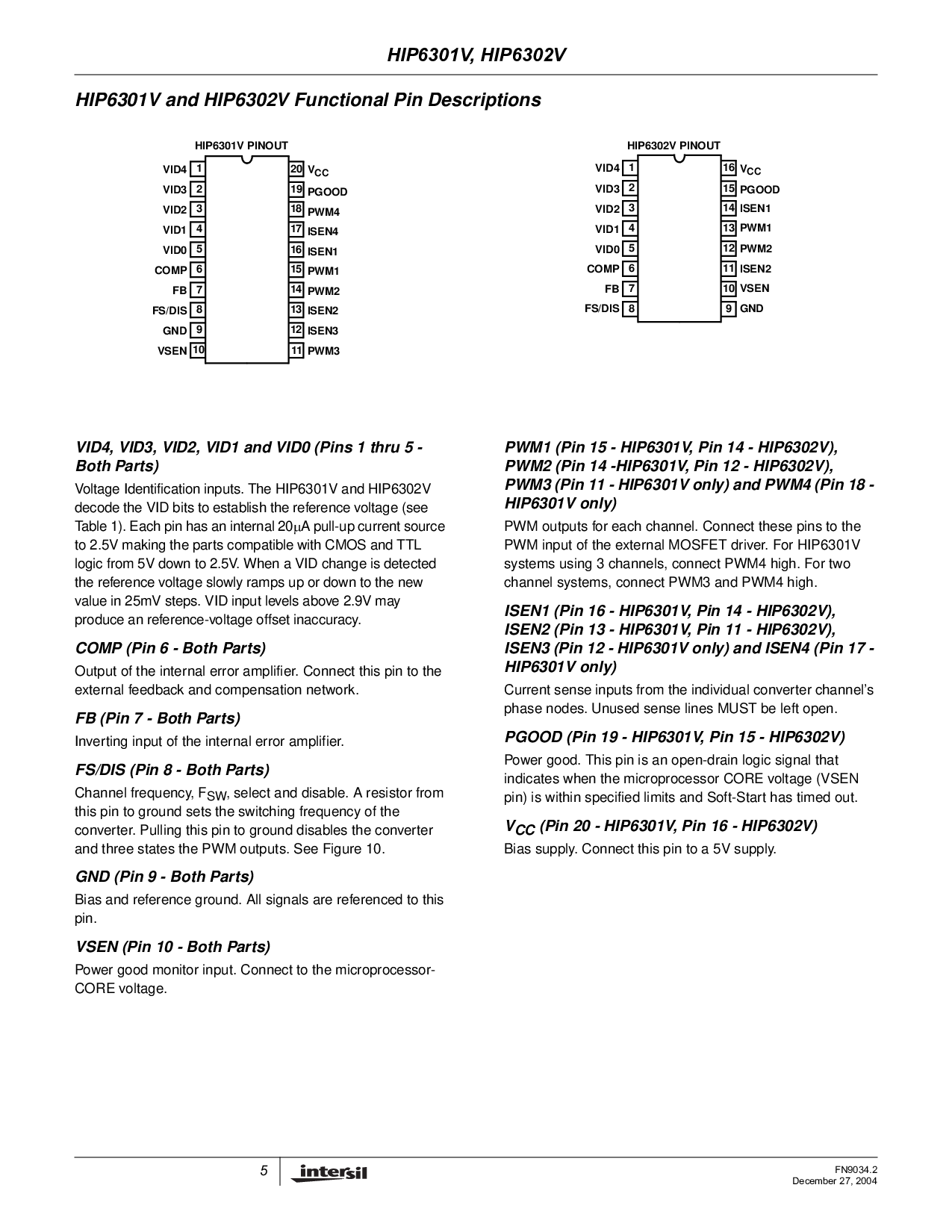

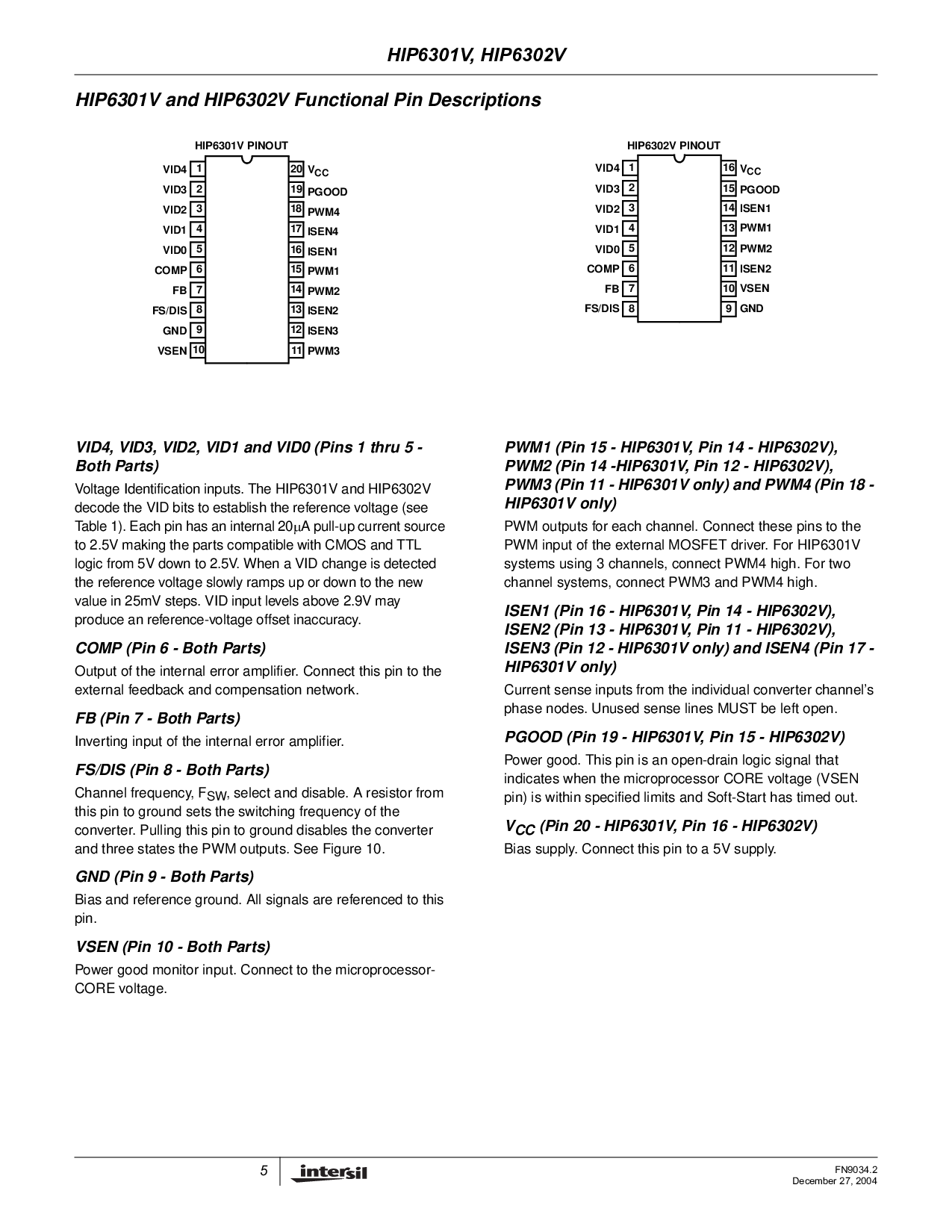

hip6301v 和 hip6302v 函数的 pin 描述

vid4, vid3, vid2, vid1 和 vid0 (管脚 1 thru 5 -

两个都 部分)

电压 identification 输入.这 hip6301v 和 hip6302v

decode 这 vid 位 至 establish 这 涉及 电压 (看

表格 1). 各自 管脚 有 一个 内部的 20

µ

一个 拉-向上 电流 源

至 2.5v 制造 这 部分 兼容 和 cmos 和 ttl

逻辑 从 5v 向下 至 2.5v. 当 一个 vid 改变 是 发现

这 涉及 电压 慢速地 ramps 向上 或者 向下 至 这 新

值 在 25mv 步伐. vid 输入 水平 在之上 2.9v 将

生产 一个 涉及-电压 补偿 inaccuracy.

竞赛 (管脚 6 - 两个都 部分)

输出 的 这 内部的 错误 放大器. 连接 这个 管脚 至 这

外部 反馈 和 补偿 网络.

fb (管脚 7 - 两个都 部分)

反相的 输入 的 这 内部的 错误 放大器.

fs/dis (管脚 8 - 两个都 部分)

频道 频率, f

SW

, 选择 和 使不能运转. 一个 电阻 从

这个 管脚 至 地面 sets 这 切换 频率 的 这

转换器. 拉 这个 管脚 至 地面 使不能运转 这 转换器

和 三 states 这 pwm 输出. 看 图示 10.

地 (管脚 9 - 两个都 部分)

偏差 和 涉及 地面. 所有 信号 是 关联 至 这个

管脚.

vsen (管脚 10 - 两个都 部分)

电源 好的 监控 输入. 连接 至 这 微处理器-

核心 电压.

pwm1 (管脚 15 - hip6301v, 管脚 14 - hip6302v),

pwm2 (管脚 14 -hip6301v, 管脚 12 - hip6302v),

pwm3 (管脚 11 - hip6301v 仅有的) 和 pwm4 (管脚 18 -

hip6301v 仅有的)

pwm 输出 为 各自 频道. 连接 这些 管脚 至 这

pwm 输入 的 这 外部 场效应晶体管 驱动器. 为 hip6301v

系统 使用 3 途径, connect pwm4 高. 为 二

频道 系统, 连接pwm3 和 pwm4 高.

isen1 (管脚 16 - hip6301v, 管脚 14 - hip6302v),

isen2 (管脚 13 - hip6301v, 管脚 11 - hip6302v),

isen3 (管脚 12 - hip6301v 仅有的) 和 isen4 (管脚 17 -

hip6301v 仅有的)

电流 sense 输入 从 这 单独的 转换器 频道’s

阶段 nodes. unused sense 线条 必须 是 left 打开.

pgood (管脚 19 - hip6301v, 管脚 15 - hip6302v)

电源 好的. 这个 管脚 是 一个 打开-流 逻辑 信号 那

indicates 当 这 microprocessor 核心 电压 (vsen

管脚) 是 在里面 指定 限制 和 软-星t 有 安排时间 输出.

V

CC

(管脚 20 - hip6301v, 管脚 16 - hip6302v)

偏差 供应. 连接 这个 管脚 至 一个 5v 供应.

11

12

13

14

15

16

17

18

20

19

10

9

8

7

6

5

4

3

2

1

VID4

VID3

VID2

VID1

VID0

fs/dis

PWM2

PGOOD

PWM3

ISEN4

ISEN1

V

CC

地

ISEN3

FB

PWM4

VSEN

竞赛

PWM1

ISEN2

hip6301v 引脚

9

10

11

12

13

14

16

15

8

7

6

5

4

3

2

1

VID4

VID3

VID2

VID1

VID0

fs/dis

VSEN

PGOOD

PWM2

V

CC

FB

竞赛

ISEN2

地

hip6302v 引脚

ISEN1

PWM1

hip6301v, hip6302v