scls407j −april 1998 − 修订 april 2005

2

邮递 办公室 盒 655303

•

达拉斯市, 德州 75265

描述/订货 信息 (持续)

当 这 获得-使能 (le) 输入 是 高, 这 q 输出 follow 这 数据 (d) inputs. 当 le 是 带去 low, 这

q 输出 是 latched 在 这 逻辑 水平 设置 向上 在 这 d 输入.

一个 缓冲 输出-使能 (oe

) 输入 能 是 使用 至 放置 这 第八 输出 在 也 一个 正常的 逻辑 状态 (高

或者 低) 或者 这 高-阻抗 状态. 在 这 高-阻抗 state, 这 输出 neither 加载 也不 驱动 这 总线 线条

significantly. 这 高-阻抗 状态 和 增加 驱动 提供 这 能力 至 驱动 总线 线条 没有

需要 为 接口 或者 pullup 组件.

OE

做 不 影响 这 内部的 行动 的 这 latches. old 数据 能 是 retained 或者 新 数据 能 是 entered

当 这 输出 是 在 这 高-阻抗 状态.

至 确保 这 高-阻抗 状态 在 电源 向上 或者 电源 向下, oe

应当 是 系 至 v

CC

通过 一个 pullup

电阻; 这 最小 值 的 这 电阻 是 决定 用 这 电流-sinking 能力 的 这 驱动器.

这些 设备 是 全部地 指定 为 partial-电源-向下 产品 使用 i

止

. 这 i

止

电路系统 使不能运转 这

输出, 阻止 损害的 电流 backflow 通过 这 设备 当 它们 是 powered 向下.

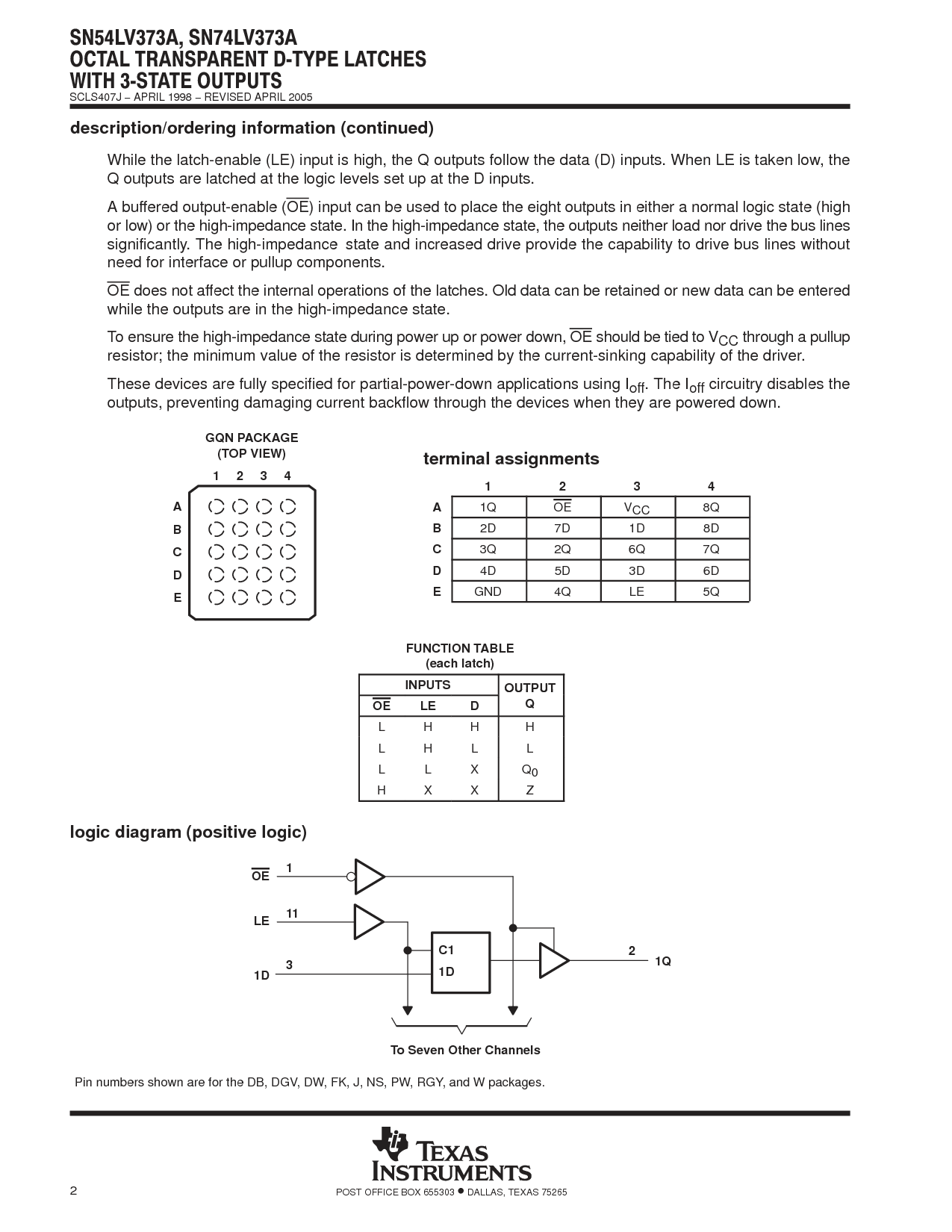

终端 assignments

1234

一个

1Q OE V

CC

8Q

B

2D 7D 1D 8D

C

3Q 2Q 6Q 7Q

D

4D 5D 3D 6D

E

地 4Q LE 5Q

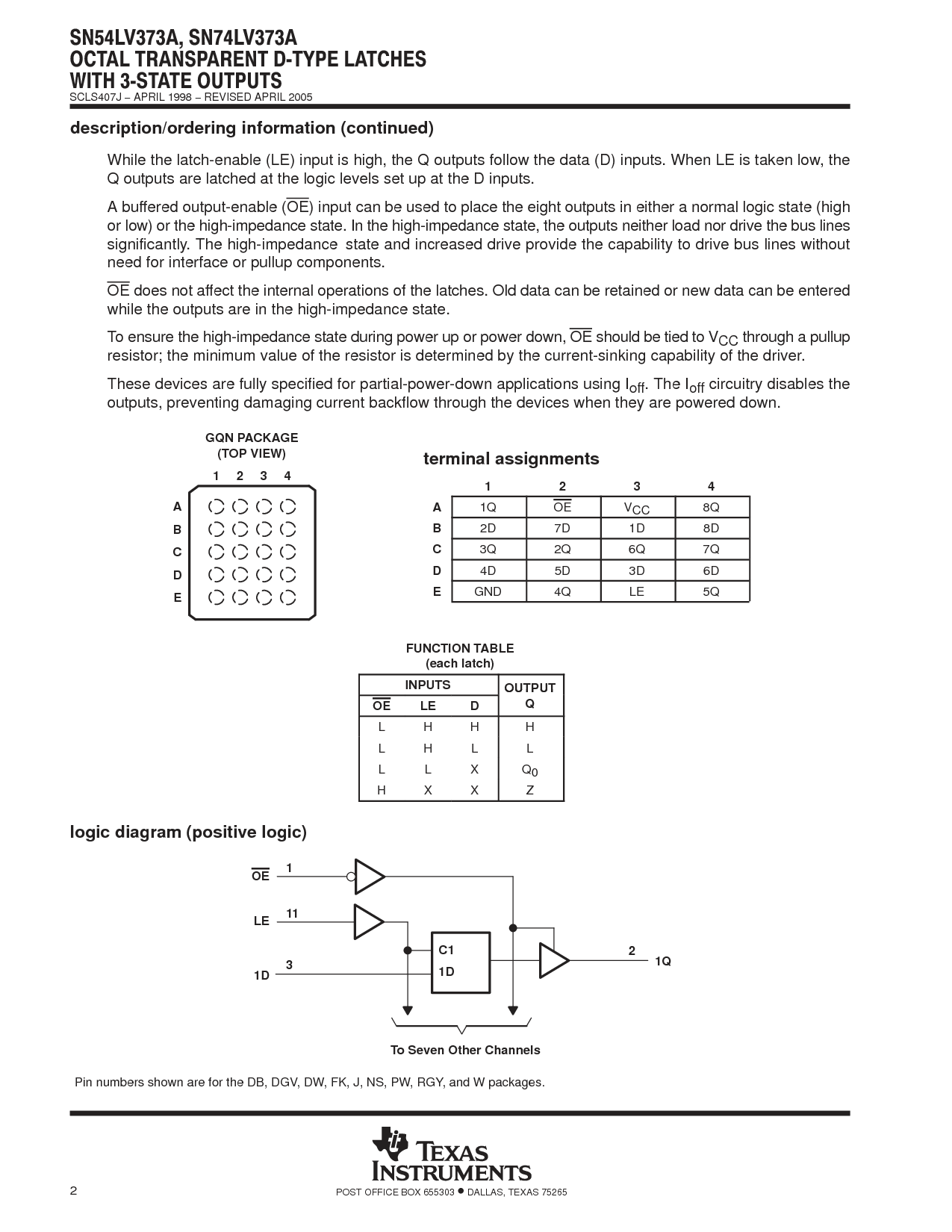

函数 表格

(各自 获得)

输入

输出

OE LE D

输出

Q

L H H H

L HL L

L LX Q

0

H X X Z

逻辑 图解 (积极的 逻辑)

OE

至 七 其它 途径

1

11

3

2

LE

1D

C1

1D

1Q

管脚 号码 显示 是 为 这 db, dgv, dw, fk, j, ns, pw, rgy, 和 w packages.

gqn 包装

(顶 视图)

1234

一个

B

C

D

E