mc54/74hc138a

MOTOROLA high–speed cmos 逻辑 数据

dl129 — rev 6

4

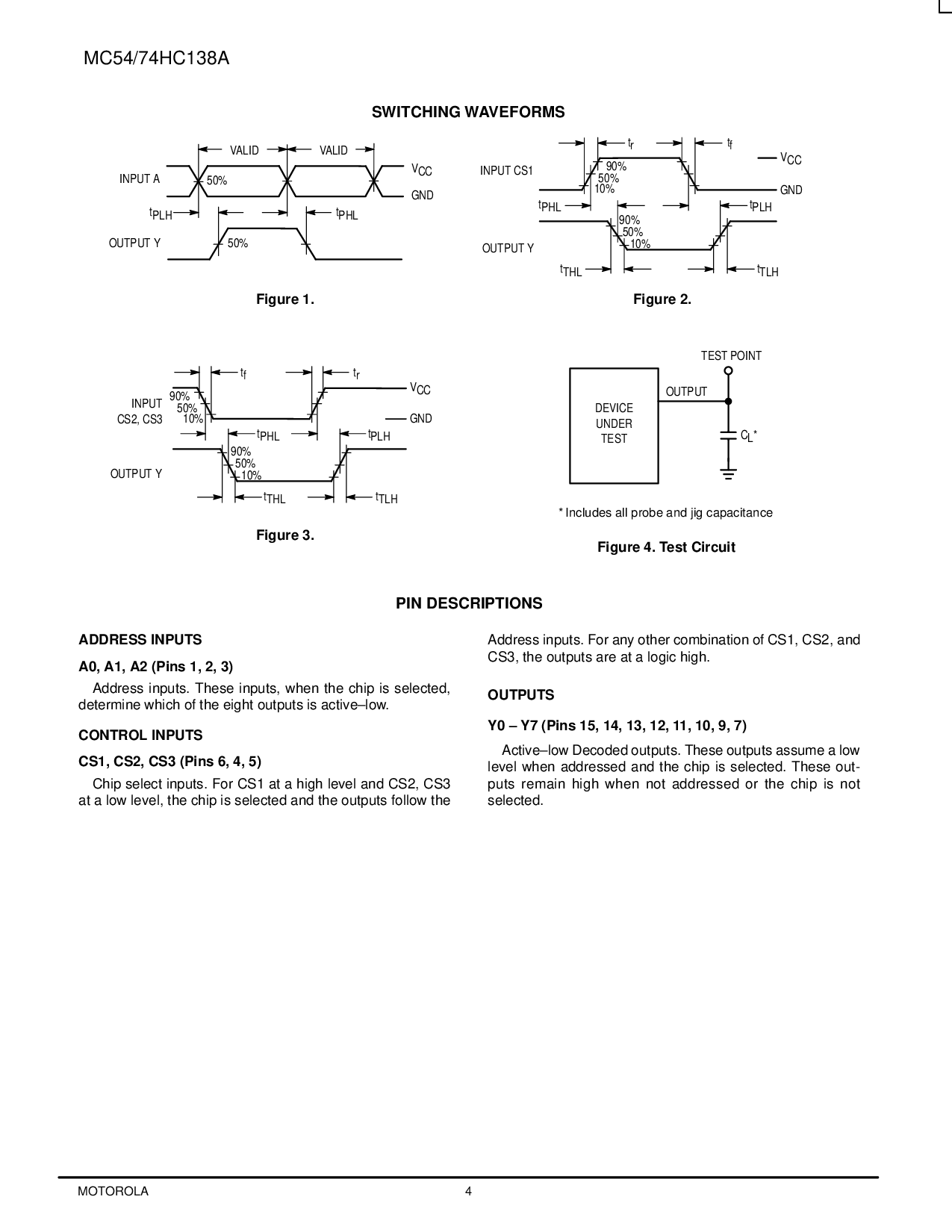

图示 1.

50%

t

PHL

t

PLH

V

CC

地

图示 2.

有效的 有效的

输出 y 50%

t

f

t

r

V

CC

地

t

PLH

t

TLH

90%

50%

10%

输出 y

输入 cs1

t

PHL

90%

50%

10%

t

THL

输入 一个

切换 波形

t

THL

t

TLH

V

CC

地

t

r

t

PHL

t

PLH

输出 y

输入

cs2, cs3

90%

50%

10%

90%

50%

10%

图示 3.

t

f

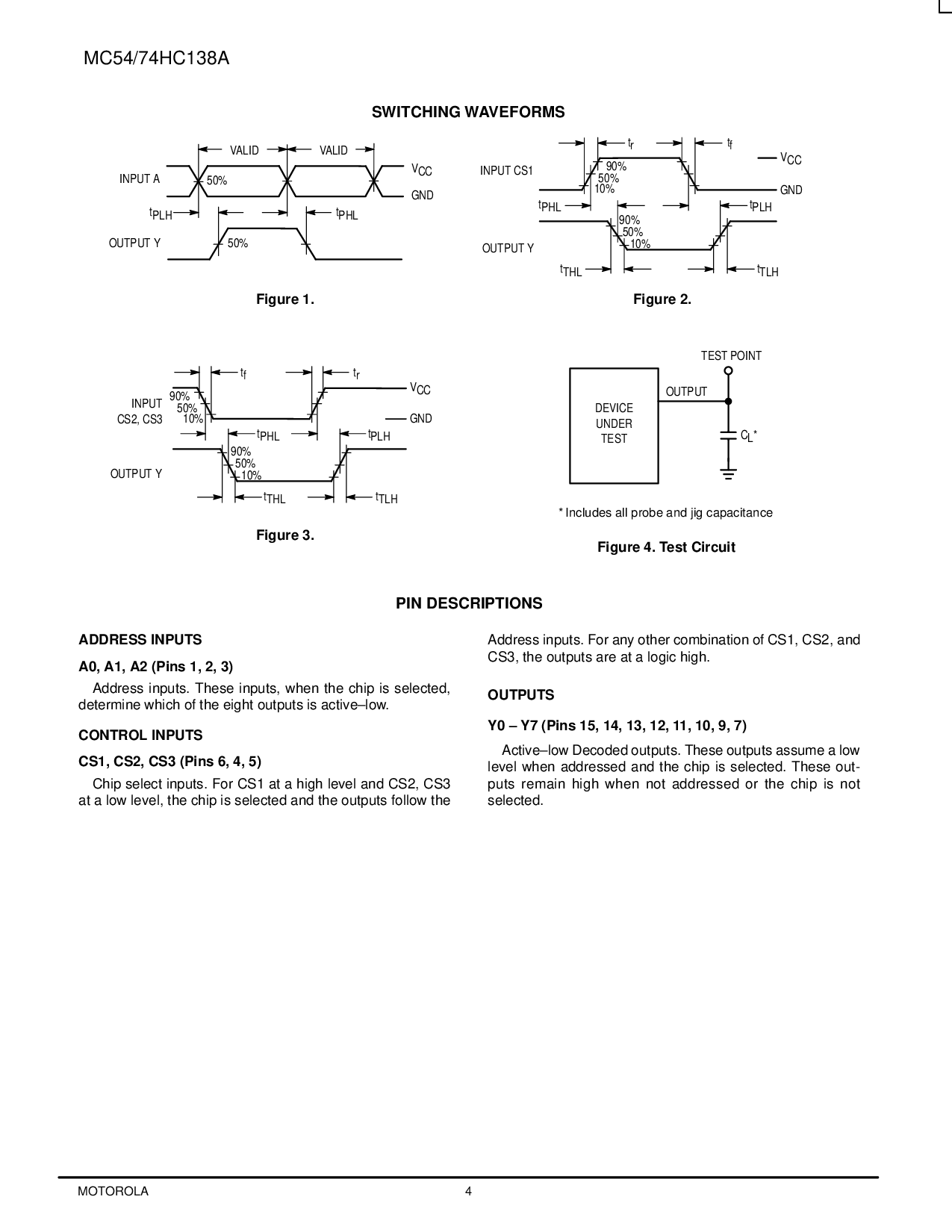

* 包含 所有 探查 和 jig 电容

图示 4. 测试 电路

C

L

*

测试 要点

设备

下面

测试

输出

管脚 描述

地址 输入

a0, a1, a2 (管脚 1, 2, 3)

地址输入. 这些 输入, 当 这 碎片 是 选择,

决定 这个 的 这 第八 输出 是 active–low.

控制 输入

cs1, cs2, cs3 (管脚 6, 4, 5)

碎片选择 输入. 为 cs1 在 一个高 水平的 和 cs2, cs3

在 一个低 水平的, 这 碎片 是 选择 和 这 输出 follow 这

地址输入. 为 任何 其它 结合体 的 cs1, cs2,和

cs3, 这 输出 是 在 一个 逻辑 高.

输出

y0 – y7 (管脚 15, 14, 13, 12, 11, 10, 9, 7)

Active–low解码 输出. 这些 输出 假设 一个 低

水平的当 addressed 和 这 碎片 是 选择. 这些 输出-

putsremain high when not 一个ddressed or the chip is not

选择.