max807l/m/n

全部-featured µp supervisory 电路 和

±1.5% 重置 精度

_______________________________________________________________________________________ 9

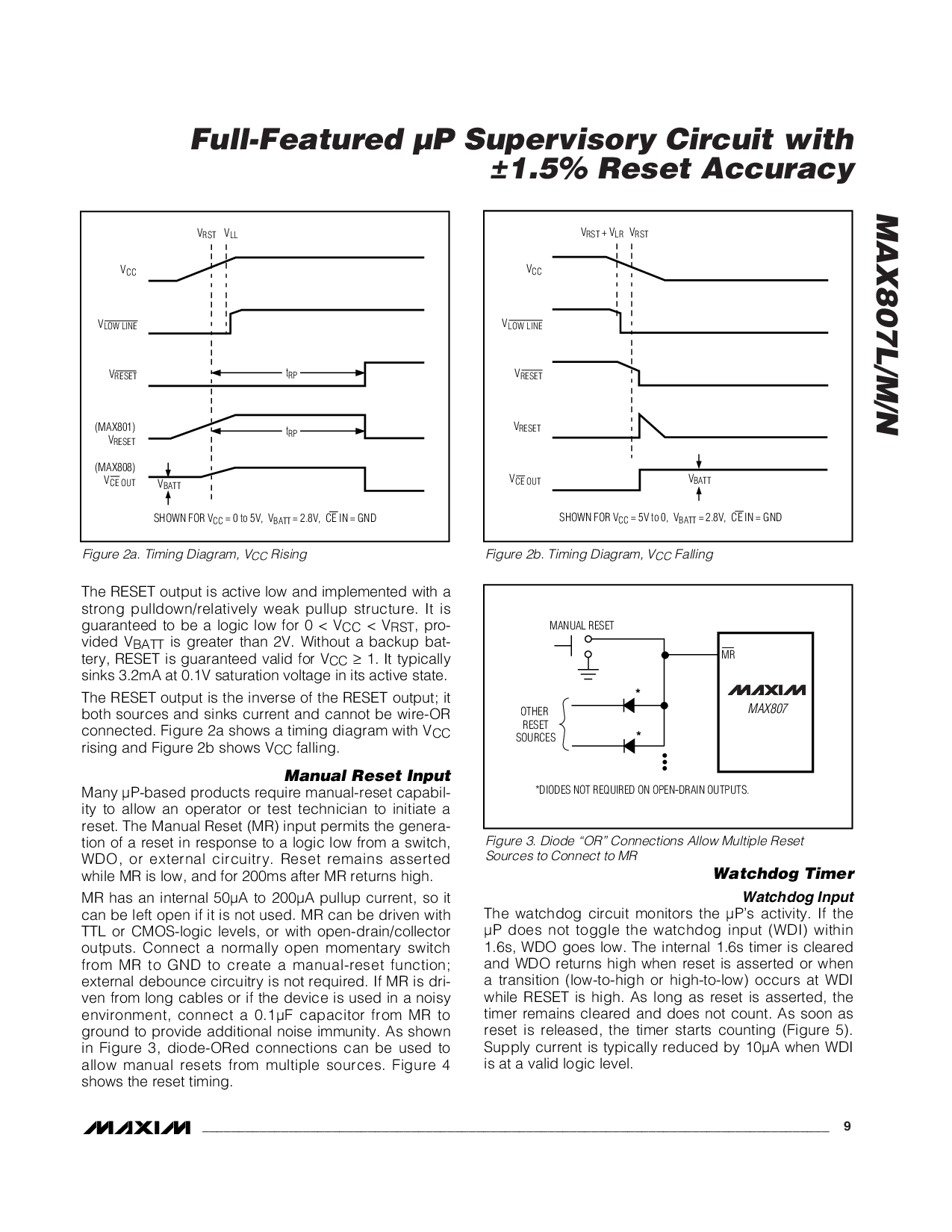

这 重置 输出 是 起作用的 低 和 执行 和 一个

强 pulldown/相当地 弱 pullup 结构. 它 是

有保证的 至 是 一个 逻辑 低 为 0 < v

CC

< v

RST

, pro-

vided v

BATT

是 更好 比 2v. 没有 一个 backup bat-

tery, 重置 是 有保证的 有效的 为 v

CC

≥

1. 它 典型地

sinks 3.2ma 在 0.1v 饱和 电压 在 它的 起作用的 状态.

这 重置 输出 是 这 inverse 的 这 重置 输出; 它

两个都 来源 和 sinks 电流 和 不能 是 线-或者

连接. 图示 2a 显示 一个 定时 图解 和 v

CC

rising 和 图示 2b 显示 v

CC

下落.

手工的 重置 输入

许多 µp-为基础 产品 需要 手工的-重置 capabil-

ity 至 准许 一个 运行器 或者 测试 technician 至 initiate 一个

重置. 这 手工的 重置 (mr) 输入 准许 这 genera-

tion 的 一个 重置 在 回馈 至 一个 逻辑 低 从 一个 转变,

wdo, 或者 外部 电路系统. 重置 仍然是 asserted

当 mr 是 低, 和 为 200ms 之后 mr returns 高.

MR 有 一个 内部的 50µa 至 200µa pullup 电流, 所以 它

能 是 left 打开 如果 它 是 不 使用. mr 能 是 驱动 和

ttl 或者 cmos-逻辑 水平, 或者 和 打开-流/集电级

输出. 连接 一个 正常情况下 打开 momentary 转变

从 mr 至 地 至 create 一个 手工的-重置 函数;

外部 debounce 电路系统 是 不 必需的. 如果 mr 是 dri-

ven 从 长 cables 或者 如果 这 设备 是 使用 在 一个 嘈杂的

环境, 连接 一个 0.1µf 电容 从 mr 至

地面 至 提供 额外的 噪音 免除. 作 显示

在 图示 3, 二极管-ored 连接 能 是 使用 至

准许 手工的 resets 从 多样的 来源. 图示 4

显示 这 重置 定时.

看门狗 计时器

看门狗 输入

这 看门狗 电路 monitors 这 µp’s activity. 如果 这

µp 做 不 toggle 这 看门狗 输入 (wdi) 在里面

1.6s, wdo 变得 低. 这 内部的 1.6s 计时器 是 cleared

和 wdo returns 高 当 重置 是 asserted 或者 当

一个 转变 (低-至-高 或者 高-至-低) occurs 在 wdi

当 重置 是 高. 作 长 作 重置 是 asserted, 这

计时器 仍然是 cleared 和 做 不 计数. 作 soon 作

重置 是 released, 这 计时器 开始 counting (图示 5).

供应 电流 是 典型地 减少 用 10µa 当 wdi

是 在 一个 有效的 逻辑 水平的.

V

重置

V

低 线条

V

CC

(max801)

V

重置

(max808)

V

ce 输出

V

RST

V

LL

t

RP

t

RP

V

BATT

显示 为 v

CC

= 0 至 5v, v

BATT

= 2.8v, ce 在 = 地

V

重置

V

低 线条

V

CC

V

重置

V

ce 输出

V

RST

V

RST

+ v

LR

V

BATT

显示 为 v

CC

= 5v 至 0, v

BATT

= 2.8v, ce 在 = 地

图示 2a. 定时 图解, v

CC

Rising 图示 2b. 定时 图解, v

CC

下落

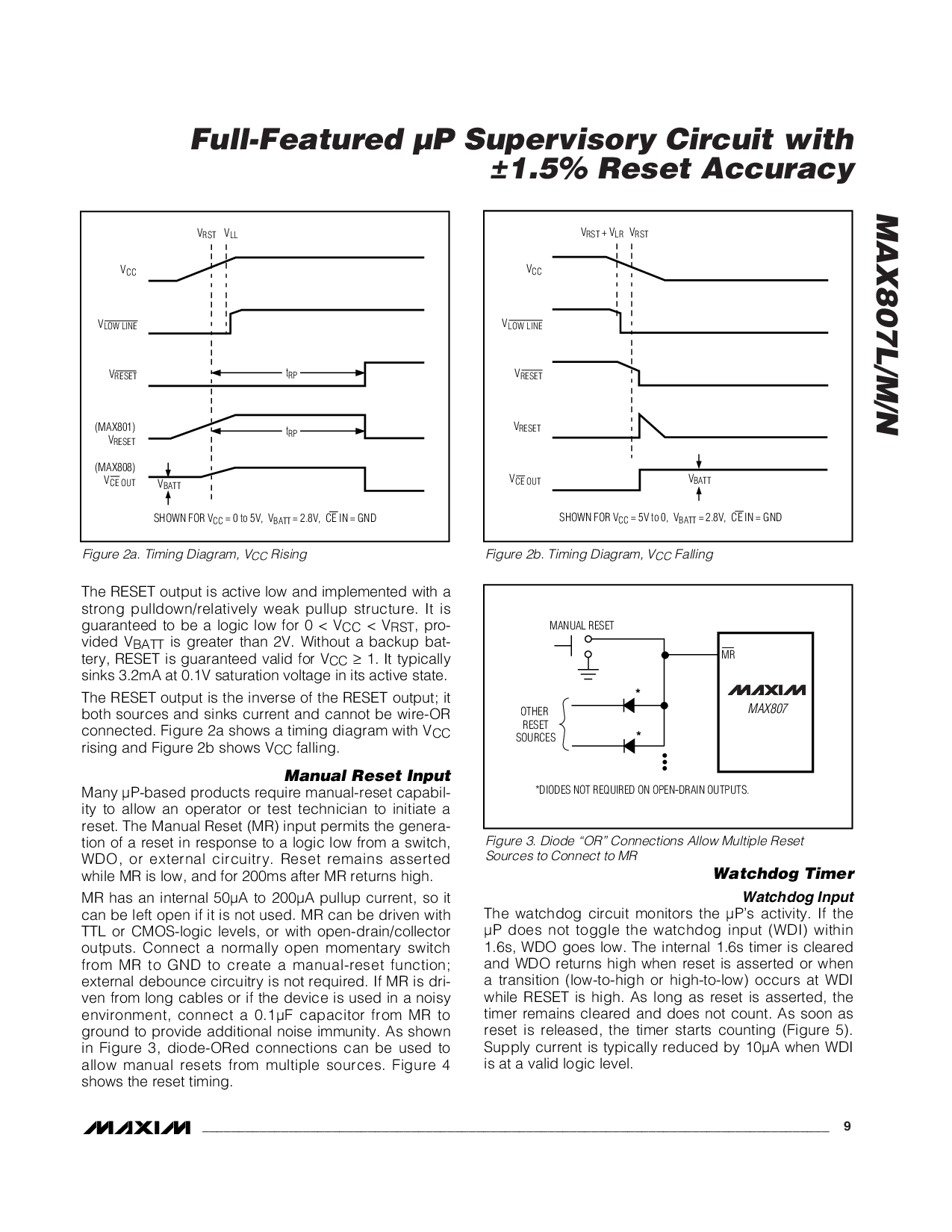

MAX807

*

*

其它

重置

来源

手工的 重置

MR

*diodes 不 必需的 在 打开-流 输出.

图示 3. 二极管 “or” 连接 准许 多样的 重置

来源 至 连接 至 mr