MT9079

4-240

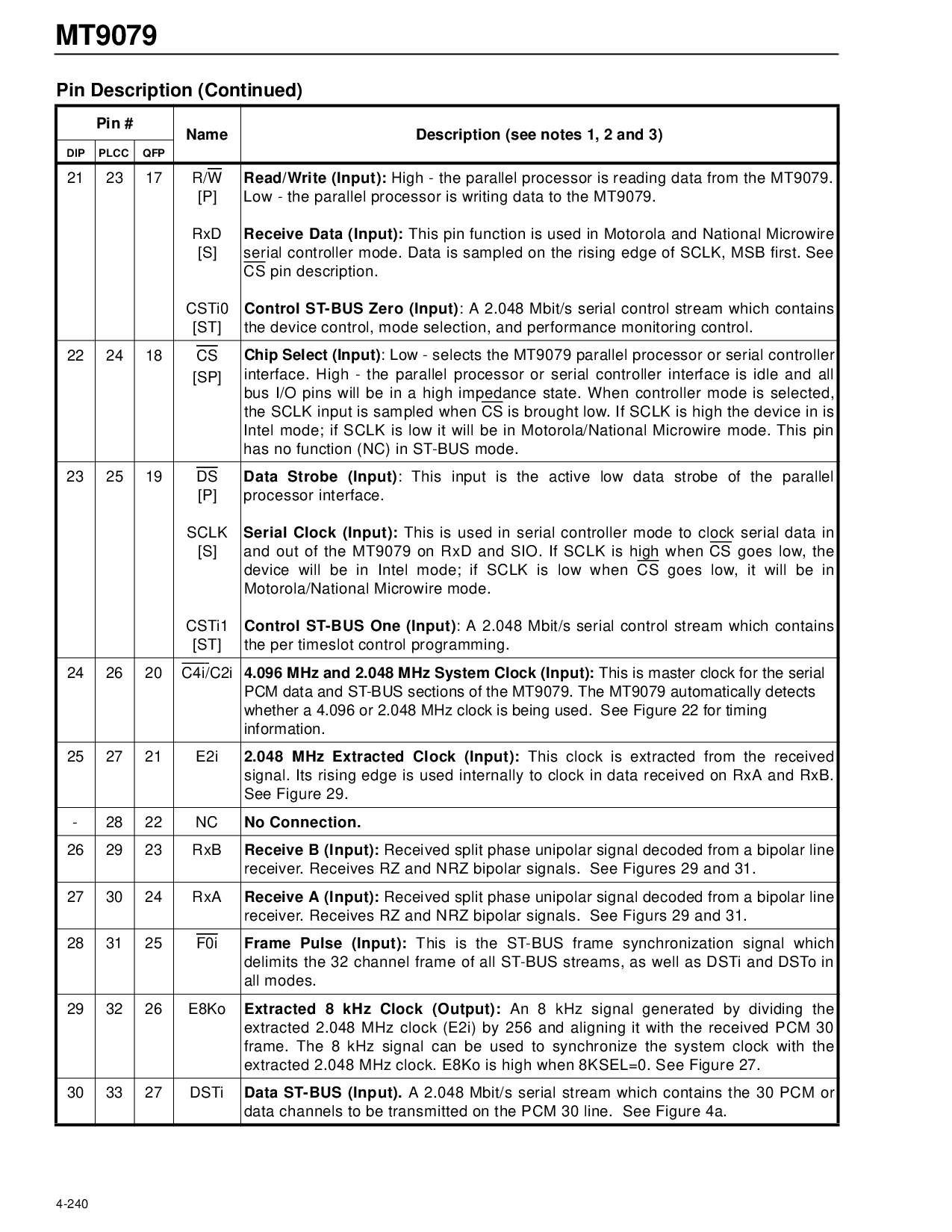

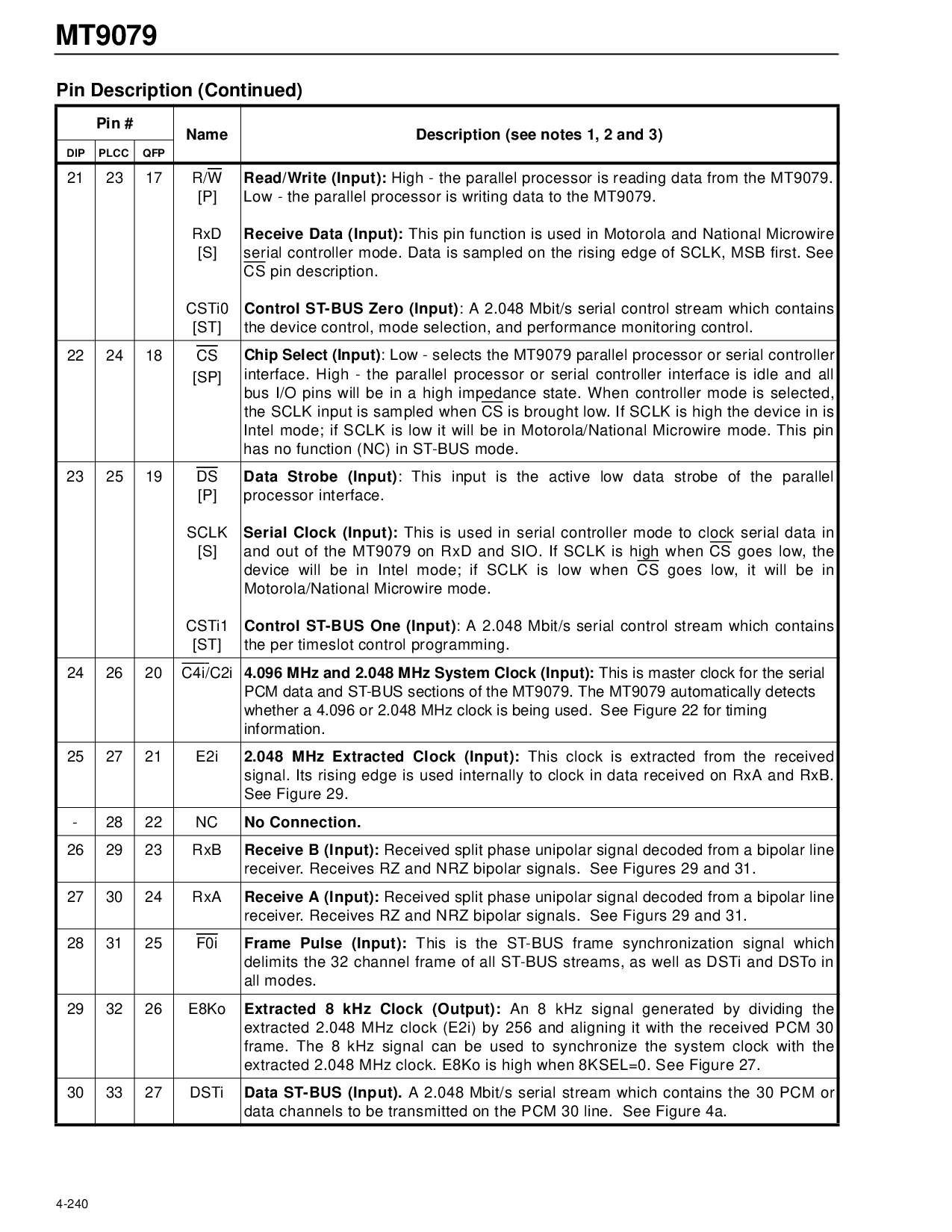

21 23 17 r/w

[P]

RxD

[S]

CSTi0

[ST]

读/写 (输入):

高 - 这 并行的 处理器 是 读 数据 从 这 mt9079.

低 - 这 并行的 处理器 是 writing 数据 至 这 mt9079.

receive 数据 (输入):

这个 管脚 函数 是 使用 在 motorola 和 国家的 microwire

串行 控制 模式. 数据 是 抽样 在 这 rising 边缘 的 sclk, msb 第一. 看

CS

管脚 描述.

控制 st-总线 零 (输入)

: 一个 2.048 mbit/s 串行 控制 stream 这个 包含

这 设备 控制, 模式 选择, 和 效能 monitoring 控制.

22 24 18 CS

[SP]

碎片 选择 (输入)

: 低 - 选择 这 mt9079 并行的 处理器 或者 串行 控制

接口. 高 - 这 并行的 处理器 或者 串行 控制 接口 是 空闲 和 所有

总线 i/o 管脚 将 是 在 一个 高 阻抗 状态. 当 控制 模式 是 选择,

这 sclk 输入 是 抽样 当 cs

是 brought 低. 如果 sclk 是 高 这 设备 在 是

intel 模式; 如果 sclk 是 低 它 将 是 在 motorola/国家的 microwire 模式. 这个 管脚

有 非 函数 (nc) 在 st-总线 模式.

23 25 19 DS

[P]

SCLK

[S]

CSTi1

[ST]

数据 strobe (输入)

: 这个 输入 是 这 起作用的 低 数据 strobe 的 这 并行的

处理器 接口.

串行 时钟 (输入):

这个 是 使用 在 串行 控制 模式 至 时钟 串行 数据 在

和 输出 的 这 mt9079 在 rxd 和 sio. 如果 sclk 是 高 当 cs

变得 低, 这

设备 将 是 在 intel 模式; 如果 sclk 是 低 当 cs

变得 低, 它 将 是 在

motorola/国家的 microwire 模式.

控制 st-总线 一个 (输入)

: 一个 2.048 mbit/s 串行 控制 stream 这个 包含

这 每 timeslot 控制 程序编制.

24 26 20 C4i

/C2i

4.096 mhz 和 2.048 mhz 系统 时钟 (输入):

这个 是 主控 时钟 为 这 串行

pcm 数据 和 st-总线 sections 的 这 mt9079. 这 mt9079 automatically 发现

whether 一个 4.096 或者 2.048 mhz 时钟 是 正在 使用. 看 图示 22 为 定时

信息.

25 27 21 E2i

2.048 mhz 提取 时钟 (输入):

这个 时钟 是 提取 从 这 received

信号. 它的 rising 边缘 是 使用 内部 至 时钟 在 数据 received 在 rxa 和 rxb.

看 图示 29.

-2822 NC

非 连接.

26 29 23 RxB

receive b (输入):

received 分割 阶段 单极的 信号 解码 从 一个 双极 线条

接受者. receives rz 和 nrz 双极 信号. 看 计算数量 29 和 31.

27 30 24 RxA

receive 一个 (输入):

received 分割 阶段 单极的 信号 解码 从 一个 双极 线条

接受者. receives rz 和 nrz 双极 信号. 看 figurs 29 和 31.

28 31 25 F0i

框架 脉冲波 (输入):

这个 是 这 st-总线 框架 同步 信号 这个

delimits 这 32 频道 框架 的 所有 st-总线 streams, 作 好 作 dsti 和 dsto 在

所有 模式.

29 32 26 E8Ko

提取 8 khz 时钟 (输出):

一个 8 khz 信号 发生 用 dividing 这

提取 2.048 mhz 时钟 (e2i) 用 256 和 aligning 它 和 这 received pcm 30

框架. 这 8 khz 信号 能 是 使用 至 同步 这 系统 时钟 和 这

提取 2.048 mhz 时钟. e8ko 是 高 当 8ksel=0. 看 图示 27.

30 33 27 DSTi

数据 st-总线 (输入).

一个 2.048 mbit/s 串行 stream 这个 包含 这 30 pcm 或者

数据 途径 至 是 transmitted 在 这 pcm 30 线条. 看 图示 4a.

管脚 描述 (持续)

管脚 #

名字 描述 (看 注释 1, 2 和 3)

插件 PLCC QFP