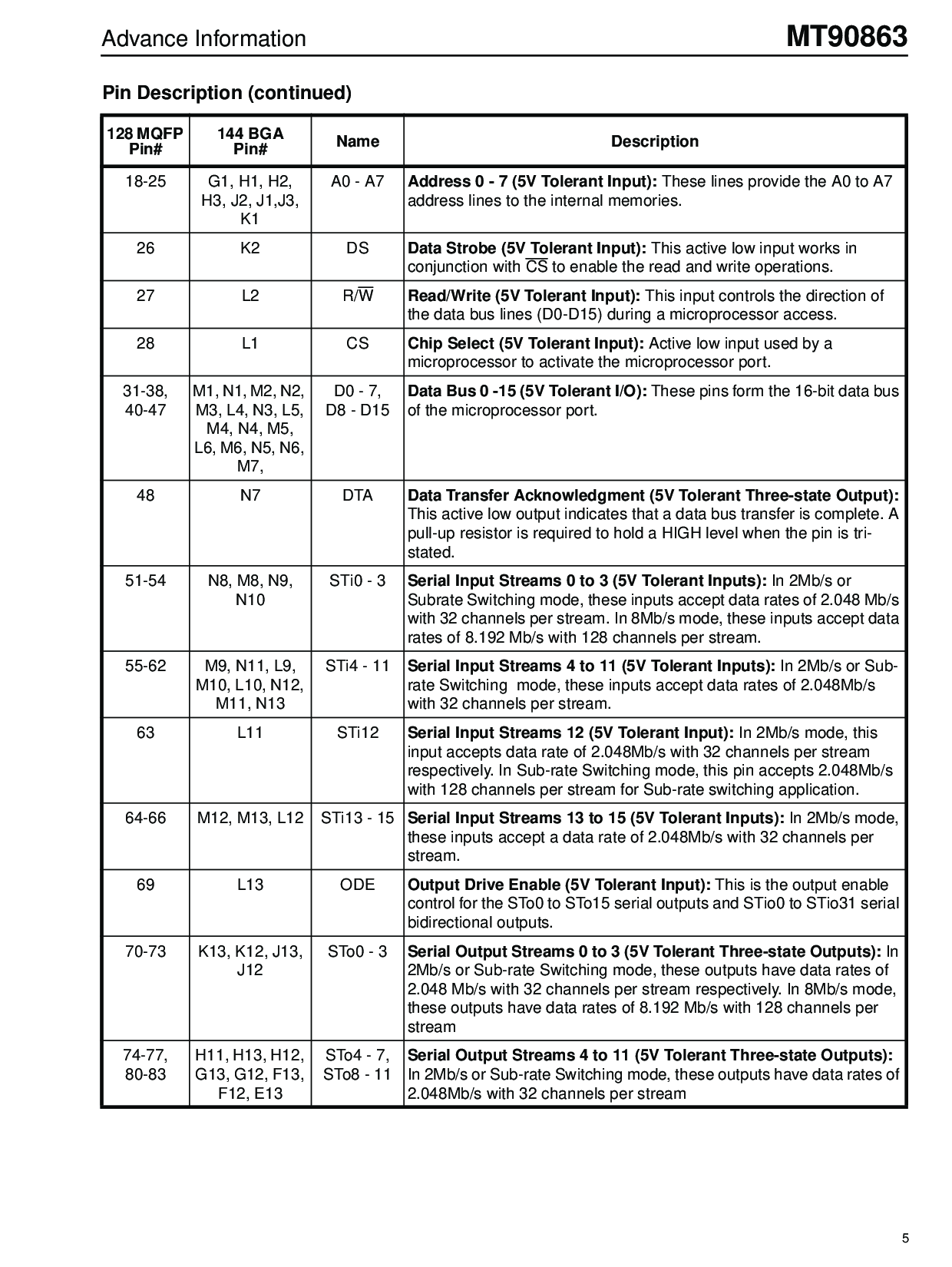

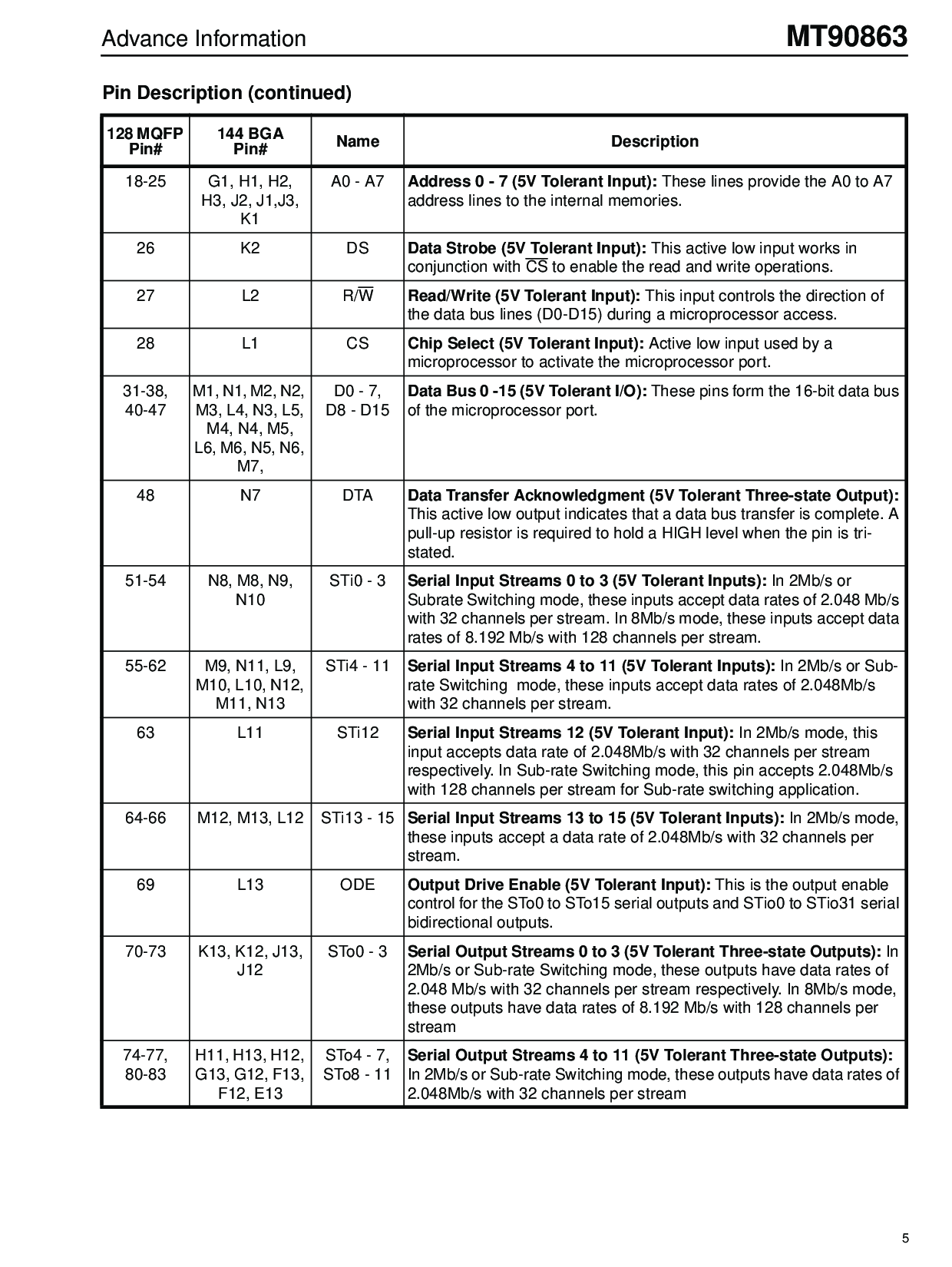

进步 信息

MT90863

5

18-25 g1, h1, h2,

h3, j2, j1,j3,

K1

a0 - a7

地址 0 - 7 (5v tolerant 输入):

这些 线条 提供 这 a0 至 a7

地址 线条 至 这 内部的 memories.

26 K2 DS

数据 strobe (5v tolerant 输入):

这个 起作用的 低 输入 工作 在

conjunction 和 cs 至 使能 这 读 和 写 行动.

27 L2 r/w

读/写 (5v tolerant 输入):

这个 输入 控制 这 方向 的

这 数据 总线 线条 (d0-d15) 在 一个 微处理器 进入.

28 L1 CS

碎片 选择 (5v tolerant 输入):

起作用的 低 输入 使用 用 一个

微处理器 至 活动 这 微处理器 端口.

31-38,

40-47

m1, n1, m2, n2,

m3, l4, n3, l5,

m4, n4, m5,

l6, m6, n5, n6,

m7,

d0 - 7,

d8 - d15

数据 总线 0 -15 (5v tolerant i/o):

这些 管脚 表格 这 16-位 数据 总线

的 这 微处理器 端口.

48 N7 DTA

数据 转移 承认 (5v tolerant 三-状态 输出):

这个 起作用的 低 输出 indicates 那 一个 数据 总线 转移 是 完全. 一个

拉-向上 电阻 是 必需的 至 支撑 一个 高 水平的 当 这 管脚 是 触发-

陈述.

51-54 n8, m8, n9,

N10

sti0 - 3

串行 输入 streams 0 至 3 (5v tolerant 输入):

在 2mb/s 或者

subrate 切换 模式, 这些 输入 接受 数据 比率 的 2.048 mb/s

和 32 途径 每 stream. 在 8mb/s 模式, 这些 输入 接受 数据

比率 的 8.192 mb/s 和 128 途径 每 stream.

55-62 m9, n11, l9,

m10, l10, n12,

m11, n13

sti4 - 11

串行 输入 streams 4 至 11 (5v tolerant 输入):

在 2mb/s 或者 sub-

比率 切换 模式, 这些 输入 接受 数据 比率 的 2.048mb/s

和 32 途径 每 stream.

63 L11 STi12

串行 输入 streams 12 (5v tolerant 输入):

在 2mb/s 模式, 这个

输入 accepts 数据 比率 的 2.048mb/s 和 32 途径 每 stream

各自. 在 sub-比率 切换 模式, 这个 管脚 accepts 2.048mb/s

和 128 途径 每 stream 为 sub-比率 切换 应用.

64-66 m12, m13, l12 sti13 - 15

串行 输入 streams 13 至 15 (5v tolerant 输入):

在 2mb/s 模式,

这些 输入 接受 一个 数据 比率 的 2.048mb/s 和 32 途径 每

stream.

69 L13 ODE

输出 驱动 使能 (5v tolerant 输入):

这个 是 这 输出 使能

控制 为 这 sto0 至 sto15 串行 输出 和 stio0 至 stio31 串行

双向的 输出.

70-73 k13, k12, j13,

J12

sto0 - 3

串行 输出 streams 0 至 3 (5v tolerant 三-状态 输出):

在

2mb/s 或者 sub-比率 切换 模式, 这些 输出 有 数据 比率 的

2.048 mb/s 和 32 途径 每 stream 各自. 在 8mb/s mode,

这些 输出 有 数据 比率 的 8.192 mb/s 和 128 途径 每

stream

74-77,

80-83

h11, h13, h12,

g13, g12, f13,

f12, e13

sto4 - 7,

sto8 - 11

串行 输出 streams 4 至 11 (5v tolerant 三-状态 输出):

在 2mb/s 或者 sub-比率 切换 模式, 这些 输出 有 数据 比率 的

2.048mb/s 和 32 途径 每 stream

管脚 描述 (持续)

128 mqfp

Pin#

144 bga

Pin#

名字 描述