MX66C1024

7

p/n ds00040

rev. 1.0, 十一月 1999

macronix america inc., usa 1338 ridder 园区 dr., san jose, ca 95131

电话 (408)453-8088 传真 (408)451-0876 http: www.macronix.com

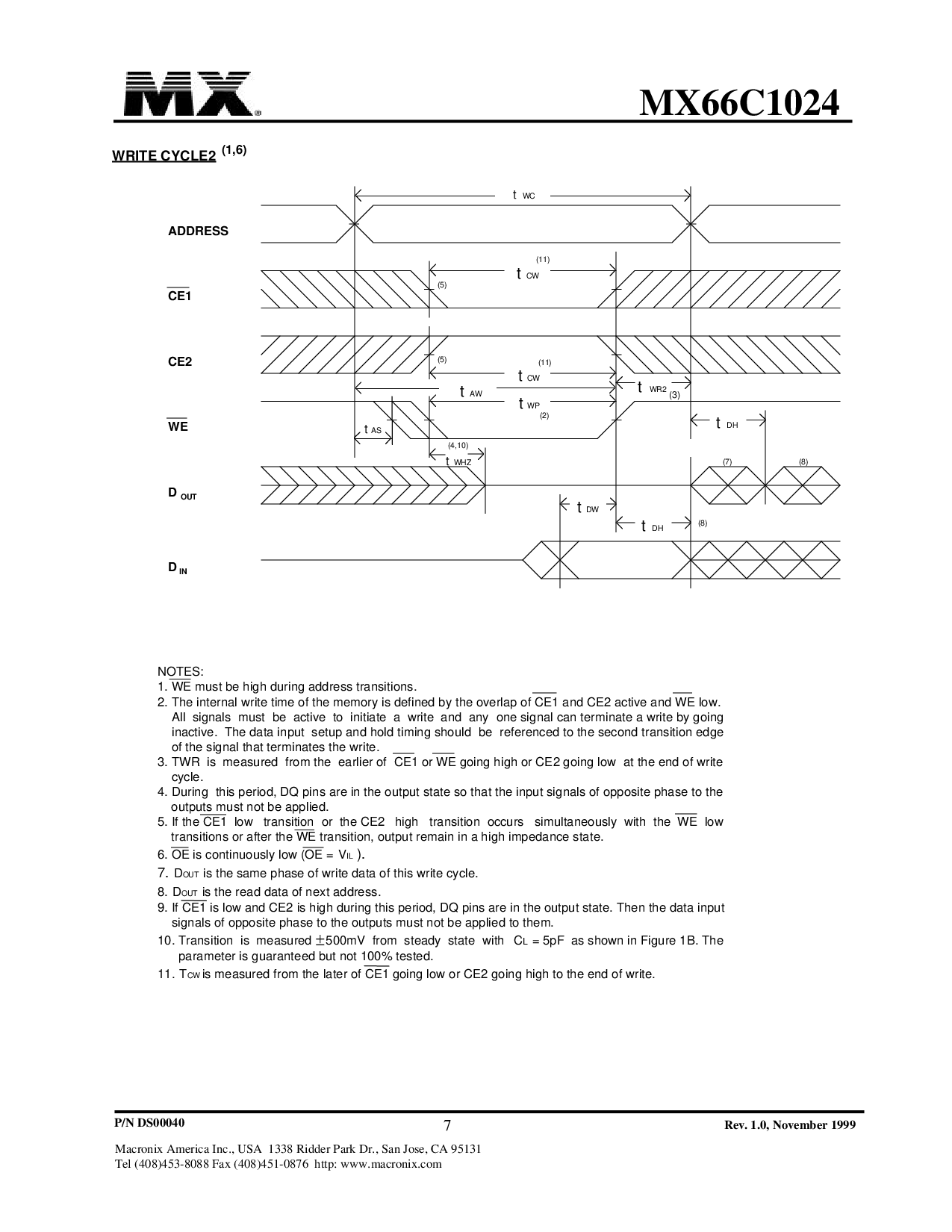

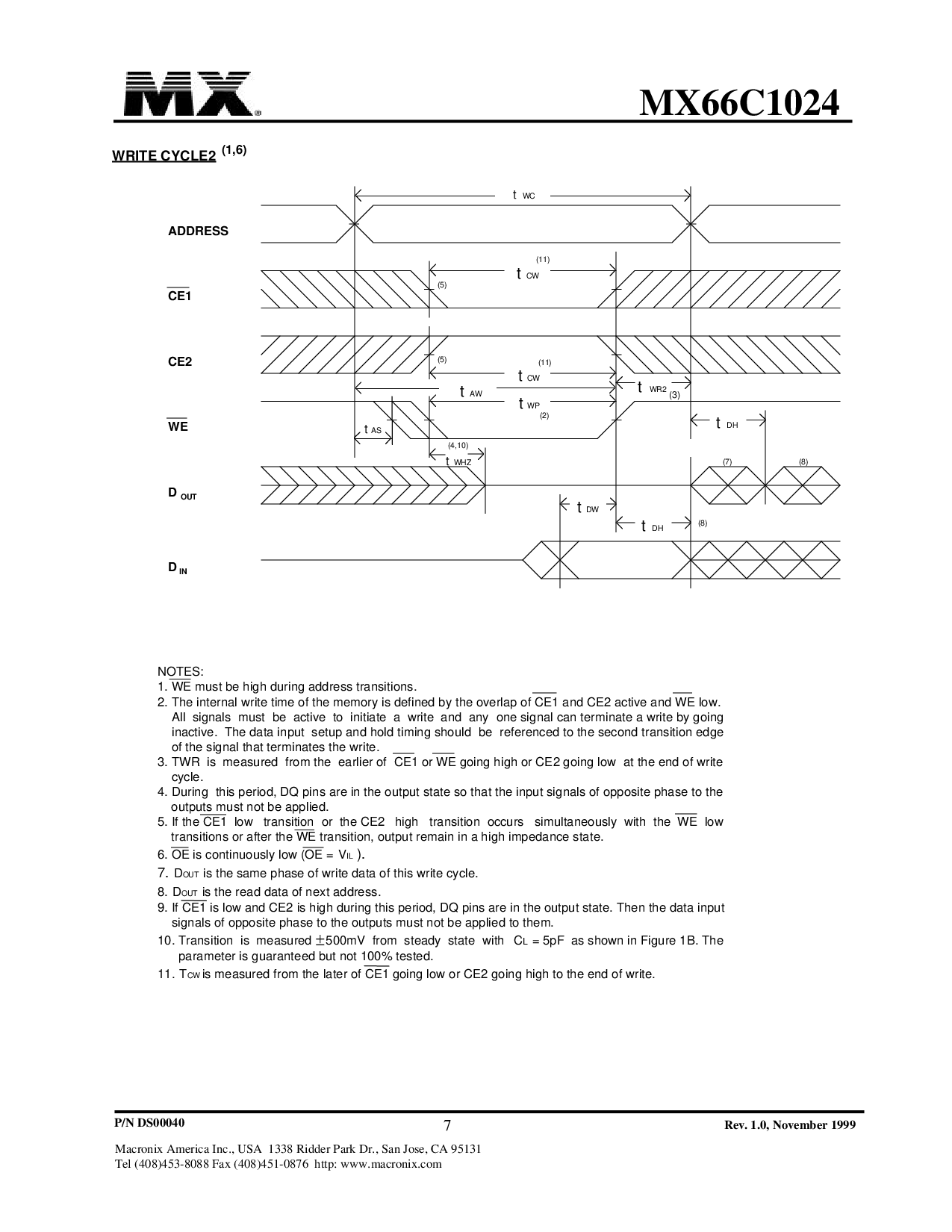

注释:

1. 我们 必须 是 高 在 地址 transitions.

2. 这 内部的 写 时间 的 这 记忆 是 定义 用 这 overlap 的 ce1 和 ce2 起作用的 和 我们 低.

所有信号必须 是 起作用的 至 initiate 一个 写 和 任何一个 信号 能 terminate 一个 写 用 going

inactive.这 数据 输入 建制 和 支撑 定时 应当是关联 至 这 第二 转变 边缘

的 这 信号 那 terminates 这 写.

3. twr 是 量过的从 这早期 的ce1 或者 我们 going 高 或者 ce2 going 低在 这 终止 的 写

循环.

4. 在这个 时期, dq 管脚 是 在 这 输出 状态 所以 那 这 输入 信号 的 opposite 阶段 至 这

输出 必须 不 是 应用.

5. 如果 这 ce1 低 转变或者 这 ce2 高转变occurs同时发生地 和 这 我们 低

transitions 或者 之后 这 我们 转变, 输出 仍然是 在 一个 高 阻抗 状态.

6. oe 是 continuously 低 (oe =VIL).

7.D输出是 这 一样 阶段 的 写 数据 的 这个 写 循环.

8.D输出是 这 读 数据 的 next 地址.

9. 如果 ce1 是 低 和 ce2 是 高 在 这个 时期, dq 管脚 是 在 这 输出 状态. 然后 这 数据 输入

信号 的 opposite 阶段 至 这 输出 必须 不 是 应用 至 它们.

10. 转变 是 量过的 500mv 从 稳步的 状态 和CL= 5pf 作 显示 在 图示 1b. 这

参数 是 有保证的 但是 不 100% 测试.

11.TCW是 量过的 从 这 后来的 的 ce1 going 低 或者 ce2 going 高 至 这 终止 的 写.

写 cycle2

(1,6)

±

tWC

tCW

(11)

(11)

tCW

(2)

tWP

tAW

tWHZ

(4,10)

t作

tWR2

(3)

tDH

tDW

D

在

D

输出

我们

CE2

CE1

地址

(5)

(5)

tDH

(7) (8)

(8)