飞利浦 半导体 产品 规格

80c51/87c51/80c31

80c51 8-位 微控制器 家族

4k/128 otp/只读存储器/romless, 低 电压 (2.7v–5.5v),

低 电源, 高 速 (33 mhz)

2000 jan 20

6

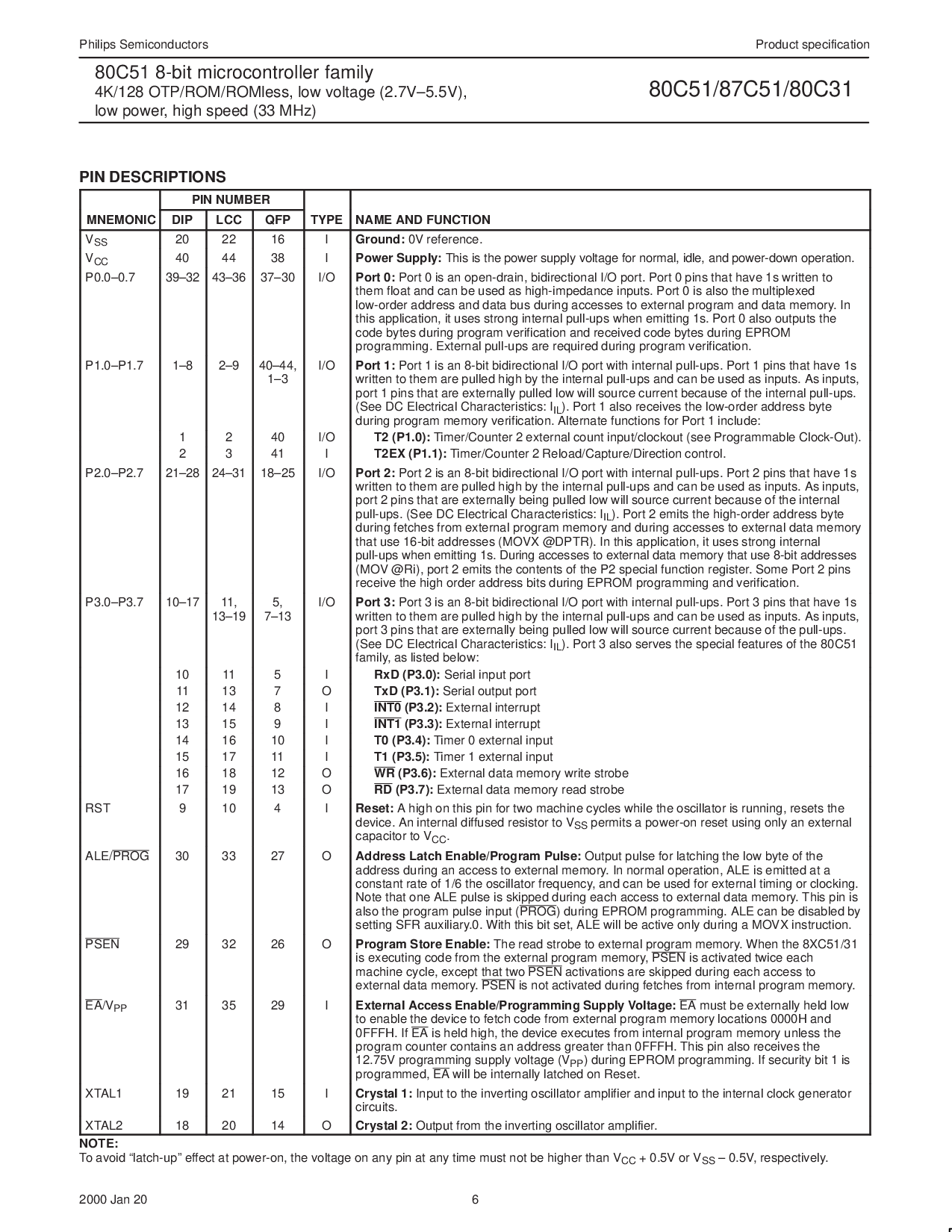

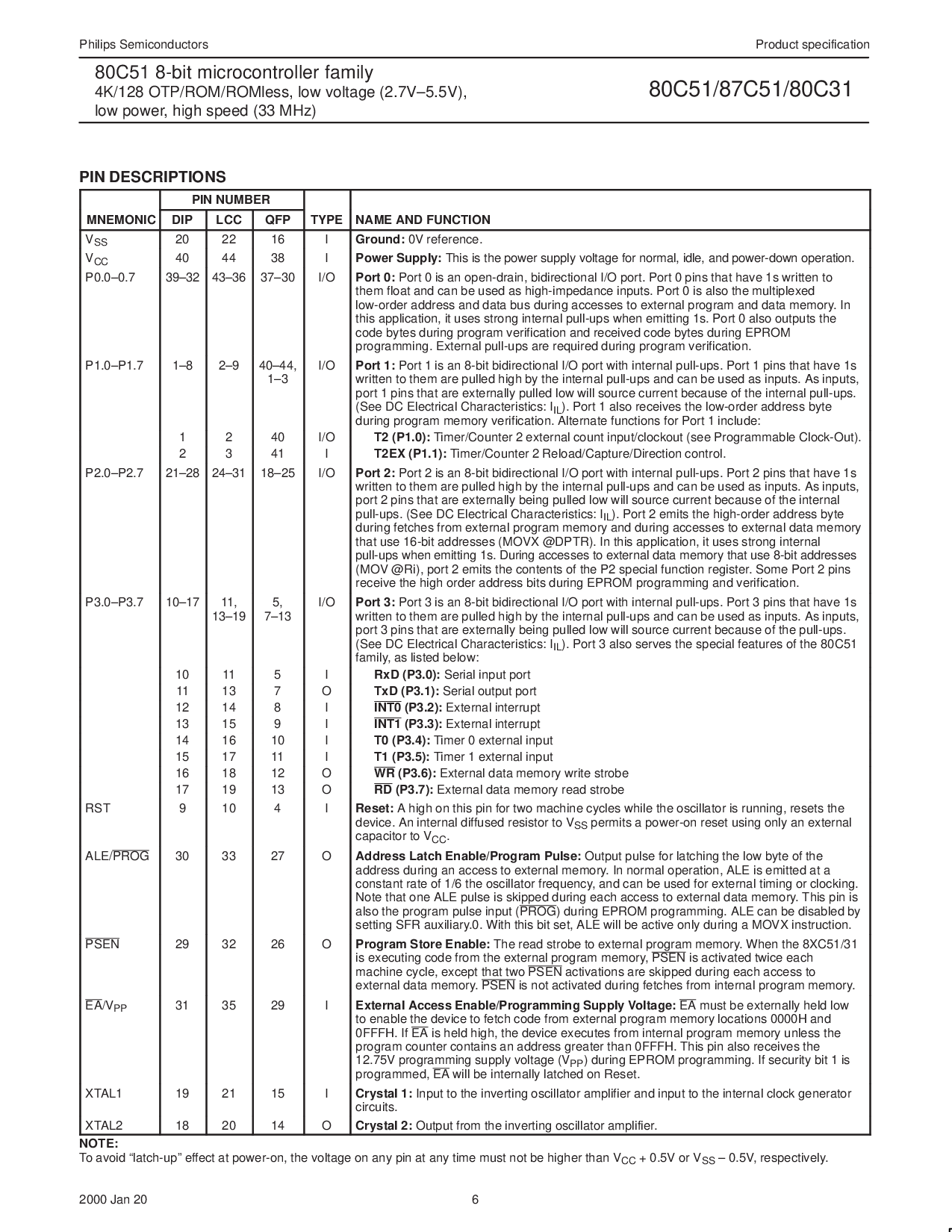

管脚 描述

管脚 号码

MNEMONIC 插件 LCC QFP 类型 名字 和 函数

V

SS

20 22 16 I

地面:

0v 涉及.

V

CC

40 44 38 I

电源 供应:

这个 是 这 电源 供应 电压 为 正常的, 空闲, 和 电源-向下 运作.

p0.0–0.7 39–32 43–36 37–30 i/o

端口 0:

端口 0 是 一个 打开-流, 双向的 i/o 端口. 端口 0 管脚 那 有 1s 写 至

它们 float 和 能 是 使用 作 高-阻抗 输入. 端口 0 是 也 这 多路复用

低-顺序 地址 和 数据 总线 在 accesses 至 外部 程序 和 数据 记忆. 在

这个 应用, 它 使用 强 内部的 拉-ups 当 发出 1s. 端口 0 也 输出 这

代号 字节 在 程序 verification 和 received 代号 字节 在 非易失存储器

程序编制. 外部 拉-ups 是 必需的 在 程序 verification.

p1.0–p1.7 1–8 2–9 40–44,

1–3

i/o

端口 1:

端口 1 是 一个 8-位 双向的 i/o 端口 和 内部的 拉-ups. 端口 1 管脚 那 有 1s

写 至 它们 是 牵引的 高 用 这 内部的 拉-ups 和 能 是 使用 作 输入. 作 输入,

端口 1 管脚 那 是 externally 牵引的 低 将 源 电流 因为 的 这 内部的 拉-ups.

(看 直流 电的 特性: i

IL

). 端口 1 也 receives 这 低-顺序 地址 字节

在 程序 记忆 verification. alternate 功能 为 端口 1 包含:

1 2 40 i/o

t2 (p1.0):

计时器/计数器 2 外部 计数 输入/clockout (看 可编程序的 时钟-输出).

2 3 41 I

t2ex (p1.1):

计时器/计数器 2 再装填/俘获/方向 控制.

p2.0–p2.7 21–28 24–31 18–25 i/o

端口 2:

端口 2 是 一个 8-位 双向的 i/o 端口 和 内部的 拉-ups. 端口 2 管脚 那 有 1s

写 至 它们 是 牵引的 高 用 这 内部的 拉-ups 和 能 是 使用 作 输入. 作 输入,

端口 2 管脚 那 是 externally 正在 牵引的 低 将 源 电流 因为 的 这 内部的

拉-ups. (看 直流 电的 特性: i

IL

). 端口 2 emits 这 高-顺序 地址 字节

在 fetches 从 外部 程序 记忆 和 在 accesses 至 外部 数据 记忆

那 使用 16-位 地址 (movx @dptr). 在 这个 应用, 它 使用 强 内部的

拉-ups 当 发出 1s. 在 accesses 至 外部 数据 记忆 那 使用 8-位 地址

(mov @ri), 端口 2 emits 这 内容 的 这 p2 特定的 函数 寄存器. 一些 端口 2 管脚

receive 这 高 顺序 地址 位 在 非易失存储器 程序编制 和 verification.

p3.0–p3.7 10–17 11,

13–19

5,

7–13

i/o

端口 3:

端口 3 是 一个 8-位 双向的 i/o 端口 和 内部的 拉-ups. 端口 3 管脚 那 有 1s

写 至 它们 是 牵引的 高 用 这 内部的 拉-ups 和 能 是 使用 作 输入. 作 输入,

端口 3 管脚 那 是 externally 正在 牵引的 低 将 源 电流 因为 的 这 拉-ups.

(看 直流 电的 特性: i

IL

). 端口 3 也 serves 这 特定的 特性 的 这 80c51

家族, 作 列表 在下:

10 11 5 I

rxd (p3.0):

串行 输入 端口

11 13 7 O

txd (p3.1):

串行 输出 端口

12 14 8 I

INT0(p3.2):

外部 中断

13 15 9 I

INT1(p3.3):

外部 中断

14 16 10 I

t0 (p3.4):

计时器 0 外部 输入

15 17 11 I

t1 (p3.5):

计时器 1 外部 输入

16 18 12 O

WR(p3.6):

外部 数据 记忆 写 strobe

17 19 13 O

RD(p3.7):

外部 数据 记忆 读 strobe

RST 9 10 4 I

重置:

一个 高 在 这个 管脚 为 二 机器 循环 当 这 振荡器 是 运动, resets 这

设备. 一个 内部的 diffused 电阻 至 v

SS

准许 一个 电源-在 重置 使用 仅有的 一个 外部

电容 至 v

CC

.

ale/prog 30 33 27 O

地址 获得 使能/程序 脉冲波:

输出 脉冲波 为 闭锁 这 低 字节 的 这

地址 在 一个 进入 至 外部 记忆. 在 正常的 运作, ale 是 emitted 在 一个

常量 比率 的 1/6 这 振荡器 频率, 和 能 是 使用 为 外部 定时 或者 clocking.

便条 那 一个 ale 脉冲波 是 skipped 在 各自 进入 至 外部 数据 记忆. 这个 管脚 是

也 这 程序 脉冲波 输入 (prog

) 在 非易失存储器 程序编制. ale 能 是 无能 用

设置 sfr auxiliary.0. 和 这个 位 设置, ale 将 是 起作用的 仅有的 在 一个 movx 操作指南.

PSEN 29 32 26 O

程序 store 使能:

这 读 strobe 至 外部 程序 记忆. 当 这 8xc51/31

是 executing 代号 从 这 外部 程序 记忆, psen是 使活动 两次 各自

机器 循环, 除了 那 二 psen activations 是 skipped 在 各自 进入 至

外部 数据 记忆. psen是 不 使活动 在 fetches 从 内部的 程序 记忆.

ea/v

PP

31 35 29 I

外部 进入 使能/程序编制 供应 电压:

EA必须 是 externally 使保持 低

至 使能 这 设备 至 fetch 代号 从 外部 程序 记忆 locations 0000h 和

0fffh. 如果 ea

是 使保持 高, 这 设备 executes 从 内部的 程序 记忆 除非 这

程序 计数器 包含 一个 地址 更好 比 0fffh. 这个 管脚 也 receives 这

12.75v 程序编制 供应 电压 (v

PP

) 在 非易失存储器 程序编制. 如果 安全 位 1 是

编写程序, ea将 是 内部 latched 在 重置.

XTAL1 19 21 15 I

结晶 1:

输入 至 这 反相的 振荡器 放大器 和 输入 至 这 内部的 时钟 发生器

电路.

XTAL2 18 20 14 O

结晶 2:

输出 从 这 反相的 振荡器 放大器.

便条:

至 避免 “latch-up” 效应 在 电源-在, 这 电压 在 任何 管脚 在 任何 时间 必须 不 是 高等级的 比 v

CC

+ 0.5v 或者 v

SS

– 0.5v, 各自.