9397 750 14655 © koninklijke 飞利浦 electronics n.v. 2005. 所有 权利 保留.

产品 数据 薄板 rev. 02 — 11 april 2005 9 的 58

飞利浦 半导体

p89lpc9102/9103/9107

8-位 微控制器 和 二-时钟 accelerated 80c51 核心

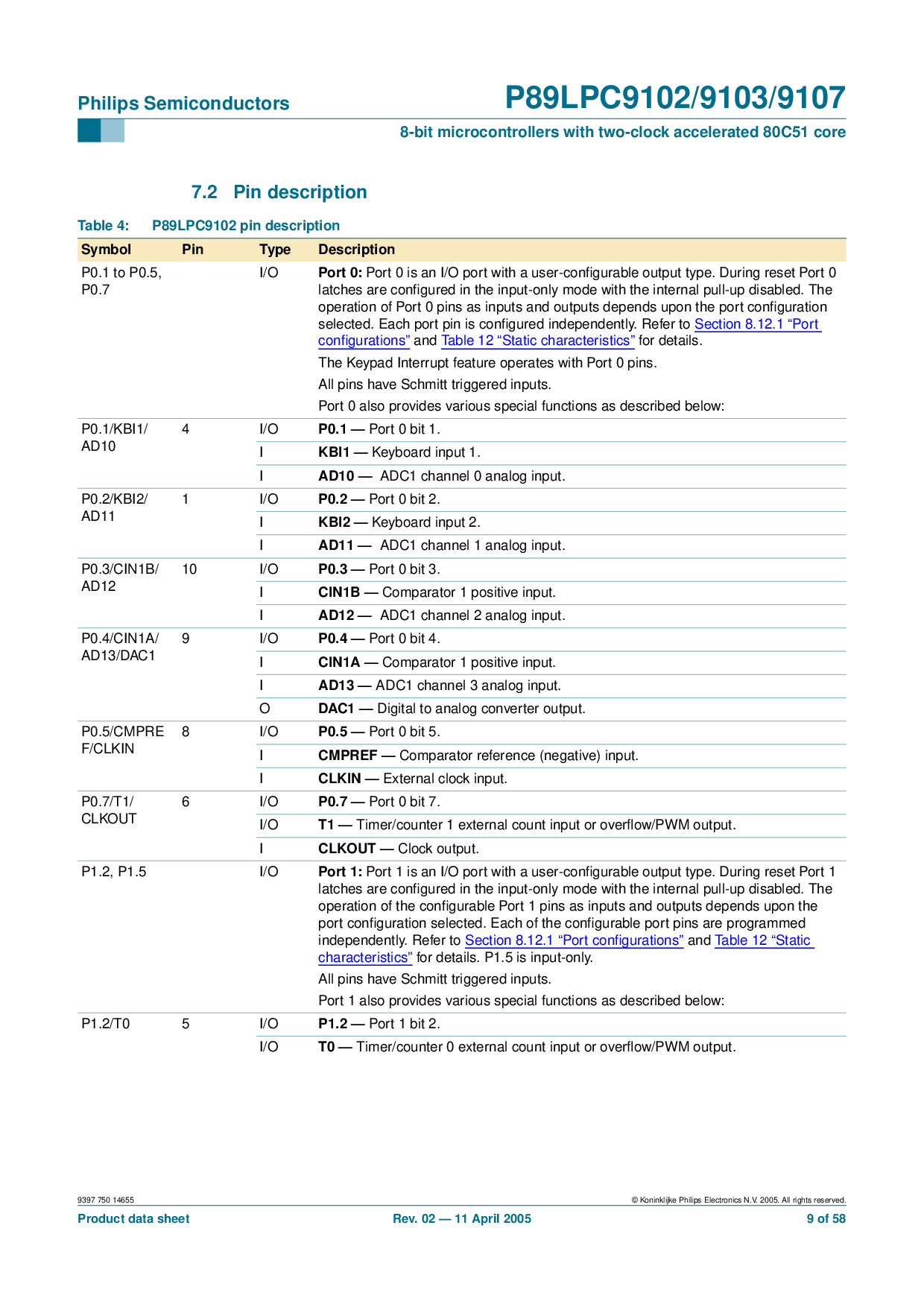

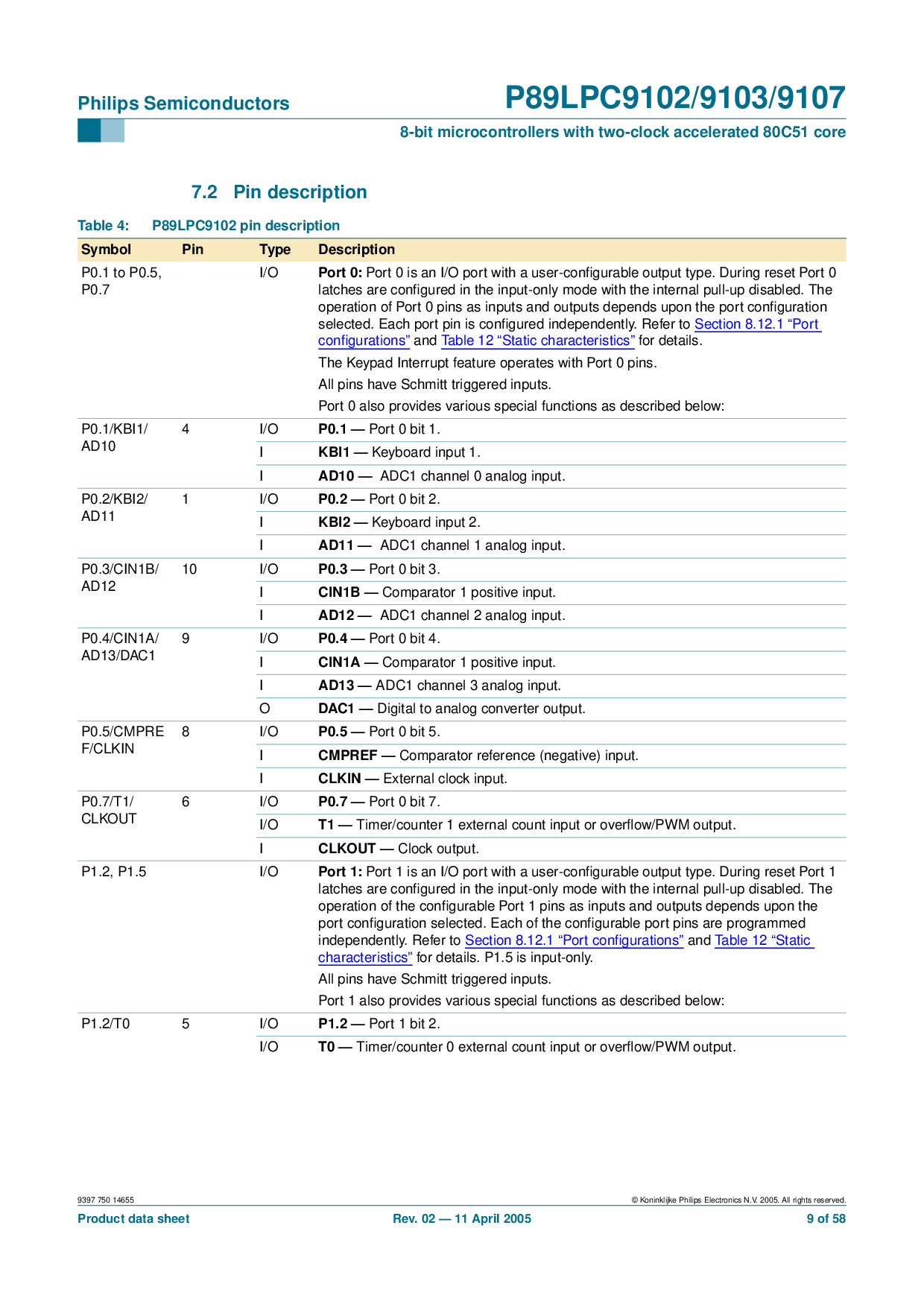

7.2 管脚 描述

表格 4: p89lpc9102 管脚 描述

标识 管脚 类型 描述

p0.1 至 p0.5,

p0.7

i/o

Port 0:

端口 0 是 一个 i/o 端口 和 一个 用户-configurable 输出 类型. 在 重置 端口 0

latches 是 configured 在 这 输入-仅有的 模式 和 这 内部的 拉-向上 无能. 这

运作 的 端口 0 管脚 作 输入 和 输出 取决于 在之上 这 端口 configuration

选择. 各自 端口 管脚 是 configured independently. 谈及 至

部分 8.12.1 “port

configurations”和 表格 12 “static characteristics”为 详细信息.

这 keypad 中断 特性 运作 和 端口 0 管脚.

所有 管脚 有 施密特 triggered 输入.

端口 0 也 提供 各种各样的 特定的 功能 作 描述 在下:

p0.1/kbi1/

AD10

4 i/o

p0.1 —

端口 0 位 1.

I

kbi1 —

键盘 输入 1.

I

ad10 —

adc1 频道 0 相似物 输入.

p0.2/kbi2/

AD11

1 i/o

p0.2 —

端口 0 位 2.

I

kbi2 —

键盘 输入 2.

I

ad11 —

adc1 频道 1 相似物 输入.

p0.3/cin1b/

AD12

10 i/o

p0.3 —

端口 0 位 3.

I

cin1b —

比较器 1 积极的 输入.

I

ad12 —

adc1 频道 2 相似物 输入.

p0.4/cin1a/

ad13/dac1

9 i/o

p0.4 —

端口 0 位 4.

I

cin1a —

比较器 1 积极的 输入.

I

ad13 —

adc1 频道 3 相似物 输入.

O

dac1 —

数字的 至 相似物 转换器 输出.

p0.5/cmpre

f/clkin

8 i/o

p0.5 —

端口 0 位 5.

I

cmpref —

比较器 涉及 (负的) 输入.

I

clkin —

外部 时钟 输入.

p0.7/t1/

CLKOUT

6 i/o

p0.7 —

端口 0 位 7.

i/o

t1 —

计时器/计数器 1 外部 计数 输入 或者 overflow/pwm 输出.

I

clkout —

时钟 输出.

p1.2, p1.5 i/o

Port 1:

端口 1 是 一个 i/o 端口 和 一个 用户-configurable 输出 类型. 在 重置 端口 1

latches 是 configured 在 这 输入-仅有的 模式 和 这 内部的 拉-向上 无能. 这

运作 的 这 configurable 端口 1 管脚 作 输入 和 输出 取决于 在之上 这

端口 configuration 选择. 各自 的 这 configurable 端口 管脚 是 编写程序

independently. 谈及 至

部分 8.12.1 “port configurations”和 表格 12 “static

characteristics”为 详细信息. p1.5 是 输入-仅有的.

所有 管脚 有 施密特 triggered 输入.

端口 1 也 提供 各种各样的 特定的 功能 作 描述 在下:

p1.2/t0 5 i/o

p1.2 —

端口 1 位 2.

i/o

t0 —

计时器/计数器 0 外部 计数 输入 或者 overflow/pwm 输出.