sbas323d −六月 2004 − 修订 九月 2005

www.德州仪器.com

3

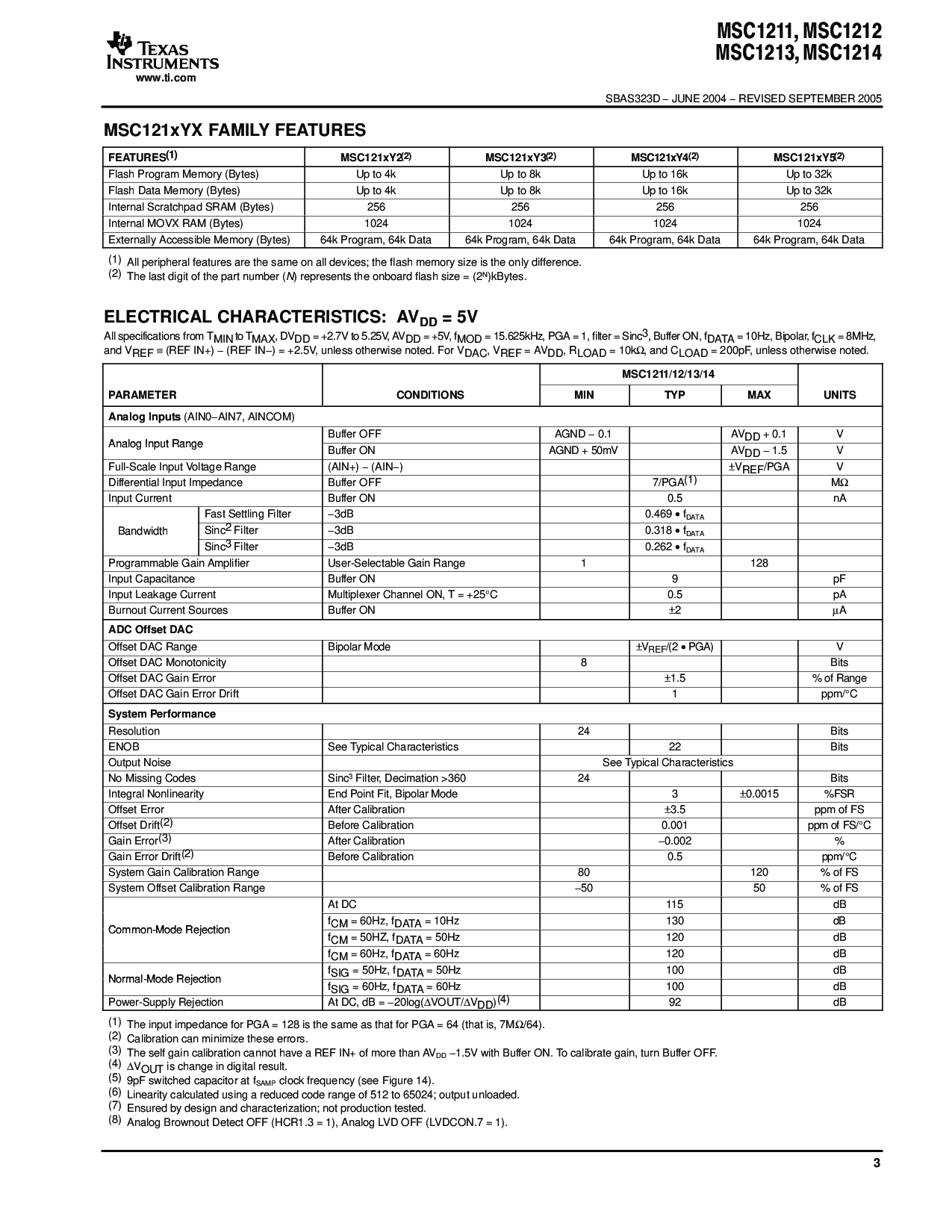

MSC121xYX家族 特性

特性

(1)

MSC121xY2

(2)

MSC121xY3

(2)

MSC121xY4

(2)

MSC121xY5

(2)

flash 程序 记忆 (字节) 向上 至 4k 向上 至 8k 向上 至 16k 向上 至 32k

flash 数据 记忆 (字节) 向上 至 4k 向上 至 8k 向上 至 16k 向上 至 32k

内部的 scratchpad sram (字节) 256 256 256 256

内部的 movx 内存 (字节) 1024 1024 1024 1024

externally accessible 记忆 (字节) 64k 程序, 64k 数据 64k 程序, 64k 数据 64k 程序, 64k 数据 64k 程序, 64k 数据

(1)

所有 附带的 特性 是 这 一样 在 所有 设备; 这 flash 记忆 大小 是这 仅有的 区别.

(2)

这 last 数字 的 这 部分 号码 (

N

) 代表 这 onboard flash 大小 = (2

N

)kbytes.

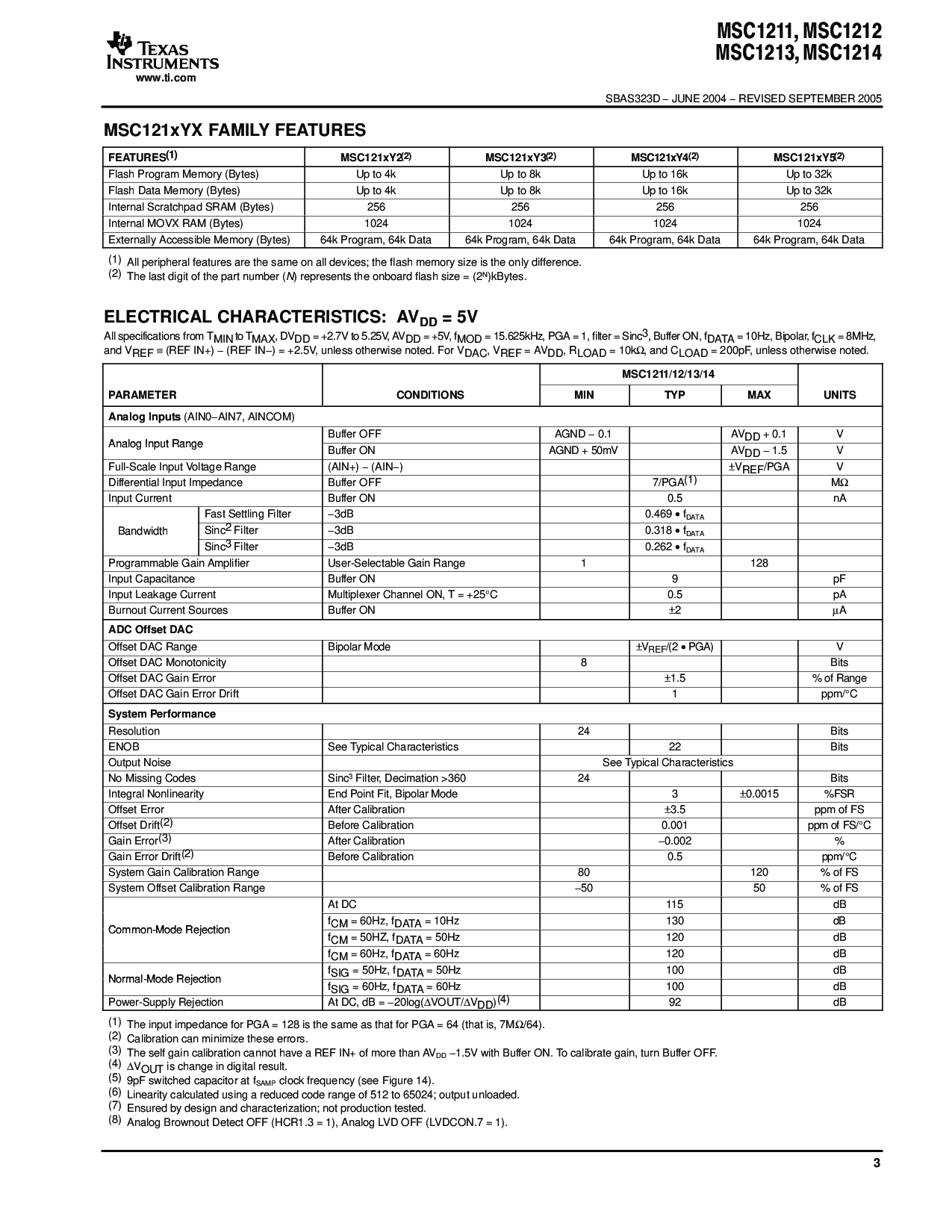

电的 特性: av

DD

= 5v

所有 规格 从 t

最小值

至 t

最大值

, dv

DD

= +2.7v 至 5.25v, av

DD

= +5v, f

MOD

= 15.625khz, pga = 1, 过滤 = sinc

3

, 缓存区 在, f

数据

= 10hz, 双极, f

CLK

= 8mhz,

和 v

REF

≡

(ref in+) − (ref in−) = +2.5v, 除非 否则 noted. 为 v

DAC

, v

REF

= av

DD

, r

加载

= 10k

Ω

, 和 c

加载

= 200pf, 除非 否则 指出.

msc1211/12/13/14

参数 情况 最小值 典型值 最大值 单位

相似物 输入

(ain0−ain7, aincom)

相似物 输入 范围

缓存区 止 agnd − 0.1 AV

DD

+ 0.1 V

相似物 输入 范围

缓存区 在 agnd + 50mv AV

DD

− 1.5 V

全部-规模 输入 电压 范围 (ain+) − (ain−)

±

V

REF

/pga V

差别的 输入 阻抗 缓存区 止 7/pga

(1)

M

Ω

输入 电流 缓存区 在 0.5 nA

快 安排好 过滤 −3dB 0.469

•

f

数据

带宽

Sinc

2

过滤 −3dB 0.318

•

f

数据

带宽

Sinc

3

过滤 −3dB 0.262

•

f

数据

可编程序的 增益 放大器 用户-可选择的 增益 范围 1 128

输入 电容 缓存区 在 9 pF

输入 泄漏 电流 多路调制器 频道 在, t = +25

°

C 0.5 pA

burnout 电流 来源 缓存区 在

±

2

µ

一个

模数转换器 补偿 dac

补偿 dac 范围 双极 模式

±

V

REF

/(2

•

pga) V

补偿 dac monotonicity 8 位

补偿 dac 增益 错误

±

1.5 % 的 范围

补偿 dac 增益 错误 逐渐变化 1 ppm/

°

C

系统 效能

决议 24 位

ENOB 看 典型 特性 22 位

输出 噪音 看 典型 特性

非 missing 代号 Sinc

3

过滤, decimation >360 24 位

integral 非线性 终止 要点 合适, 双极 模式 3

±

0.0015 %FSR

补偿 错误 之后 校准

±

3.5 ppm 的 fs

补偿 逐渐变化

(2)

在之前 校准 0.001 ppm 的 fs/

°

C

增益 错误

(3)

之后 校准 −0.002 %

增益 错误 逐渐变化

(2)

在之前 校准 0.5 ppm/

°

C

系统 增益 校准 范围 80 120 % 的 fs

系统 补偿校准 范围 −50 50 % 的 fs

在 直流 115 dB

一般模式 拒绝

f

CM

= 60hz, f

数据

= 10hz 130 dB

一般模式 拒绝

f

CM

= 50hz, f

数据

= 50hz 120 dB

f

CM

= 60hz, f

数据

= 60hz 120 dB

正常的-模式 拒绝

f

SIG

= 50hz, f

数据

= 50hz 100 dB

正常的-模式 拒绝

f

SIG

= 60hz, f

数据

= 60hz 100 dB

电源-供应 拒绝 在 直流, db = −20log(

∆

vout/

∆

V

DD

)

(4)

92 dB

(1)

这 输入 阻抗 为 pga = 128 是 这 一样 作 那 为 pga = 64 (那 是, 7m

Ω

/64).

(2)

校准 能 降低 这些 errors.

(3)

这 自 增益 校准 不能 有 一个 ref in+ 的 更多 比 av

DD

−1.5v 和 buffer 在. 至 calibrate 增益,转变 缓存区 止.

(4)

∆

V

输出

是 改变 在 数字的 结果.

(5)

9pf 切换 电容 在 f

SAMP

时钟 频率 (看 图示 14).

(6)

线性 计算 使用 一个 减少 代号 范围 的 512 至 65024; 输出 unloaded.

(7)

保证 用 设计 和 描绘; 不 生产 测试.

(8)

相似物 brownout 发现 止 (hcr1.3 = 1), 相似物 lvd 止 (lvdcon.7 = 1).