TLC8652

PC16550D 普遍的 异步的 ReceiverTransmitter 和 FIFOs

六月 1995

PC16550D 普遍的 异步的

ReceiverTransmitter 和 FIFOs

一般 描述

这 PC16550D 是 一个 改进 版本 的 这 原来的 16450

普遍的 异步的 ReceiverTransmitter (uart)

Functionally 完全同样的 至 这 16450 在 powerup (charac-

TER 模式)

这 PC16550D 能 是 放 在 一个 alternate

模式 (先进先出 模式) 至 relieve 这 CPU 的 过度的 软件

overhead

在 这个 模式 内部的 FIFOs 是 使活动 准许 16 字节

(加 3 位 的 错误 数据 每 字节 在 这 RCVR 先进先出) 至 是

贮存 在 两个都 receive 和 transmit modes 所有 这 逻辑 是 在

碎片 至 降低 系统 overhead 和 maximize 系统 ef-

ficiency 二 管脚 功能 有 被 changed 至 准许 sig-

nalling 的 DMA transfers

这 UART 执行 串行-至-并行的 转换 在 数据

characters received 从 一个 附带的 设备 或者 一个 MODEM

和 并行的-至-串行 转换 在 数据 characters re-

ceived 从 这 CPU 这 CPU 能 读 这 完全

状态 的 这 UART 在 任何 时间 在 这 函数的 opera-

tion 状态 信息 reported 包含 这 类型 和 con-

dition 的 这 转移 行动 正在 执行 用 这

UART 作 好 作 任何 错误 情况 (parity overrun fram-

ing 或者 破裂 中断)

这 UART 包含 一个 可编程序的 波特 比率 发生器

那 是 有能力 的 dividing 这 定时 涉及 时钟 输入

用 divisors 的 1 至 (2

16

b

1) 和 producing 一个 16

c

时钟 为

驱动 这 内部的 传输者 logic Provisions 是 也 在-

cluded 至 使用 这个 16

c

时钟 至 驱动 这 接受者 logic 这

UART 有 完全 modem-控制 capability 和 一个 proc-

essor-中断 system 中断 能 是 编写程序 至

这 user’s requirements 降低 这 computing 必需的

至 handle 这 communications link

这 UART 是 fabricated 使用 国家的 Semiconductor’s ad-

vanced M

2

CMOS process

能 也 是 重置 至 16450 模式 下面 软件 control

Note 这个 部分 是 patented

特性

Y

有能力 的 运动 所有 存在 16450 software

Y

管脚 为 管脚 兼容 和 这 存在 16450 除了

为 CSOUT (24) 和 NC (29) 这 former CSOUT 和

NC 管脚 是 TXRDY

和 RXRDY respectively

Y

之后 reset 所有 寄存器 是 完全同样的 至 这 16450 reg-

ister set

Y

在 这 先进先出 模式 传输者 和 接受者 是 各自

缓冲 和 16 字节 FIFO’s 至 减少 这 号码 的

interrrupts 提交 至 这 CPU

Y

Adds 或者 deletes 标准 异步的 交流

位 (start stop 和 parity) 至 或者 从 这 串行 data

Y

支持 和 变换 寄存器 在 这 16450 模式 eliminate

这 需要 为 准确的 同步 在 这 CPU

和 串行 data

Y

Independently 控制 transmit receive 线条 status

和 数据 设置 interrupts

Y

可编程序的 波特 发生器 divides 任何 输入 时钟

by1to(2

16

b

1) 和 发生 这 16

c

clock

Y

独立 接受者 时钟 input

Y

MODEM 控制 功能 (cts RTS DSR DTR RI

和 dcd)

Y

全部地 可编程序的 串行-接口 characteristics

5- 6- 7- 或者 8-位 characters

Even odd 或者 非-parity 位 一代 和 发现

1- 1

- 或者 2-停止 位 一代

波特 一代 (直流 至 15M 波特)

Y

False 开始 位 detection

Y

完全 状态 reporting capabilities

Y

触发-状态

TTL 驱动 为 这 数据 和 控制 buses

Y

线条 破裂 一代 和 detection

Y

内部的 diagnostic capabilities

Loopback 控制 为 communications link 故障

分开

Break parity overrun framing 错误 simulation

Y

全部 prioritized 中断 系统 controls

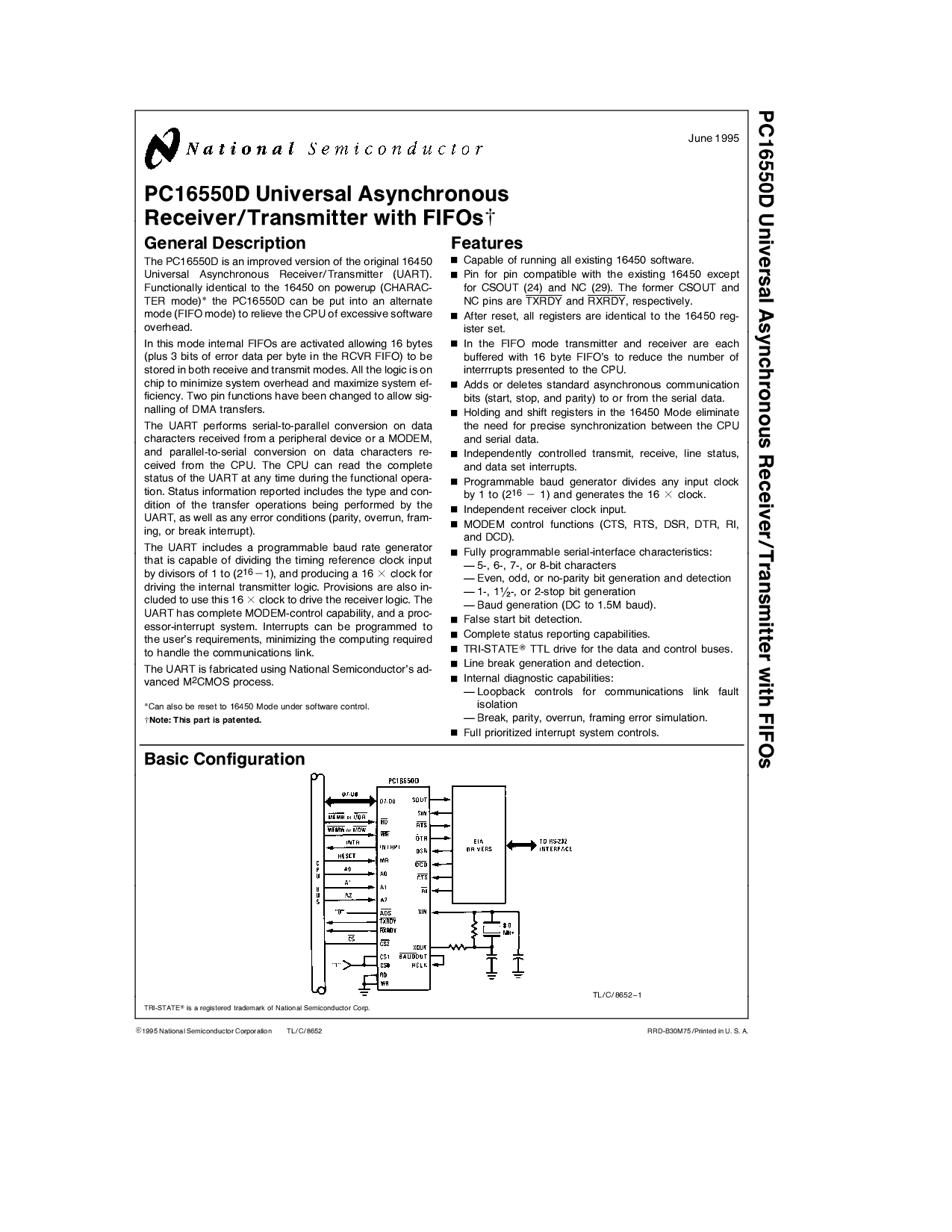

基本 配置

TLC8652–1

触发-状态

是 一个 注册 商标 的 国家的 半导体 Corp

C

1995 国家的 半导体 公司 rrd-b30m75printed 在 U S A