–5–

rev. 一个

3

AD7564

定时 规格

1

(t

一个

= t

最小值

至 t

最大值

除非 否则 指出)

限制 在 限制 在

参数 V

DD

= +3 v 至 +3.6 v V

DD

= +4.75 v 至 +5.25 v 单位 描述

t

1

180 100 ns 最小值 clkin 循环 时间

t

2

80 40 ns 最小值 clkin 高 时间

t

3

80 40 ns 最小值 clkin 低 时间

t

4

50 30 ns 最小值

FSIN

建制 时间

t

5

50 30 ns 最小值 数据 建制 时间

t

6

10 5 ns 最小值 数据 支撑 时间

t

7

125 90 ns 最小值

FSIN

支撑 时间

t

8

2

100 70 ns 最大值 sdout 有效的 之后 clkin 下落 边缘

t

9

80 40 ns 最小值

LDAC

,

CLR

脉冲波 宽度

注释

1

不

生产 测试. 有保证的 用 描绘 在 最初的 产品 释放. 所有 输入 信号 是 指定 和 tr = tf = 5 ns (10% 至 90% 的 V

DD

) 和 安排时间

从 一个 电压 水平的 的 1.6 v 为 一个 v

DD

的 5 v 和 从 一个 电压 水平的 1.35 v 为 一个 v

DD

的 3.3 v.

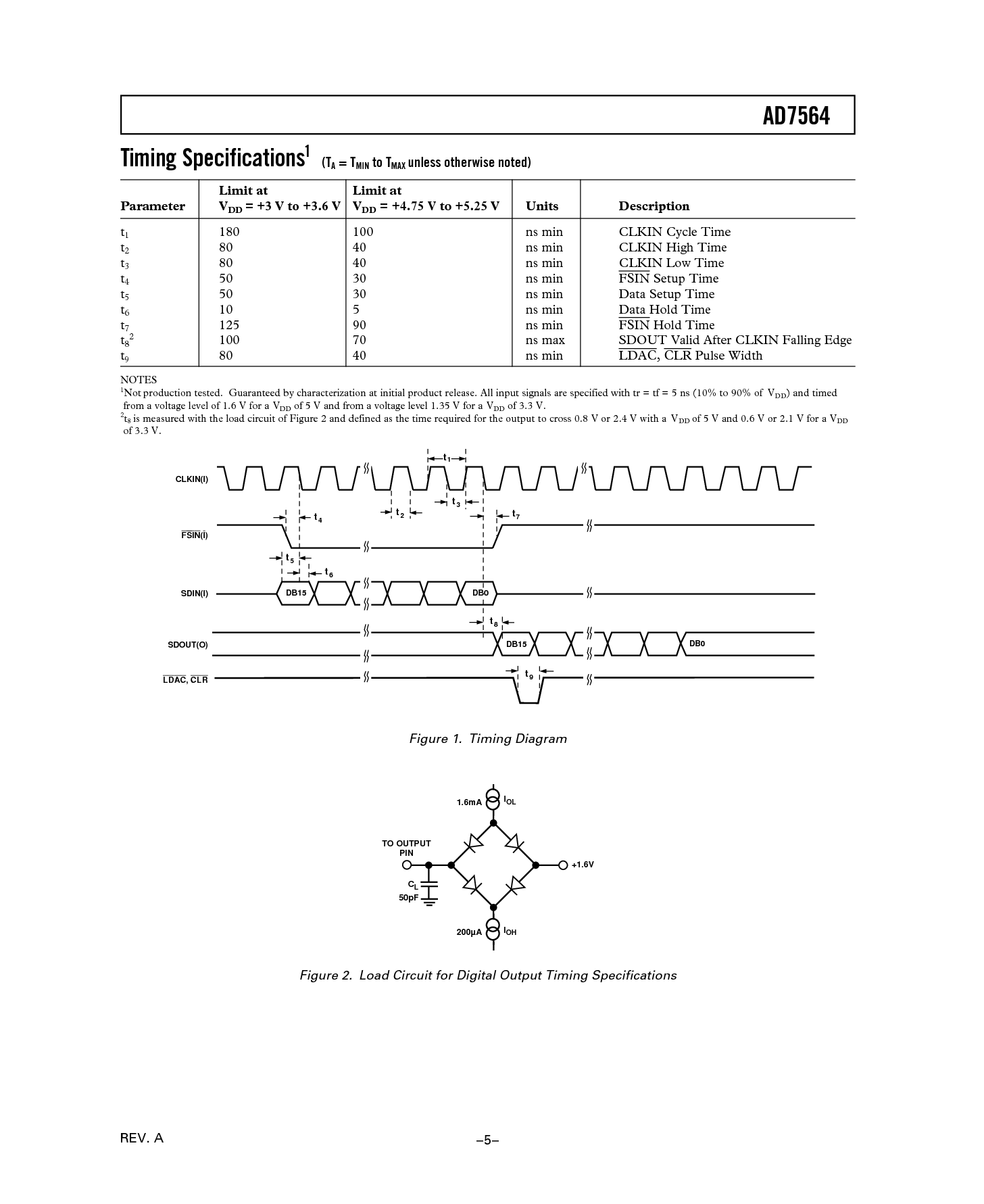

2

t

8

是 量过的 和 这 加载 电路 的 图示 2 和 定义 作 这 时间 必需的 为 这 输出 至 交叉 0.8 v 或者 2.4 v 和 一个 V

DD

的 5 v 和 0.6 v 或者 2.1 v 为 一个 v

DD

的 3.3 v.

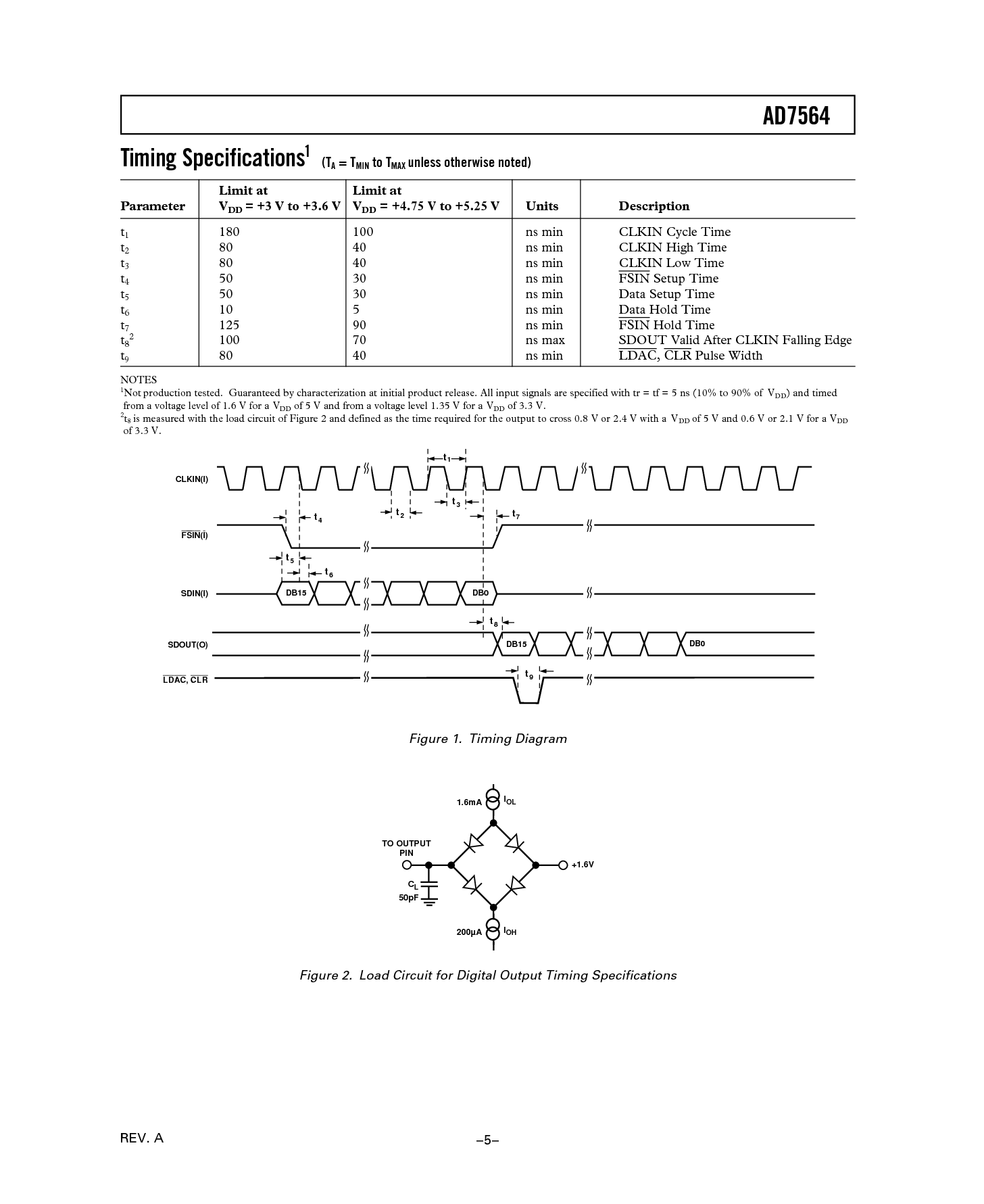

DB15

DB15

DB0

t

2

t

3

t

4

t

5

t

7

t

8

t

9

DB0

t

6

t

1

fsin(i)

clkin(i)

sdin(i)

sdout(o)

ldac, clr

图示 1. 定时 图解

1.6ma

+1.6v

200µA

C

L

50pF

至 输出

管脚

I

OL

I

OH

图示 2. 加载 电路 为 数字的 输出 定时 规格