tps70345, tps70348, tps70351, tps70358, tps70302

双-输出 低-落后 电压 regulators

和 电源 向上 sequencing 为 分割 电压 dsp 系统

SLVS285A

–

8月 2000

–

修订 october 2002

5

邮递 办公室 盒 655303

•

达拉斯市, 德州 75265

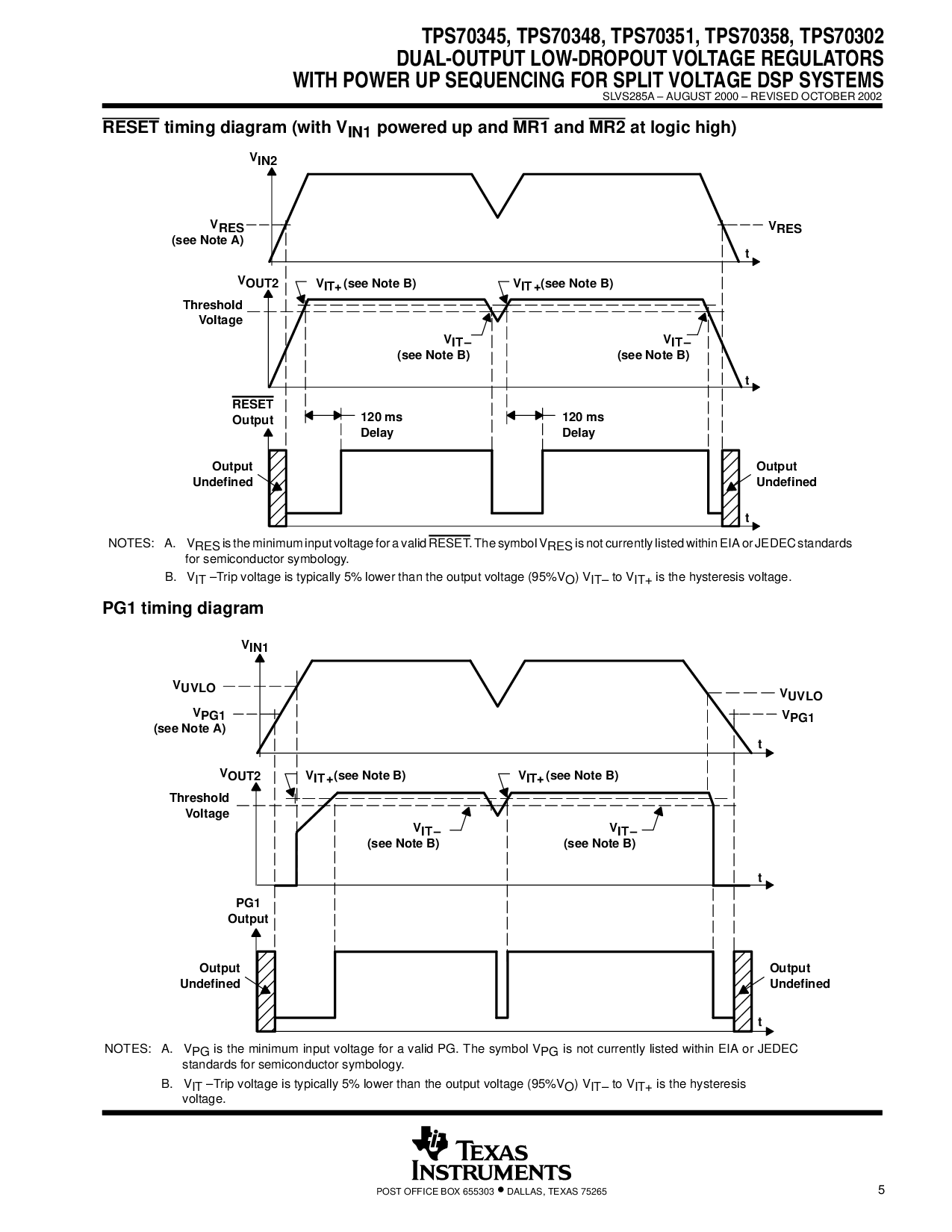

重置定时 图解 (和 v

IN1

powered 向上 和 mr1和 mr2在 逻辑 高)

注释: 一个. V

RES

是 这 最小 输入 电压 为 一个 有效的 重置. 这 标识 v

RES

是 不 目前 列表 在里面 eia 或者 电子元件工业联合会 standards

为 半导体 symbology.

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

V

IN2

V

RES

(看 便条 一个)

V

RES

t

t

t

V

OUT2

门槛

电压

重置

输出

120 ms

延迟

120 ms

延迟

输出

未阐明的

输出

未阐明的

V

它 +

(看 便条 b)

V

它

–

(看 便条 b)

V

IT+

(看 便条 b)

b. V

它

–

trip 电压 是 典型地 5% 更小的 比 这 输出 电压 (95%v

O

) v

它

–

至 v

IT+

是 这 hysteresis 电压.

V

它

–

(看 便条 b)

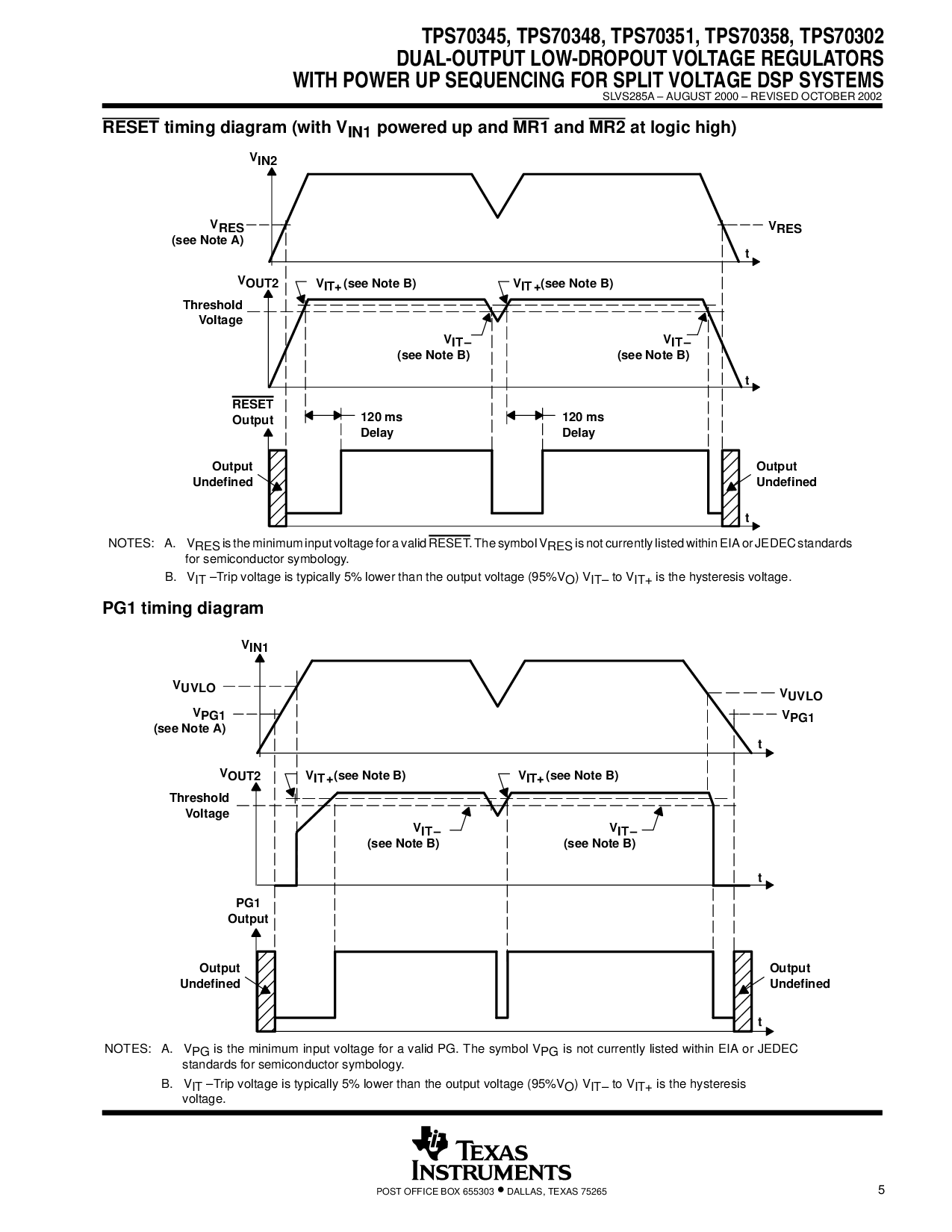

pg1 定时 图解

注释: 一个. V

PG

是 这 最小 输入 电压 为 一个 有效的 pg. 这 标识 v

PG

是 不 目前 列表 在里面 eia 或者 电子元件工业联合会

standards 为 半导体 symbology.

b. V

它

–

trip 电压 是 典型地 5% 更小的 比 这 输出 电压 (95%v

O

) v

它

–

至 v

IT+

是 这 hysteresis

电压.

ÎÎ

ÎÎ

ÎÎ

ÎÎ

ÎÎ

ÎÎ

ÎÎ

ÎÎ

ÎÎ

ÎÎ

V

PG1

t

t

t

门槛

电压

PG1

输出

输出

未阐明的

输出

未阐明的

V

IT+

(看 便条 b)V

它 +

(看 便条 b)

V

IN1

V

OUT2

V

PG1

(看 便条 一个)

V

它

–

(看 便条 b)

V

它

–

(看 便条 b)

V

UVLO

V

UVLO