飞利浦 半导体 rf communications 产品 产品 规格

SA702

分隔 用: 64/65/72 triple modulus 低 电源

ecl 预分频器

六月 17, 1993

4

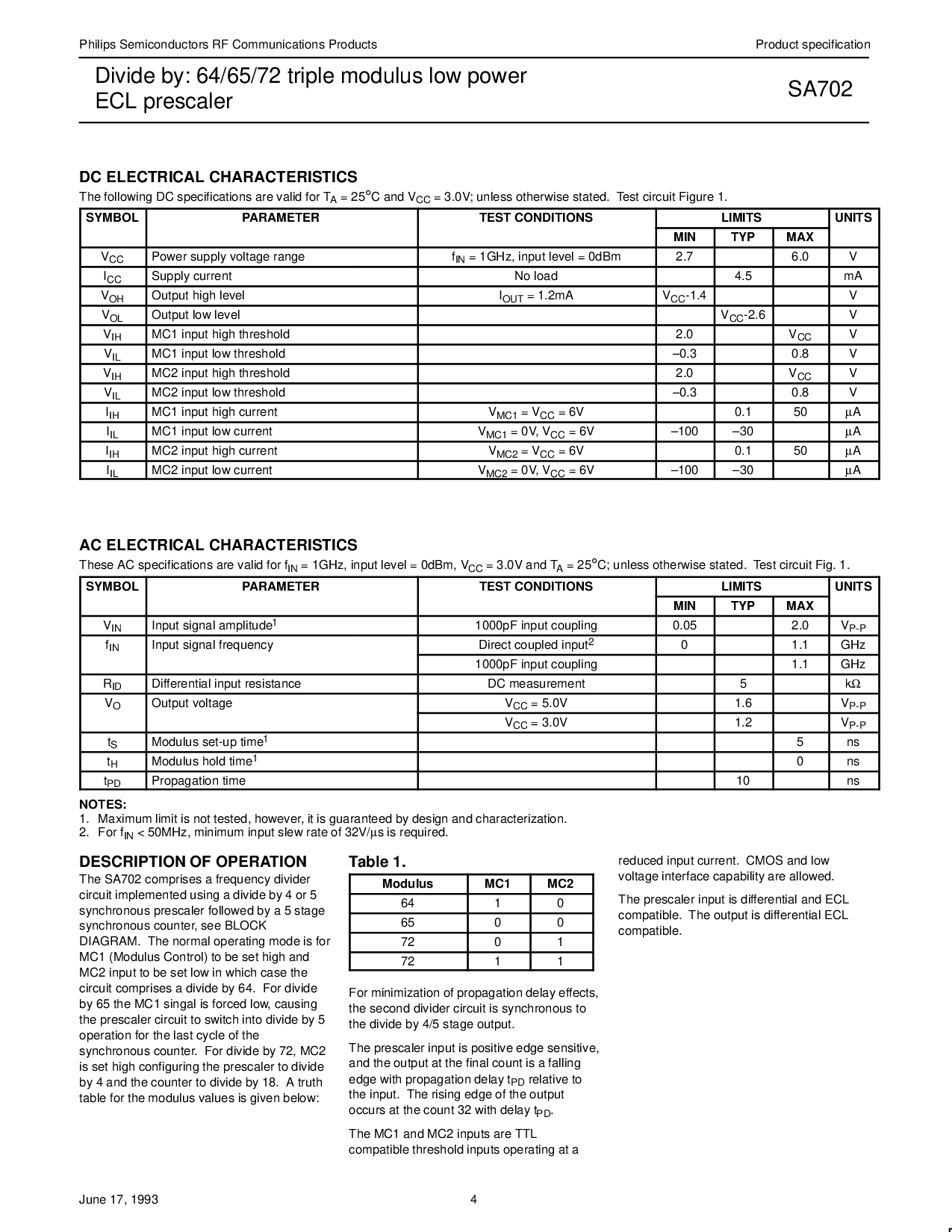

直流 电的 特性

这下列的 直流 规格 是 有效的 为 t

一个

= 25

°

c 和 v

CC

= 3.0v; 除非 否则 陈述. 测试 电路 图示 1.

标识

参数 测试 情况 限制 单位

最小值 典型值 最大值

V

CC

电源 供应 电压 范围 f

在

= 1ghz, 输入 水平的 = 0dbm 2.7 6.0 V

I

CC

供应 电流 非 加载 4.5 毫安

V

OH

输出 高 水平的 I

输出

= 1.2ma V

CC

-1.4 V

V

OL

输出 低 水平的 V

CC

-2.6 V

V

IH

mc1 输入 高 门槛 2.0 V

CC

V

V

IL

mc1 输入 低 门槛 –0.3 0.8 V

V

IH

mc2 输入 高 门槛 2.0 V

CC

V

V

IL

mc2 输入 低 门槛 –0.3 0.8 V

I

IH

mc1 输入 高 电流 V

MC1

= v

CC

= 6v 0.1 50

µ

一个

I

IL

mc1 输入 低 电流 V

MC1

= 0v, v

CC

= 6v –100 –30

µ

一个

I

IH

mc2 输入 高 电流 V

MC2

= v

CC

= 6v 0.1 50

µ

一个

I

IL

mc2 输入 低 电流 V

MC2

= 0v, v

CC

= 6v –100 –30

µ

一个

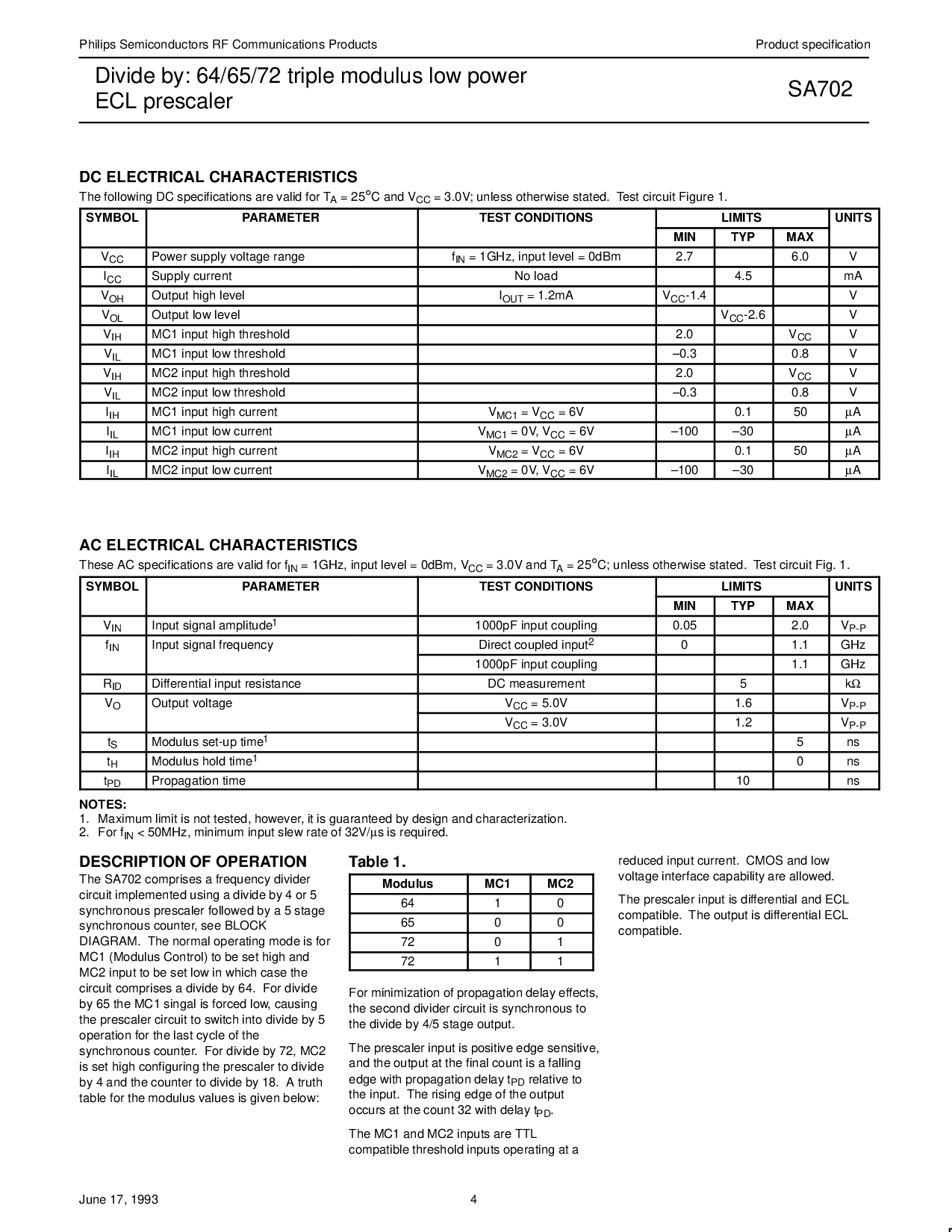

交流 电的 特性

这些 交流 规格 是 有效的 为 f

在

= 1ghz, 输入 水平的 = 0dbm, v

CC

= 3.0v 和 t

一个

= 25

°

c; 除非 否则 陈述. 测试 电路 图. 1.

标识

参数 测试 情况 限制 单位

最小值 典型值 最大值

V

在

输入 信号 振幅

1

1000pf 输入 连接 0.05 2.0 V

p-p

f

在

输入 信号 频率 直接 结合 输入

2

0 1.1 GHz

1000pf 输入 连接 1.1 GHz

R

ID

差别的 输入 阻抗 直流 度量 5 k

Ω

V

O

输出 电压 V

CC

= 5.0v 1.6 V

p-p

V

CC

= 3.0v 1.2 V

p-p

t

S

modulus 设置-向上 时间

1

5 ns

t

H

modulus 支撑 时间

1

0 ns

t

PD

传播 时间 10 ns

注释:

1. 最大 限制 是 不 测试, 不管怎样, 它 是 有保证的 用 设计 和 描绘.

2. 为 f

在

< 50mhz, 最小 输入 回转 比率 的 32v/

µ

s 是 必需的.

描述 的 运作

这 sa702 comprises 一个 频率 分隔物

电路 执行 使用 一个 分隔 用 4 或者 5

同步的 预分频器 followed 用 一个 5 平台

同步的 计数器, 看 块

图解. 这 正常的 运行 模式 是 为

mc1 (modulus 控制) 至 是 设置 高 和

mc2 输入 至 是 设置 低 在 这个 情况 这

电路 comprises 一个 分隔 用 64. 为 分隔

用 65 这 mc1 singal 是 强迫 低, 造成

这 预分频器 电路 至 转变 在 分隔 用 5

运作 为 这 last 循环 的 这

同步的 计数器. 为 分隔 用 72, mc2

是 设置 高 configuring 这 预分频器 至 分隔

用 4 和 这 计数器 至 分隔 用 18. 一个 真实

表格 为 这 modulus 值 是 给 在下:

表格 1.

Modulus MC1 MC2

64 1 0

65 0 0

72 0 1

72 1 1

为minimization 的 传播 延迟 effects,

这 第二 分隔物 电路 是 同步的 至

这 分隔 用 4/5 平台 输出.

这 预分频器 输入 是 积极的 边缘 敏感的,

和 这 输出 在 这 最终 计数 是 一个 下落

边缘 和 传播 延迟 t

PD

相关的 至

这 输入. 这 rising 边缘 的 这 输出

occurs 在 这 计数 32 和 延迟 t

PD

.

这 mc1 和 mc2 输入 是 ttl

兼容 门槛 输入 运行 在 一个

减少 输入 电流. cmos 和 低

电压 接口 能力 是 允许.

这 预分频器 输入 是 差别的 和 ecl

兼容. 这 输出 是 differential ecl

兼容.