2000 Jan 18 7

飞利浦 半导体 产品 规格

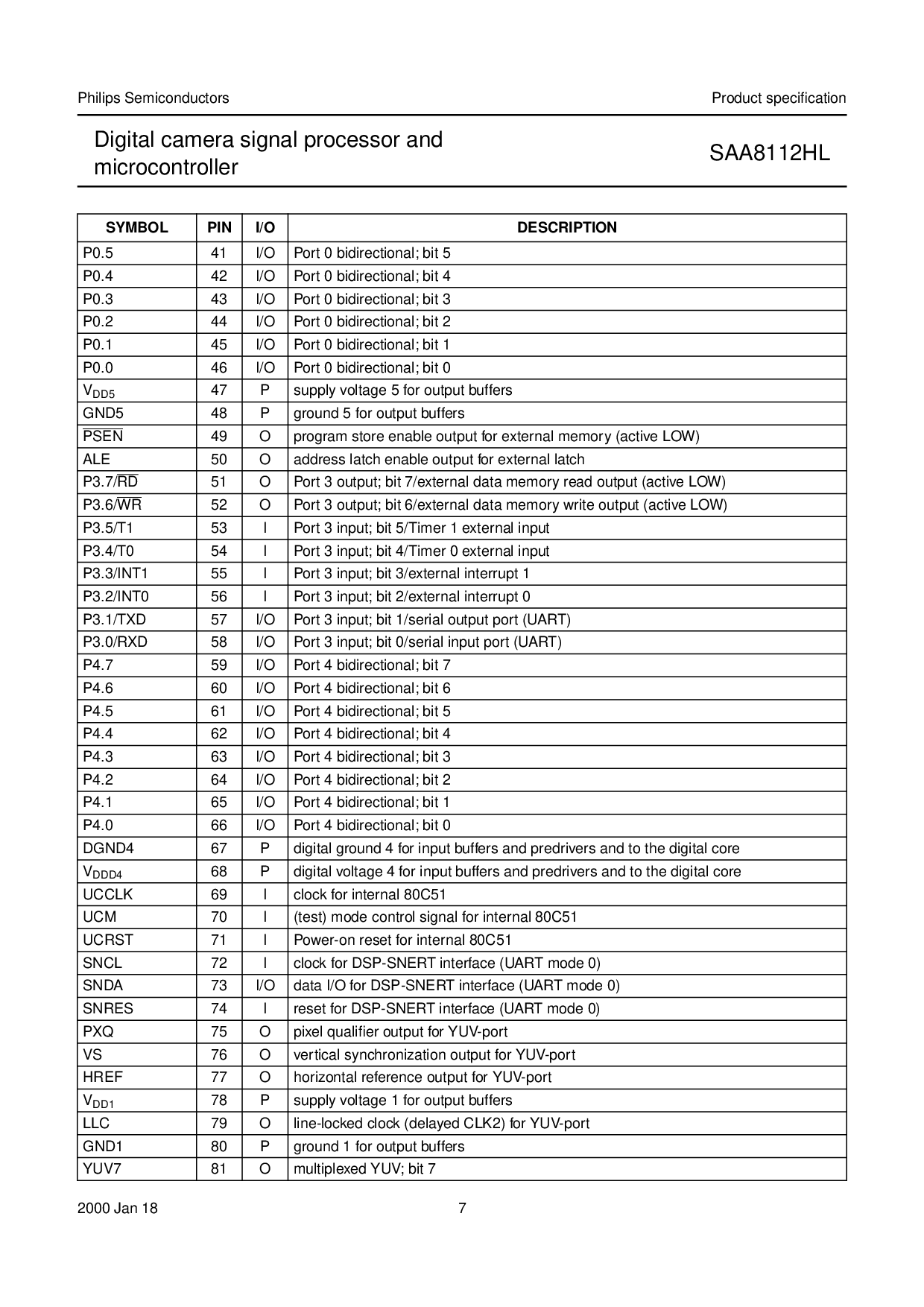

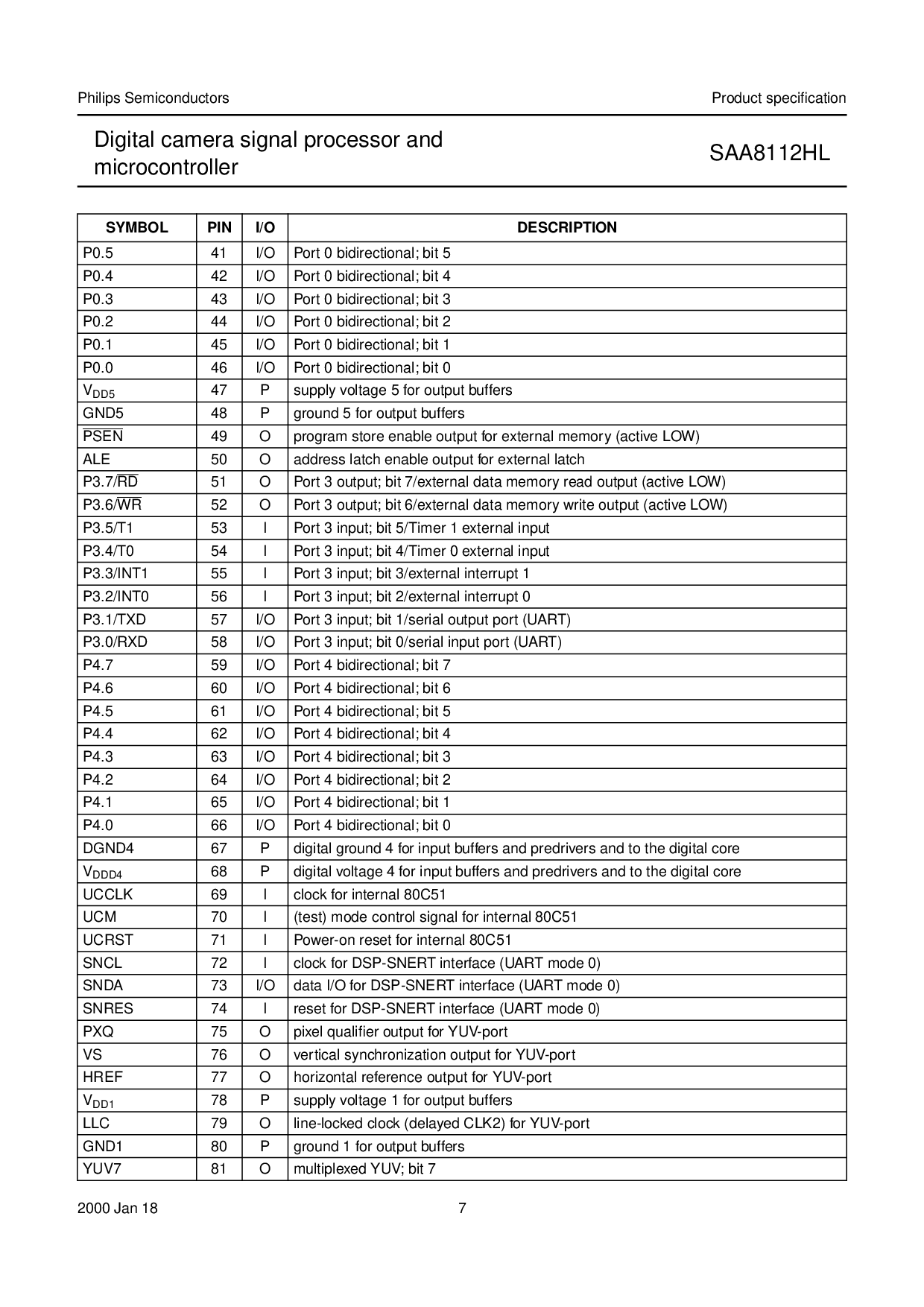

数字的 camera 信号 处理器 和

微控制器

SAA8112HL

p0.5 41 i/o 端口 0 双向的; 位 5

p0.4 42 i/o 端口 0 双向的; 位 4

p0.3 43 i/o 端口 0 双向的; 位 3

p0.2 44 i/o 端口 0 双向的; 位 2

p0.1 45 i/o 端口 0 双向的; 位 1

p0.0 46 i/o 端口 0 双向的; 位 0

V

DD5

47 P 供应 电压 5 为 输出 缓存区

GND5 48 P 地面 5 为 输出 缓存区

PSEN 49 O 程序 store 使能 输出 为 外部 记忆 (起作用的 低)

ALE 50 O 地址 获得 使能 输出 为 外部 获得

p3.7/

RD 51 O 端口 3 输出; 位 7/外部 数据 记忆 读 输出 (起作用的 低)

p3.6/

WR 52 O 端口 3 输出; 位 6/外部 数据 记忆 写 输出 (起作用的 低)

p3.5/t1 53 I 端口 3 输入; 位 5/计时器 1 外部 输入

p3.4/t0 54 I 端口 3 输入; 位 4/计时器 0 外部 输入

p3.3/int1 55 I 端口 3 输入; 位 3/外部 中断 1

p3.2/int0 56 I 端口 3 输入; 位 2/外部 中断 0

p3.1/txd 57 i/o 端口 3 输入; 位 1/串行 输出 端口 (uart)

p3.0/rxd 58 i/o 端口 3 输入; 位 0/串行 输入 端口 (uart)

p4.7 59 i/o 端口 4 双向的; 位 7

p4.6 60 i/o 端口 4 双向的; 位 6

p4.5 61 i/o 端口 4 双向的; 位 5

p4.4 62 i/o 端口 4 双向的; 位 4

p4.3 63 i/o 端口 4 双向的; 位 3

p4.2 64 i/o 端口 4 双向的; 位 2

p4.1 65 i/o 端口 4 双向的; 位 1

p4.0 66 i/o 端口 4 双向的; 位 0

DGND4 67 P 数字的 地面 4 为 输入 缓存区 和 predrivers 和 至 这 数字的 核心

V

DDD4

68 P 数字的 电压 4 为 输入 缓存区 和 predrivers 和 至 这 数字的 核心

UCCLK 69 I 时钟 为 内部的 80c51

UCM 70 I (测试) 模式 控制 信号 为 内部的 80c51

UCRST 71 I 电源-在 重置 为 内部的 80c51

SNCL 72 I 时钟 为 dsp-snert 接口 (uart 模式 0)

SNDA 73 i/o 数据 i/o 为 dsp-snert 接口 (uart 模式 0)

SNRES 74 I 重置 为 dsp-snert 接口 (uart 模式 0)

PXQ 75 O pixel qualifier 输出 为 yuv-端口

VS 76 O vertical 同步 输出 为 yuv-端口

HREF 77 O horizontal 涉及 输出 为 yuv-端口

V

DD1

78 P 供应 电压 1 为 输出 缓存区

LLC 79 O 线条-锁 时钟 (delayed clk2) 为 yuv-端口

GND1 80 P 地面 1 为 输出 缓存区

YUV7 81 O 多路复用 yuv; 位 7

标识 管脚

i/o

描述