20dec96@09:25h intermediate 版本

半导体 组 6

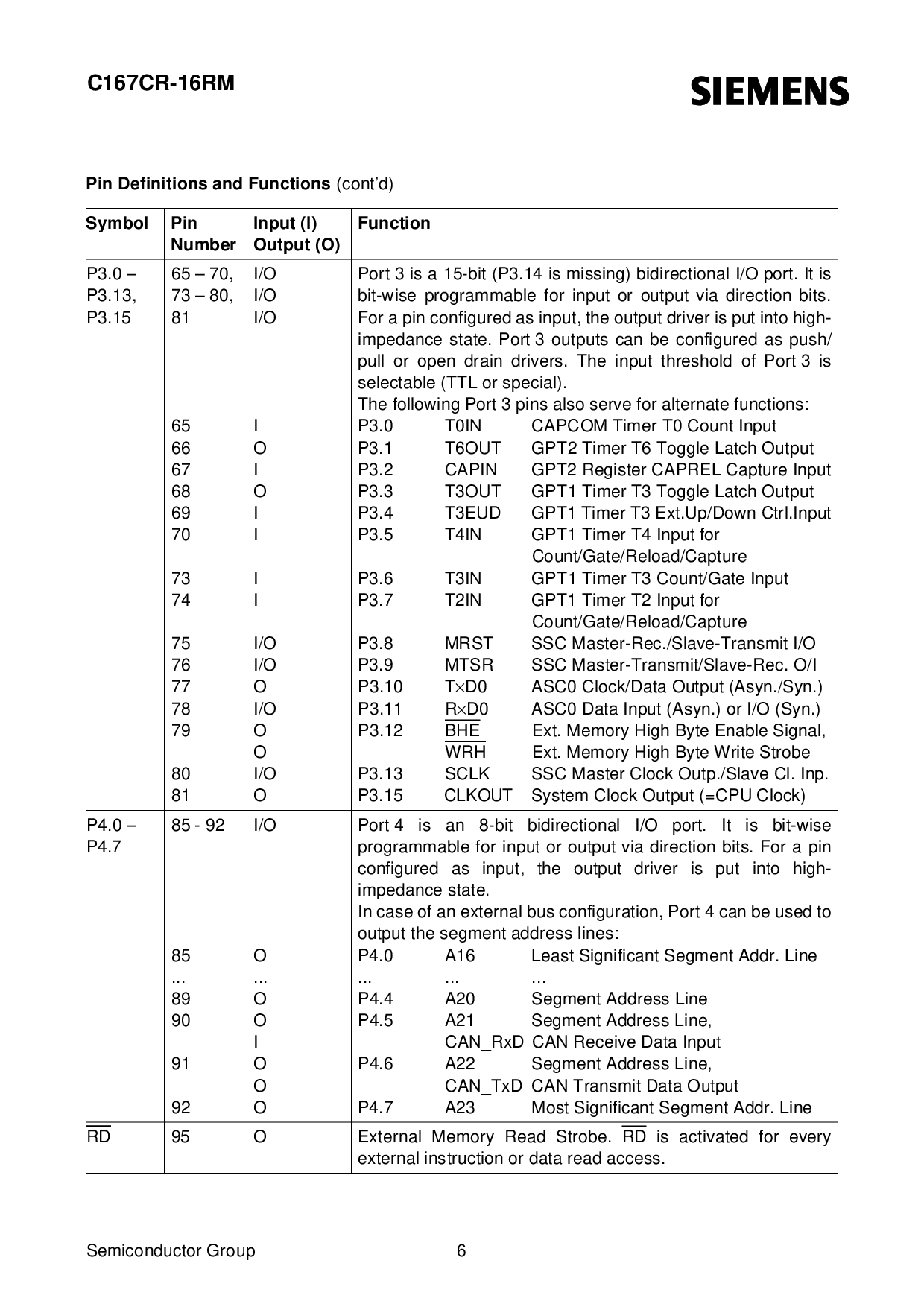

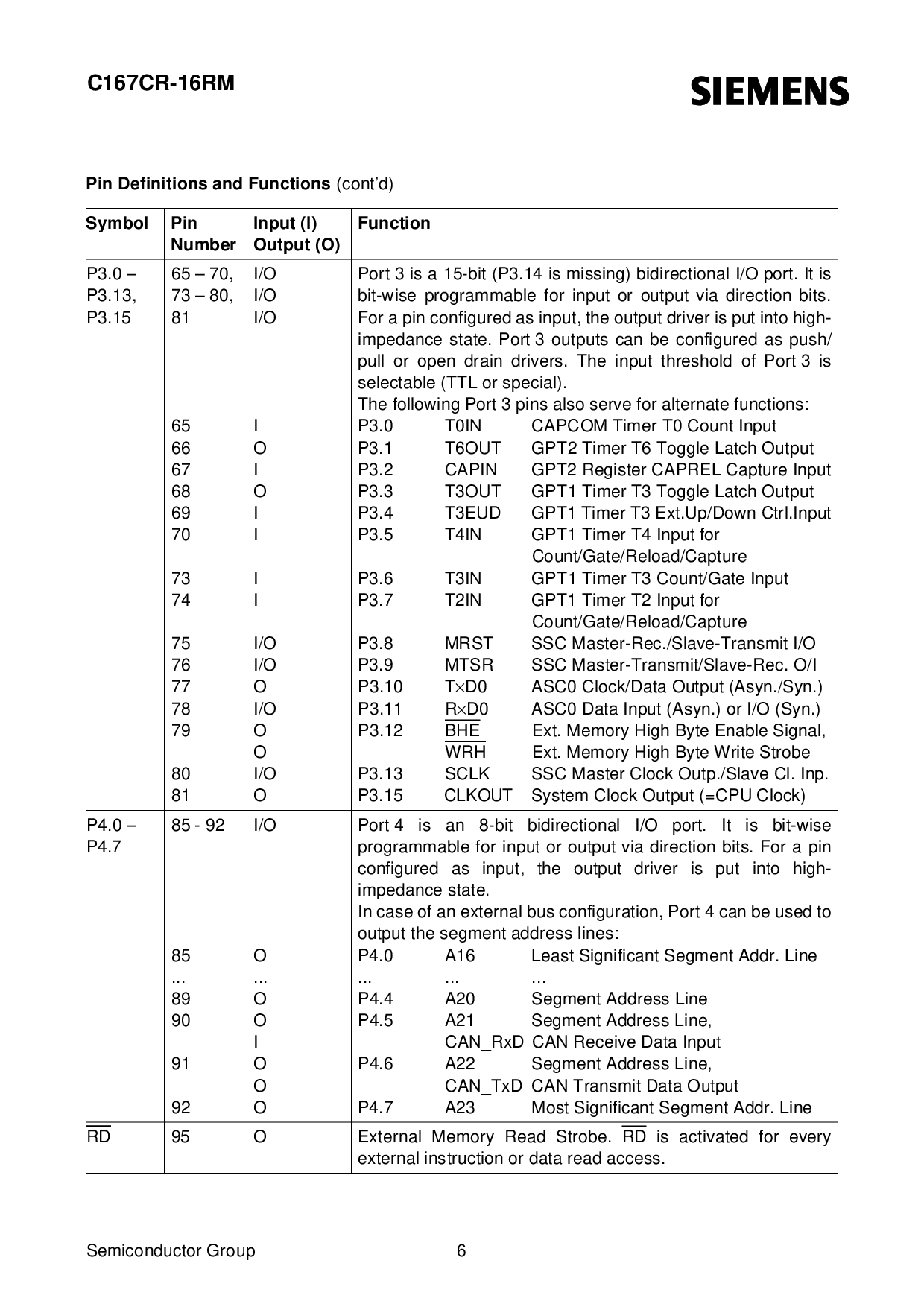

c167cr-16rm

p3.0 –

p3.13,

p3.15

65 – 70,

73 – 80,

81

65

66

67

68

69

70

73

74

75

76

77

78

79

80

81

i/o

i/o

i/o

I

O

I

O

I

I

I

I

i/o

i/o

O

i/o

O

O

i/o

O

端口 3 是 一个 15-位 (p3.14 是 missing) 双向的 i/o port. 它 是

位-wise 可编程序的 为 输入 或者 输出 通过 方向 位.

为 一个 管脚 配置 作 输入, 这 输出 驱动器 是 放 在 高-

阻抗 状态. 端口 3 输出 能 是 配置 作 推/

拉 或者 打开 流 驱动器. 这 输入 门槛 的 端口 3 是

可选择的 (ttl 或者 特定的).

这 下列的 端口 3 管脚 也 提供 为 alternate 功能:

p3.0 T0IN capcom 计时器 t0 计数 输入

p3.1 T6OUT gpt2 计时器 t6 toggle 获得 输出

p3.2 CAPIN gpt2 寄存器 caprel 俘获 输入

p3.3 T3OUT gpt1 计时器 t3 toggle 获得 输出

p3.4 T3EUD gpt1 计时器 t3 ext.向上/向下 ctrl.输入

p3.5 T4IN gpt1 计时器 t4 输入 为

计数/门/再装填/俘获

p3.6 T3IN gpt1 计时器 t3 计数/门 输入

p3.7 T2IN gpt1 计时器 t2 输入 为

计数/门/再装填/俘获

p3.8 MRST ssc 主控-rec./从动装置-transmit i/o

p3.9 MTSR ssc 主控-transmit/从动装置-rec. o/i

p3.10 T

×

D0 asc0 时钟/数据 输出 (asyn./syn.)

p3.11 R

×

D0 asc0 数据 输入 (asyn.) 或者 i/o (syn.)

p3.12 BHE

ext. 记忆 高 字节 使能 信号,

WRH

ext. 记忆 高 字节 写 strobe

p3.13 SCLK ssc 主控 时钟 outp./从动装置 cl. inp.

p3.15 CLKOUT 系统 时钟 输出 (=cpu 时钟)

p4.0 –

p4.7

85 - 92

85

...

89

90

91

92

i/o

O

...

O

O

I

O

O

O

端口 4 是 一个 8-位 双向的 i/o 端口. 它 是 位-wise

可编程序的 为 输入 或者 输出 通过 方向 位. 为 一个 管脚

配置 作 输入, 这 输出 驱动器 是 放 在 高-

阻抗 状态.

在 情况 的 一个 外部 总线 配置, 端口 4 能 是 使用 至

输出 这 段 地址 线条:

p4.0 A16 least 重大的 段 地址. 线条

... ... ...

p4.4 A20 段 地址 线条

p4.5 A21 段 地址 线条,

能_rxd 能 receive 数据 输入

p4.6 A22 段 地址 线条,

能_txd 能 transmit 数据 输出

p4.7 A23 大多数 重大的 段 地址. 线条

RD

95 O 外部 记忆 读 strobe. rd是 使活动 为 每

外部 操作指南 或者 数据 读 进入.

管脚 定义 和 功能

(内容’d)

标识 管脚

号码

输入 (i)

输出 (o)

函数