硅 image, 公司

sii 161

一个

SiI

-DS-0009-D

硅 image, 公司

9 主题 至 改变 没有 注意

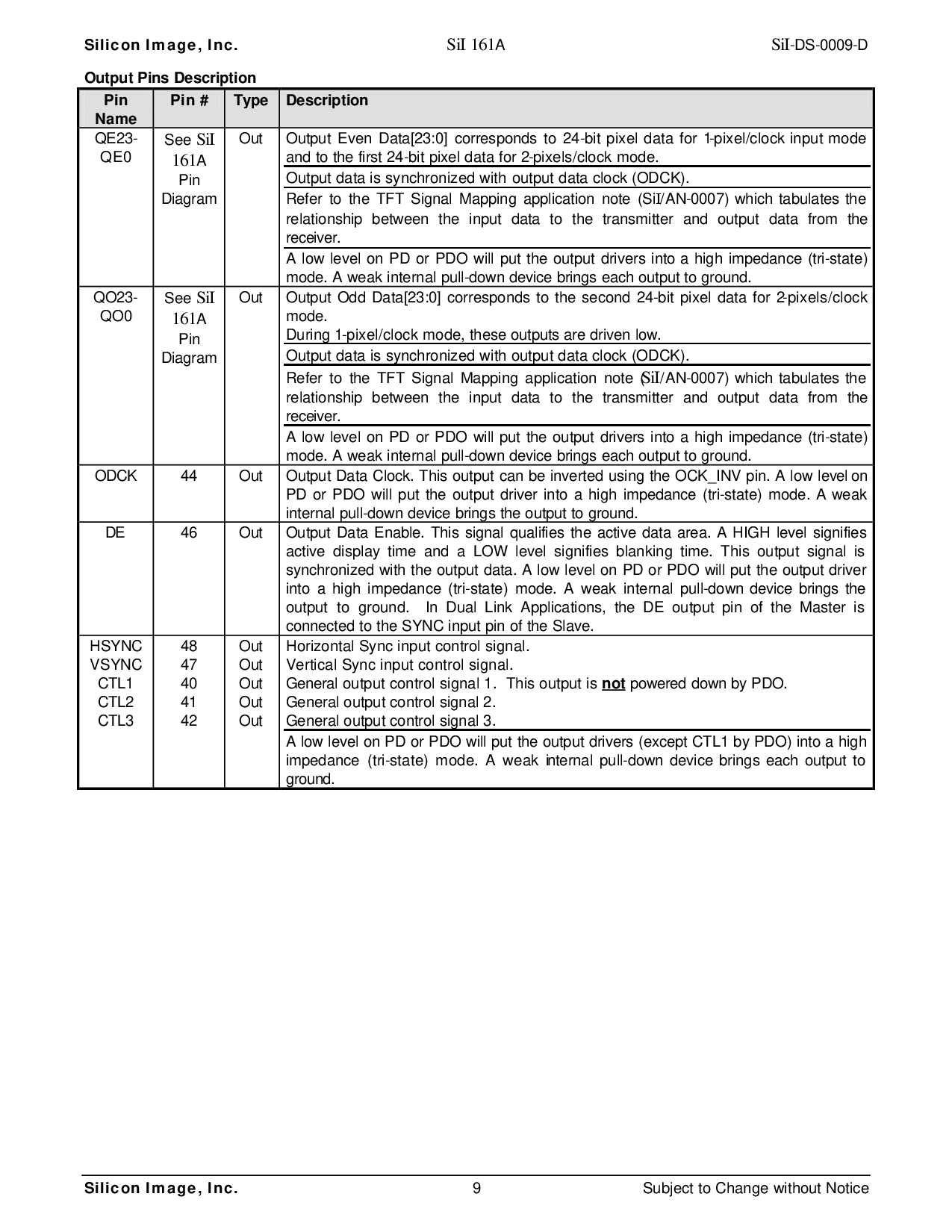

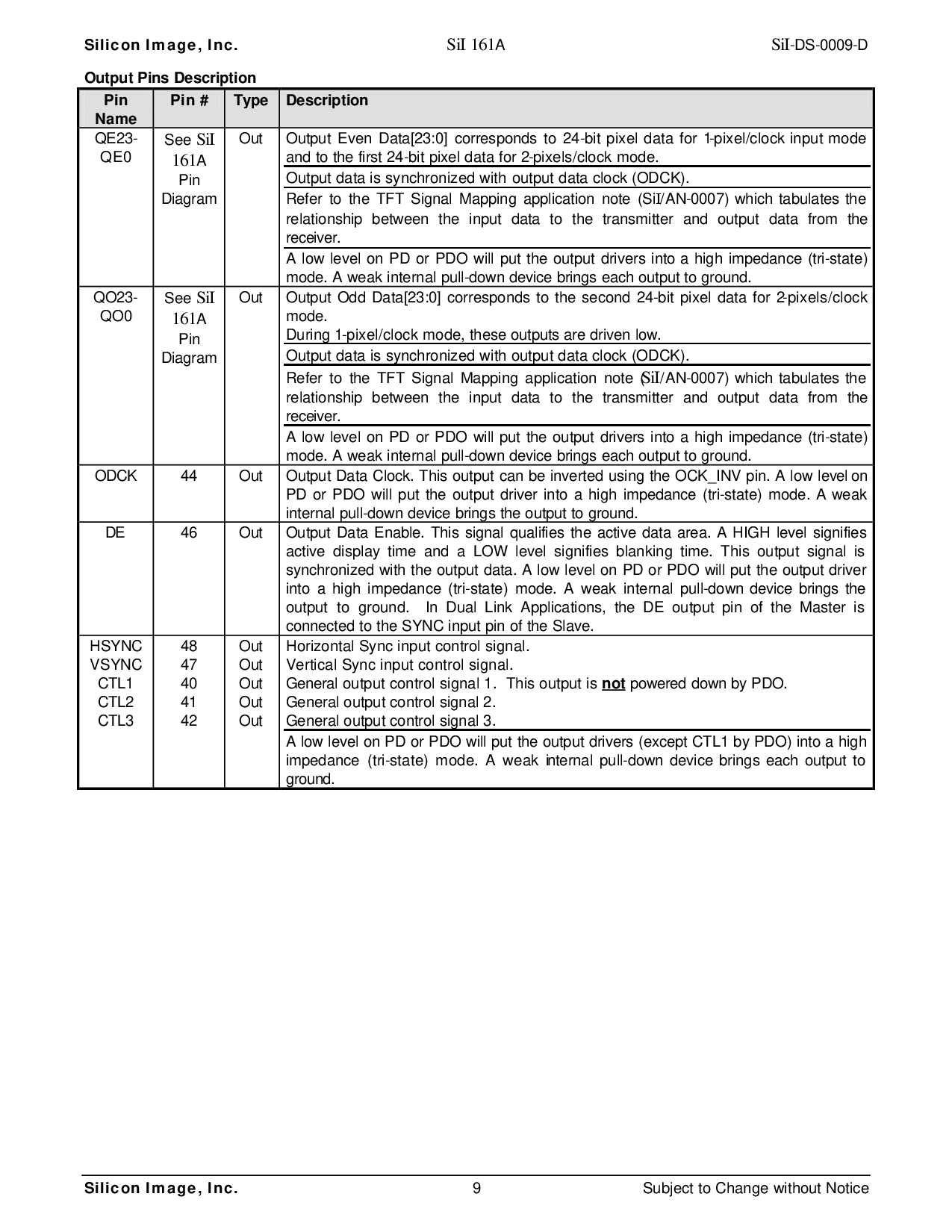

输出 管脚 description

管脚

名字

管脚 # 类型 描述

QE23-

QE0

看

SiI

161

一个

管脚

图解

输出 输出 甚至 data[23:0] corresponds 至 24-位 pixel 数据 为 1-pixel/时钟 输入 模式

和 至 这 第一 24-位 pixel 数据 为 2-pixels/时钟 模式.

输出 数据 是 同步 和输出 数据 时钟 (odck).

谈及 至 这 tft 信号 mapping 应用 便条 (si

I

/一个-0007) 这个 tabulates 这

relationship 在 这 输入 数据 至 这 传输者 和 输出 数据 从 这

接受者.

一个 低 水平的 在 pd 或者 pdo 将 放 这 输出 驱动器 在一个 高 阻抗 (触发-状态)

模式. 一个 弱 内部的 拉-向下 设备 brings 各自 输出 至 地面.

QO23-

QO0

看

SiI

161

一个

管脚

图解

输出 输出 odd data[23:0] corresponds 至 这 第二 24-位 pixel 数据 为 2-pixels/时钟

模式.

在 1-pixel/时钟 mode, 这些 输出 是 驱动 低.

输出 数据 是 同步 和 输出 数据 时钟 (odck).

谈及 至 这 tft 信号 mapping 应用 便条 (

SiI

/一个-0007) 这个 tabulates 这

relationship 在 这 输入 数据 至 这 传输者 和 输出 数据 从 这

receiver.

一个 低 水平的 在 pd 或者 pdo 将 放 这 输出 驱动器 在 一个 高 阻抗 (触发-状态)

模式. 一个 弱 内部的 拉-向下 设备 brings 各自 输出 至 地面.

ODCK 44 输出 输出 数据 时钟. 这个 输出 能 是 inverted 使用 这 ock_inv 管脚. 一个 低 level 在

pd 或者 pdo 将 放 这 输出 驱动器 在 一个 高 阻抗 (触发-状态) 模式. 一个 弱

内部的 拉-向下 设备 brings 这 输出 至 地面.

DE 46 输出 输出 数据 使能. 这个 信号 qualifies 这 起作用的 数据 范围. 一个 高 水平的 signifies

起作用的 display 时间 和 一个 低 水平的 signifies blanking 时间. 这个 输出 信号 是

同步 和 这 输出 数据. 一个 低 水平的 在 pd 或者 pdo 将 放 这 输出 驱动器

在 一个 高 阻抗 (触发-状态) 模式. 一个 弱 内部的 拉-向下 设备 brings 这

输出 至 ground. 在 双 link 产品, 这 de 输出 管脚 的 这 主控 是

连接 至 这 同步 输入 管脚 的 这 从动装置.

HSYNC

VSYNC

CTL1

CTL2

CTL3

48

47

40

41

42

输出

输出

输出

输出

输出

horizontal 同步 输入 控制 信号.

vertical 同步 输入 控制 信号.

General 输出 控制 信号 1. 这个 输出 是

不

powered 向下 用 pdo.

一般 输出 控制 信号 2.

一般 输出 控制 信号 3.

一个 低 水平的 在 pd 或者 pdo 将 放 这 输出 驱动器 (除了 ctl1 用 pdo) 在 一个 高

阻抗 (触发-状态) 模式. 一个 弱 internal 拉-向下 设备 brings 各自 输出 至

地面.