3

ClockWorks

™

SY89429V

Micrel

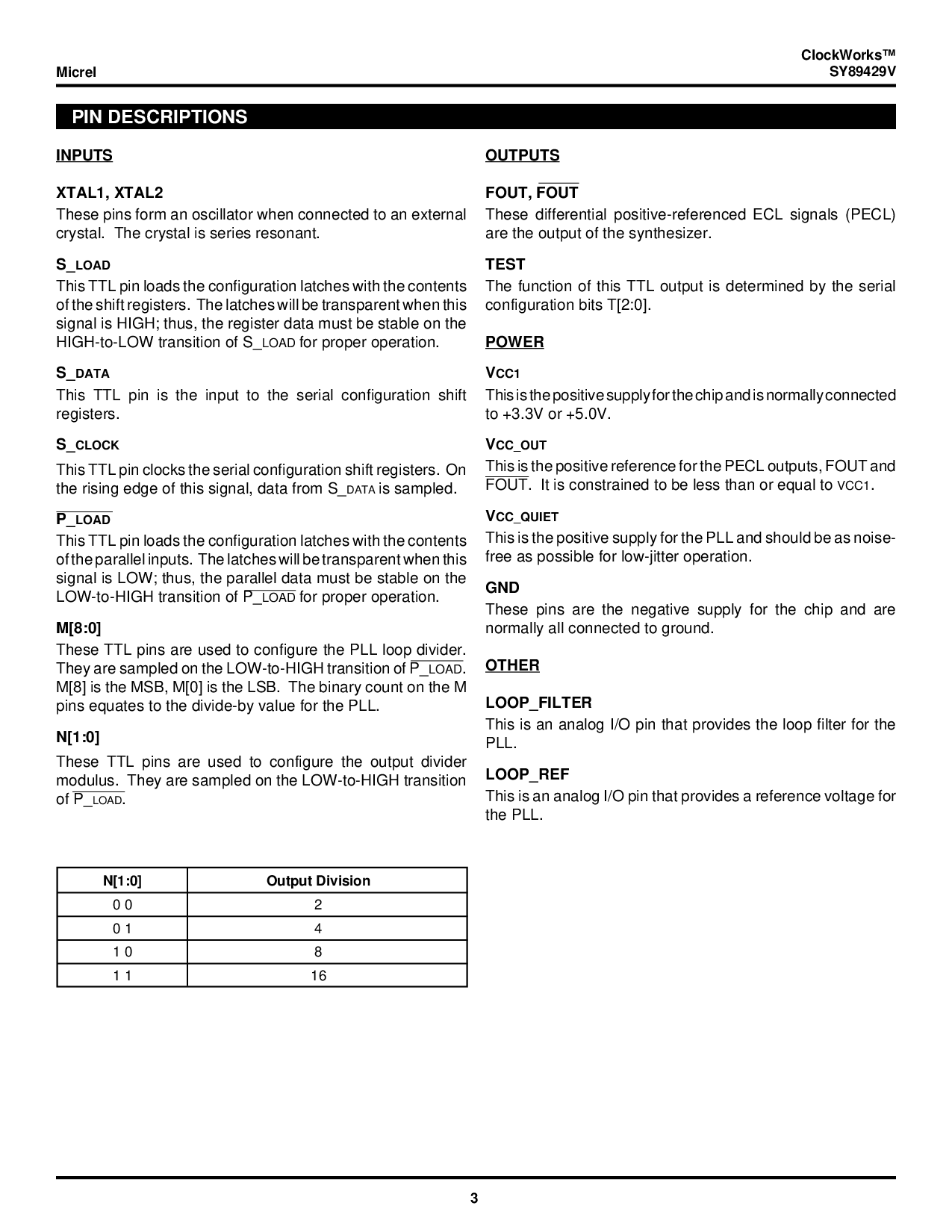

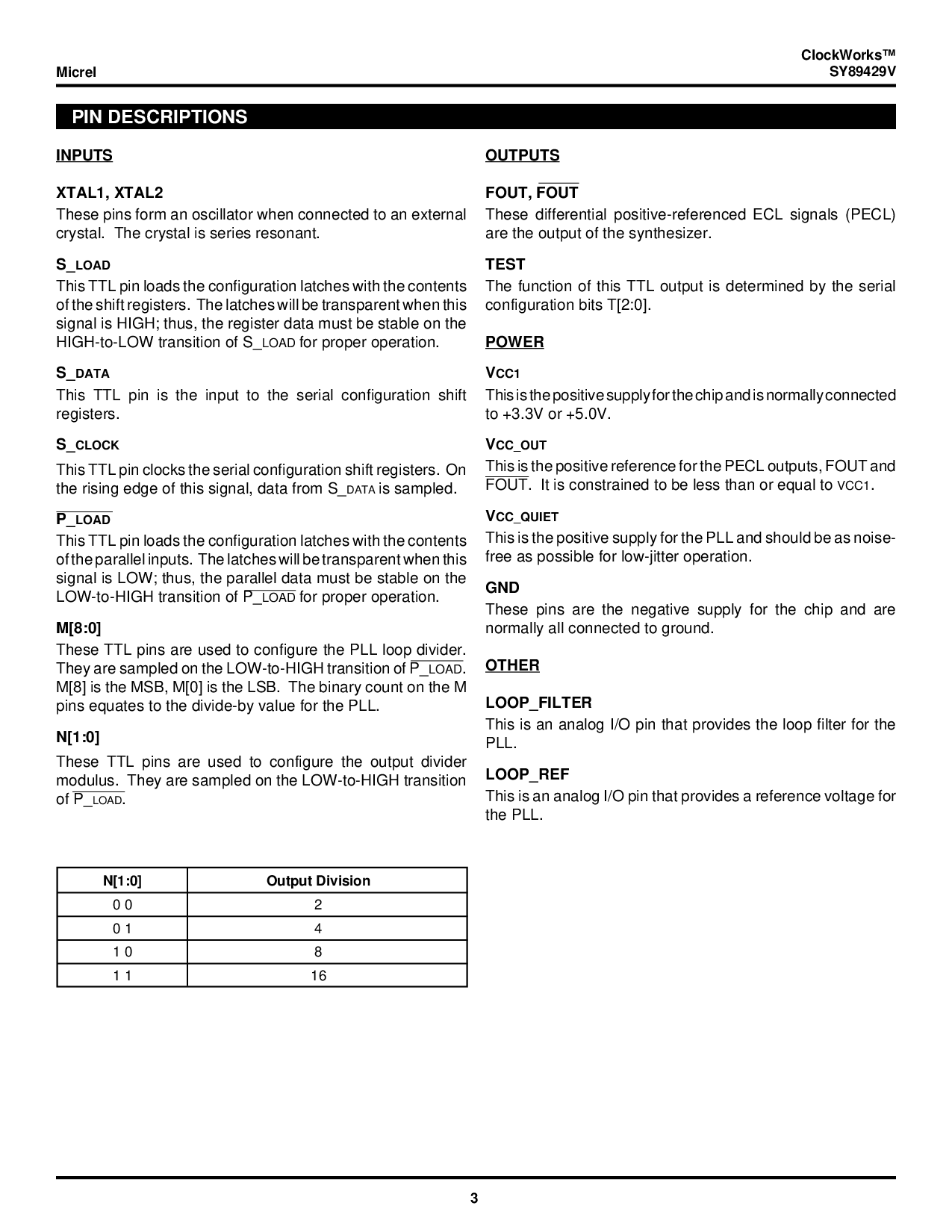

管脚 描述

n[1:0] 输出 分隔

0 0 2

0 1 4

1 0 8

1 1 16

输入

xtal1, xtal2

这些 管脚 表格 一个 振荡器 当 连接 至 一个 外部

结晶. 这 结晶 是 序列 resonant.

s_

加载

这个 ttl 管脚 负载 这 配置 latches 和 这 内容

的 这 变换 寄存器. 这 latches 将 是 transparent 当 这个

信号 是 高; 因此, 这 寄存器 数据 必须 是 稳固的 在 这

高-至-低 转变 的 s_

加载

为 恰当的 运作.

s_

数据

这个 ttl 管脚 是 这 输入 至 这 串行 配置 变换

寄存器.

s_

时钟

这个 ttl 管脚 clocks 这 串行 配置 变换 寄存器. 在

这 rising 边缘 的 这个 信号, 数据 从 s_

数据

是 抽样.

p_

加载

这个 ttl 管脚 负载 这 配置 latches 和 这 内容

的 这 并行的 输入. 这 latches 将 是 transparent 当 这个

信号 是 低; 因此, 这 并行的 数据 必须 是 稳固的 在 这

低-至-高 转变 的 p_

加载

为 恰当的 运作.

m[8:0]

这些 ttl 管脚 是 使用 至 配置 这 pll 循环 分隔物.

它们 是 抽样 在 这 低-至-高 转变 的 p_

加载

.

m[8] 是 这 msb, m[0] 是 这 lsb. 这 二进制的 计数 在 这 m

管脚 equates 至 这 分隔-用 值 为 这 pll.

n[1:0]

这些 ttl 管脚 是 使用 至 配置 这 输出 分隔物

modulus. 它们 是 抽样 在 这 低-至-高 转变

的 p_

加载

.

输出

fout, fout

这些 差别的 积极的-关联 ecl 信号 (pecl)

是 这 输出 的 这 synthesizer.

测试

这 函数 的 这个 ttl 输出 是 决定 用 这 串行

配置 位 t[2:0].

电源

V

CC1

这个 是 这 积极的 供应 为 这 碎片 和 是 正常情况下 连接

至 +3.3v 或者 +5.0v.

V

cc_输出

这个 是 这 积极的 涉及 为 这 pecl 输出, fout 和

fout. 它 是 constrained 至 是 较少 比 或者 equal 至

VCC1

.

V

cc_安静

这个 是 这 积极的 供应 为 这 pll 和 应当 是 作 噪音-

自由 作 可能 为 低-jitter 运作.

地

这些 管脚 是 这 负的 供应 为 这 碎片 和 是

正常情况下 所有 连接 至 地面.

其它

循环_过滤

这个 是 一个 相似物 i/o 管脚 那 提供 这 循环 过滤 为 这

pll.

循环_ref

这个 是 一个 相似物 i/o 管脚 那 提供 一个 涉及 电压 为

这 pll.