SY87700L

2

Micrel

PLLSP TCLKN1811

PLLSN CLKSEL1712

地 PLLRP1613

地 PLLRN1514

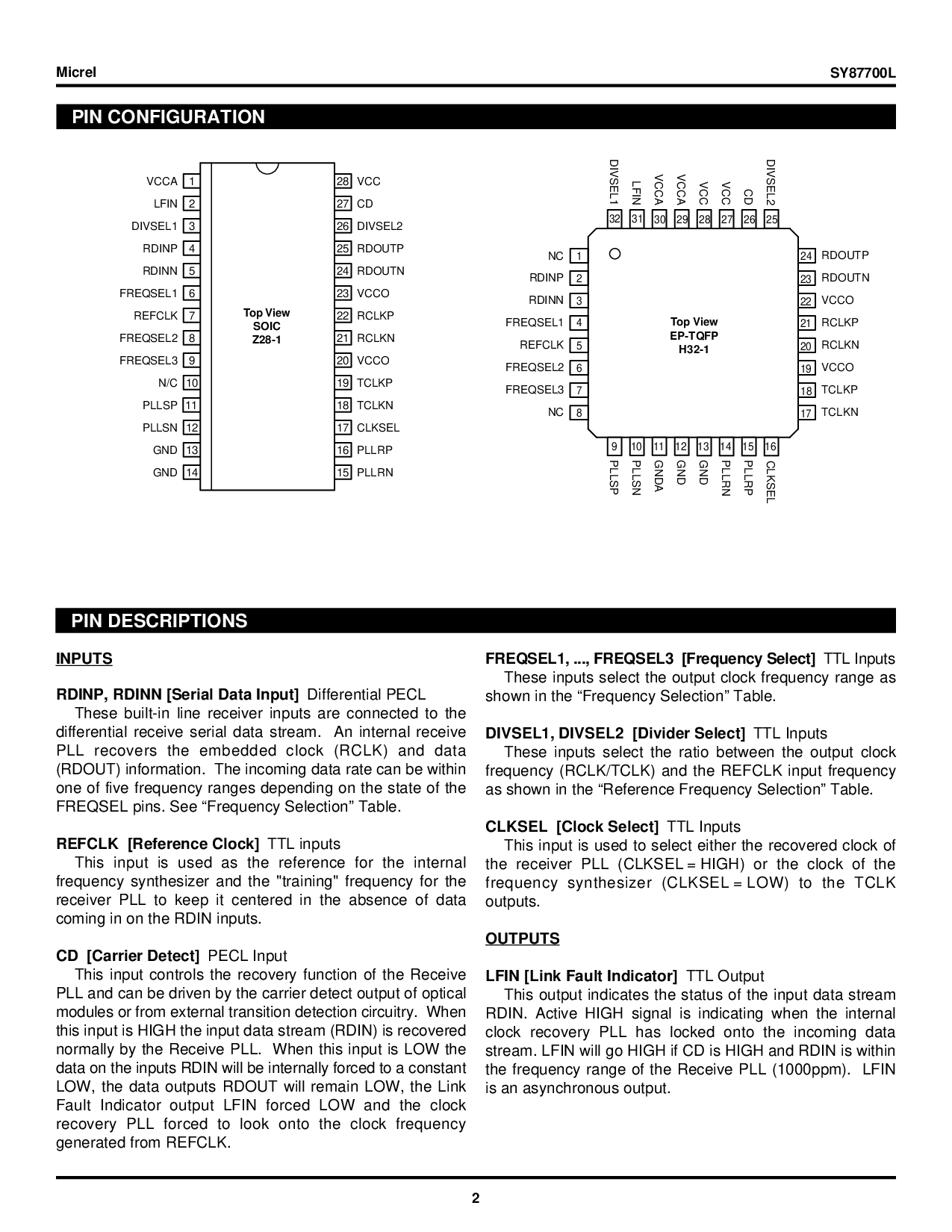

1VCCA

LFIN

DIVSEL1

RDINP

RDINN

FREQSEL1

REFCLK

FREQSEL2

FREQSEL3

n/c

28 VCC

CD

DIVSEL2

RDOUTP

RDOUTN

VCCO

RCLKP

RCLKN

VCCO

TCLKP

27

26

25

24

23

22

21

20

19

2

3

4

5

6

7

8

9

10

顶 视图

SOIC

z28-1

管脚 配置

管脚 描述

输入

rdinp, rdinn [serial 数据 input]

差别的 pecl

这些 建造-在 线条 接受者 输入 是 连接 至 这

差别的 receive 串行 数据 stream. 一个 内部的 receive

pll recovers 这 embedded 时钟 (rclk) 和 数据

(rdout) 信息. 这 新当选的 数据 比率 能 是 在里面

一个 的 five 频率 范围 取决于 在 这 状态 的 这

freqsel 管脚. 看

“

频率 选择

”

表格.

refclk [reference clock]

ttl 输入

这个 输入 是 使用 作 这 涉及 为 这 内部的

频率 synthesizer 和 这 "training" 频率 为 这

接受者 pll 至 保持 它 集中 在 这 absence 的 数据

coming 在 在 这 rdin 输入.

cd [carrier detect]

pecl 输入

这个 输入 控制 这 恢复 函数 的 这 receive

pll 和 能 是 驱动 用 这 运输车 发现 输出 的 视力的

modules 或者 从 外部 转变 发现 电路系统. 当

这个 输入 是 高 这 输入 数据 stream (rdin) 是 recovered

正常情况下 用 这 receive pll. 当 这个 输入 是 低 这

数据 在 这 输入 rdin 将 是 内部 强迫 至 一个 常量

低, 这 数据 输出 rdout 将 仍然是 低, 这 link

故障 指示信号 输出 lfin 强迫 低 和 这 时钟

恢复 pll 强迫 至 看 面向 这 时钟 频率

发生 从 refclk.

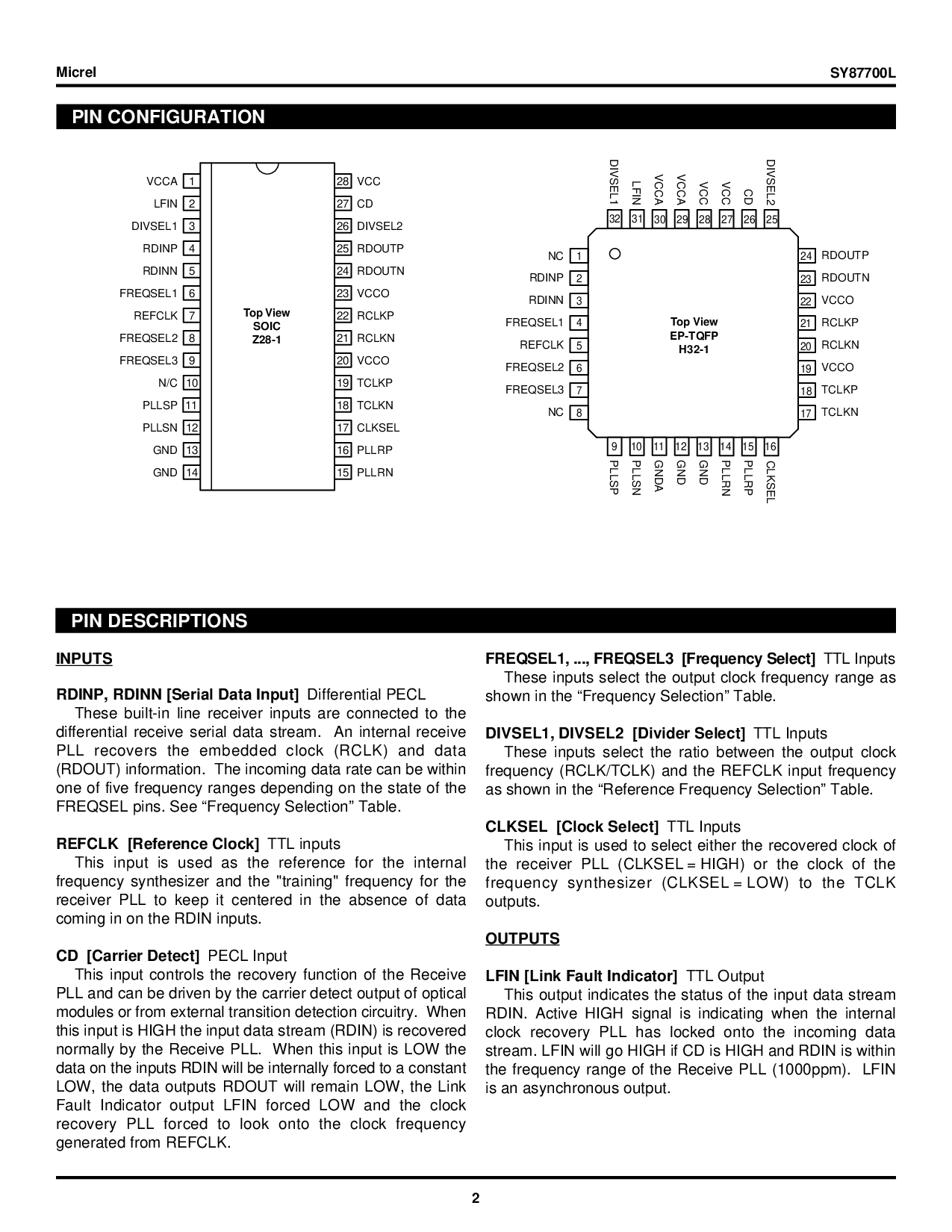

1

2

3

4

5

6

7

8

24

23

22

21

20

19

18

17

NC

RDINP

RDINN

FREQSEL1

REFCLK

FREQSEL2

FREQSEL3

NC

RDOUTP

RDOUTN

VCCO

RCLKP

RCLKN

VCCO

TCLKP

TCLKN

9

10

11 12 13 14 15 16

CLKSEL

PLLRP

PLLRN

地

地

GNDA

PLLSN

PLLSP

32

31

30 29 28 27 26 25

DIVSEL2

CD

VCC

VCC

VCCA

VCCA

LFIN

DIVSEL1

顶 视图

ep-tqfp

h32-1

freqsel1, ..., freqsel3 [frequency select]

ttl 输入

这些 输入 选择 这 输出 时钟 频率 范围 作

显示 在 这

“

频率 选择

”

表格.

divsel1, divsel2 [divider select]

ttl 输入

这些 输入 选择 这 比率 在 这 输出 时钟

频率 (rclk/tclk) 和 这 refclk 输入 频率

作 显示 在 这

“

涉及 频率 选择

”

表格.

clksel [clock select]

ttl 输入

这个 输入 是 使用 至 选择 也 这 recovered 时钟 的

这 接受者 pll (clksel = 高) 或者 这 时钟 的 这

频率 synthesizer (clksel = 低) 至 这 tclk

输出.

输出

lfin [link 故障 indicator]

ttl 输出

这个 输出 indicates 这 状态 的 这 输入 数据 stream

rdin. 起作用的 高 信号 是 表明 当 这 内部的

时钟 恢复 pll 有 锁 面向 这 新当选的 数据

stream. lfin 将 go 高 如果 cd 是 高 和 rdin 是 在里面

这 频率 范围 的 这 receive pll (1000ppm). lfin

是 一个 异步的 输出.