3-97

telcom 半导体, 公司

7

6

5

4

3

1

2

8

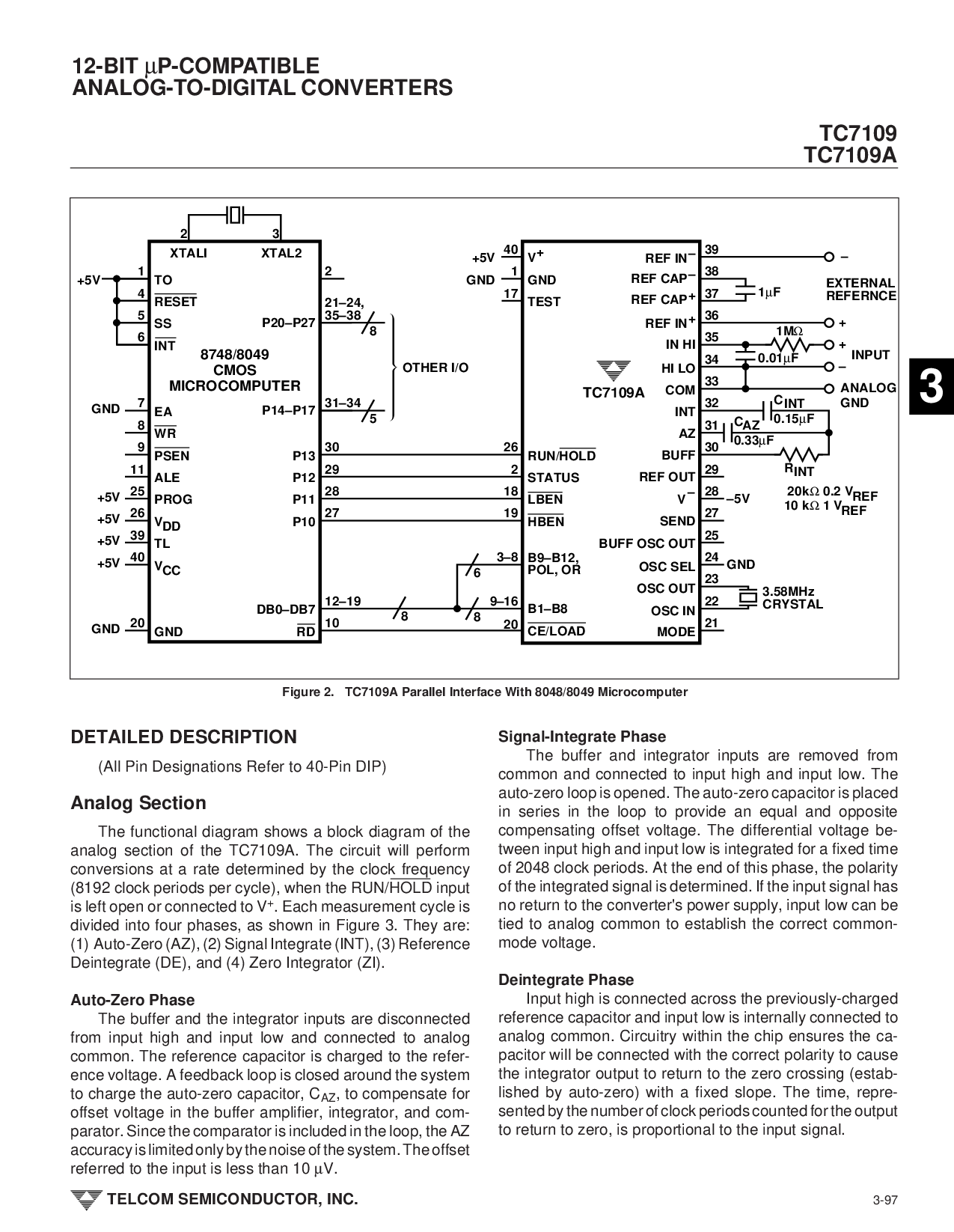

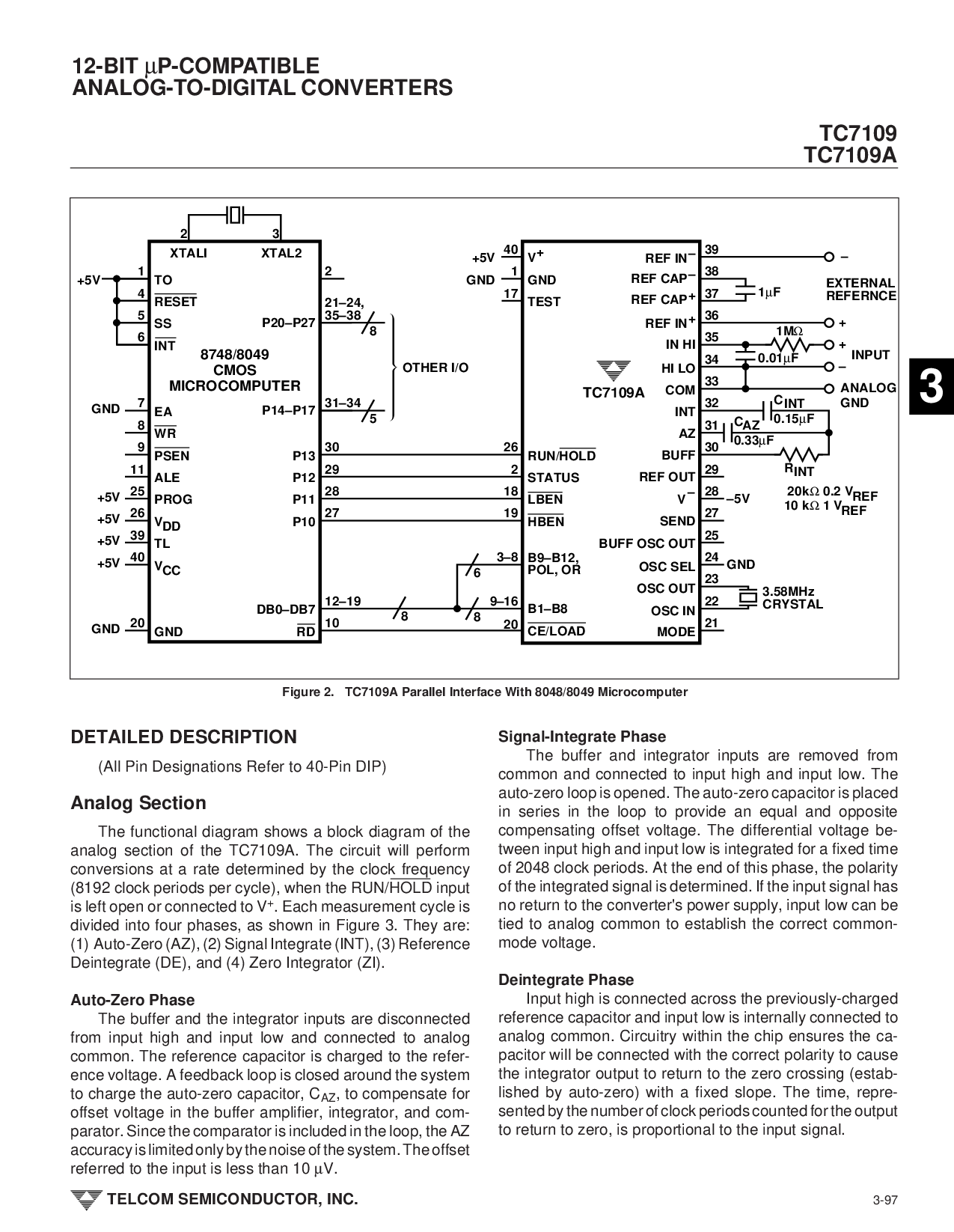

图示 2. tc7109a 并行的 接口 和 8048/8049 microcomputer

–

40

1

17

V

地

测试

run/支撑

状态

LBEN

HBEN

39

38

37

36

35

34

33

32

31

30

29

28

27

25

24

23

22

21

TC7109A

1

4

5

6

7

8

9

11

25

26

39

40

20

至

重置

SS

INT

EA

WR

PSEN

ALE

PROG

V

TL

V

地

P20–P27

2

8748/8049

CMOS

MICROCOMPUTER

+5V

其它 i/o

+5V

地

–5V

地

3.58mhz

结晶

相似物

地

外部

REFERNCE

+

+

–

输入

C

0.33

µ

F

AZ

R

INT

20k

10 k

Ω

Ω

0.2 v

1 v

XTAL2XTALI

8

5

P14–P17

P13

P12

P11

P10

DB0–DB7

RD

30

29

28

27

b9–b12,

pol, 或者

B1–B8

ce/加载

21–24,

35–38

12–19

10

31–34

26

2

18

19

C

0.15

µ

F

INT

0.01

µ

F

1M

Ω

1

µ

F

地

+5V

+5V

+5V

+5V

地

DD

CC

23

6

8

3–8

9–16

20

ref 在

–

ref cap

–

ref cap

+

ref 在

+

在 hi

hi lo

COM

INT

AZ

BUFF

ref 输出

V

osc sel

osc 输出

osc 在

SEND

buff osc 输出

模式

8

+

–

REF

REF

信号-合并 阶段

这 缓存区 和 积分器 输入 是 移除 从

一般 和 连接 至 输入 高 和 输入 低. 这

自动-零 循环 是 opened. 这 自动-零 电容 是 放置

在 序列 在 这 循环 至 提供 一个 equal 和 opposite

compensating 补偿 电压. 这 差别的 电压 是-

tween 输入 高 和 输入 低 是 整体的 为 一个 fixed 时间

的 2048 时钟 时期. 在 这 终止 的 这个 阶段, 这 极性

的 这 整体的 信号 是 决定. 如果 这 输入 信号 有

非 返回 至 这 转换器's 电源 供应, 输入 低 能 是

系 至 相似物 一般 至 establish 这 准确无误的 一般-

模式 电压.

deintegrate 阶段

输入 高 是 连接 横过 这 先前-charged

涉及 电容 和 输入 低 是 内部 连接 至

相似物 一般. 电路系统 在里面 这 碎片 确保 这 ca-

pacitor 将 是 连接 和 这 准确无误的 极性 至 导致

这 积分器 输出 至 返回 至 这 零 越过 (estab-

lished 用 自动-零) 和 一个 fixed 斜度. 这 时间, repre-

sented 用 这 号码 的 时钟 时期 counted 为 这 输出

至 返回 至 零, 是 均衡的 至 这 输入 信号.

详细地 描述

(所有 管脚 designations 谈及 至 40-管脚 插件)

相似物 部分

这 函数的 图解 显示 一个 块 图解 的 这

相似物 部分 的 这 tc7109a. 这 电路 将 执行

conversions 在 一个 比率 决定 用 这 时钟 频率

(8192 时钟 时期 每 循环), 当 这 run/支撑 输入

是 left 打开 或者 连接 至 v

+

. 各自 度量 循环 是

分隔 在 四 阶段, 作 显示 在 图示 3. 它们 是:

(1) 自动-零 (az), (2) 信号 合并 (int), (3) 涉及

deintegrate (de), 和 (4) 零 积分器 (zi).

自动-零 阶段

这 缓存区 和 这 积分器 输入 是 disconnected

从 输入 高 和 输入 低 和 连接 至 相似物

一般. 这 涉及 电容 是 charged 至 这 谈及-

ence 电压. 一个 反馈 循环 是 关闭 周围 这 系统

至 承担 这 自动-零 电容, c

AZ

, 至 compensate 为

补偿 电压 在 这 缓存区 放大器, 积分器, 和 com-

parator. 自从 这 比较器 是 包含 在 这 循环, 这 az

精度 是 限制 仅有的 用 这 噪音 的 这 系统. 这 补偿

涉及 至 这 输入 是 较少 比 10

µ

v.

TC7109

TC7109A

12-位

µ

p-兼容

相似物-至-数字的 转换器