7

TC811

tc811-7 11/5/96

© 2001 微芯 技术 公司 ds21472a

3-1/2 数字 相似物-至-数字的 转换器 和

支撑 和 差别的 涉及 输入

R

INT

C

INT

V

INT

V

REF

电源 消耗, 和 改进 这 整体的 效能.

(看 振荡器 组件)

数字的 部分

这 tc811 包含 所有 这 段 驱动器 需要

至 直接地 驱动 一个 3-1/2 数字 liquid 结晶 显示 (lcd). 一个

lcd backplane 驱动器 是 包含. 这 backplane 频率

是 这 外部 时钟 频率 分隔 用 800. 为 三

conversions/第二 这 backplane 频率 是 60hz 和

一个 5v 名义上的 振幅. 当 一个 段 驱动器 是 在 阶段

和 这 backplane 信号 这 段 的

“

止

”

. 一个 输出 的

阶段 段 驱动 信号 导致 这 段 至 是

“

在

”

或者 visible. 这个 交流 驱动 配置 结果 在 negligible

直流 电压 横过 各自 lcd 段. 这个 insures 长

lcd 显示 生命. 这 极性 段 驱动器 是

“

在

”

为

负的 相似物 输入. 如果 v

在

+

和 v

在

–

是 使反转 然后 这个

指示信号 将 反转.

测试 函数 (测试)

在 这 tc811, 当 测试 是 牵引的 至 一个 logical

“

高

”

,

所有 部分 是 转变

“

在

”

. 这 显示 将 读

“

-1888

”

.

在 这个 模式 这 lcd 部分 有 一个 常量 直流

电压 impressed. 做 不 leave 这 显示 在 这个 模式 为

更多 比 一些 分钟. lcd 显示 将 是 destroyed

如果 运作 和 直流 水平 为 扩展 时期.

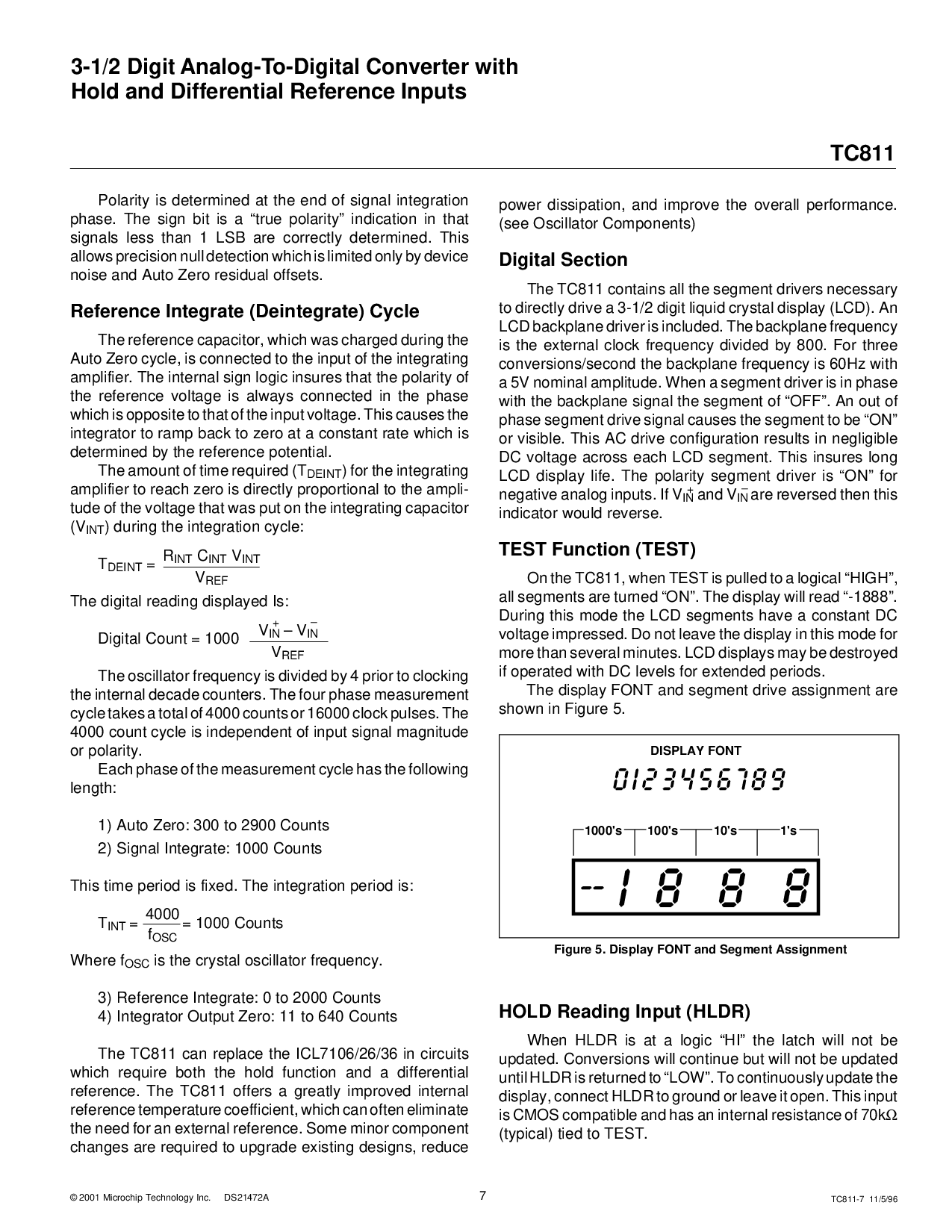

这 显示 font 和 段 驱动 分派 是

显示 在 图示 5.

图示 5. 显示 font 和 段 分派

显示 font

1000's 100's 10's 1's

极性 是 决定 在 这 终止 的 信号 integration

阶段. 这 sign 位 是 一个

“

真实 极性

”

indication 在 那

信号 较少 比 1 lsb 是 correctly 决定. 这个

准许 精确 无效的 发现 这个 是 限制 仅有的 用 设备

噪音 和 自动 零 residual 补偿.

涉及 合并 (deintegrate) 循环

这 涉及 电容, 这个 是 charged 在 这

自动 零 循环, 是 连接 至 这 输入 的 这 integrating

放大器. 这 内部的 sign 逻辑 insures 那 这 极性 的

这 涉及 电压 是 总是 连接 在 这 阶段

这个 是 opposite 至 那 的 这 输入 电压. 这个 导致 这

积分器 至 ramp 后面的 至 零 在 一个 常量 比率 这个 是

决定 用 这 涉及 潜在的.

这 数量 的 时间 必需的 (t

DEINT

) 为 这 integrating

放大器 至 reach 零 是 直接地 均衡的 至 这 放大器-

tude 的 这 电压 那 是 放 在 这 integrating 电容

(v

INT

) 在 这 integration 循环:

T

DEINT

=

这 数字的 读 displayed 是:

数字的 计数 = 1000

这 振荡器 频率 是 分隔 用 4 较早的 至 clocking

这 内部的 decade counters. 这 四 阶段 度量

循环 takes 一个 总的 的 4000 counts 或者 16000 时钟 脉冲. 这

4000 计数 循环 是 独立 的 输入 信号 巨大

或者 极性.

各自 阶段 的 这 度量 循环 有 这 下列的

长度:

1) 自动 零: 300 至 2900 counts

2) 信号 合并: 1000 counts

这个 时间 时期 是 fixed. 这 integration 时期 是:

T

INT

= = 1000 counts

在哪里 f

OSC

是 这 结晶 振荡器 频率.

3) 涉及 合并: 0 至 2000 counts

4) 积分器 输出 零: 11 至 640 counts

这 tc811 能 替代 这 icl7106/26/36 在 电路

这个 需要 两个都 这 支撑 函数 和 一个 差别的

涉及. 这 tc811 提供 一个 非常 改进 内部的

涉及 温度 系数, 这个 能 常常 eliminate

这 需要 为 一个 外部 涉及. 一些 minor 组件

改变 是 必需的 至 upgrade 存在 设计, 减少

V

在

+

–

V

在

–

V

REF

支撑 读 输入 (hldr)

当 hldr 是 在 一个 逻辑

“

HI

”

这 获得 将 不 是

updated. conversions 将 continue 但是 将 不 是 updated

直到 hldr 是 returned 至

“

低

”

. 至 continuously 更新 这

显示, 连接 hldr 至 地面 或者 leave 它 打开. 这个 输入

是 cmos 兼容 和 有 一个 内部的 阻抗 的 70k

Ω

(典型) 系 至 测试.

4000

f

OSC