tlv1504, tlv1508

2.7 v 至 5.5 v, 10-位, 200 ksps, 4/8 channel, 低 power,

串行 相似物-至-数字的 转换器 和 自动 电源 向下

slas251 – 12月 1999

3

邮递 办公室 盒 655303

•

达拉斯市, 德州 75265

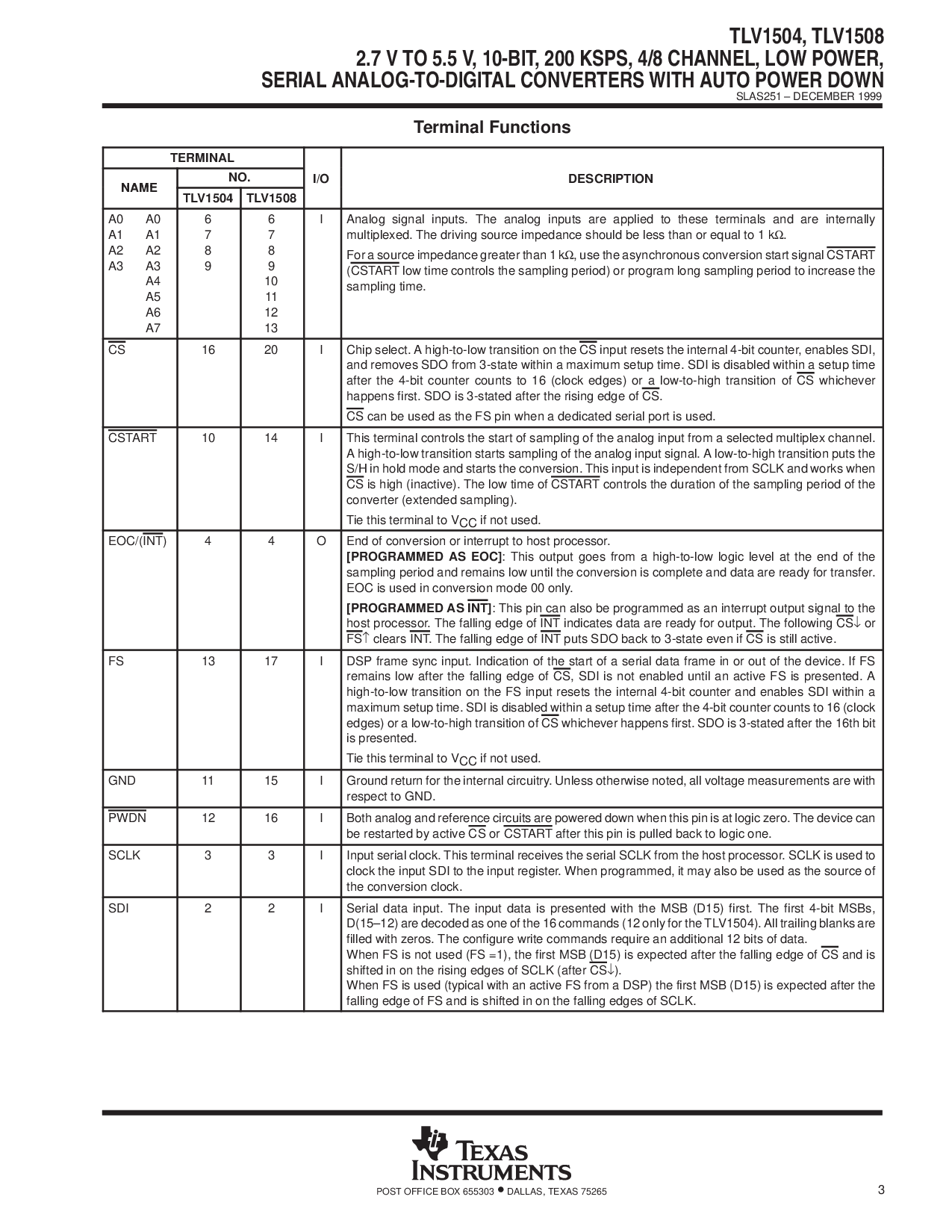

终端 功能

终端

名字

非.

i/o 描述

名字

TLV1504 TLV1508

A0 A0

A1 A1

A2 A2

A3 A3

A4

A5

A6

A7

6

7

8

9

6

7

8

9

10

11

12

13

I 相似物 信号 输入. 这 相似物 输入 是 应用 至 这些 terminals 和 是 内部

多路复用. 这 驱动 源 阻抗 应当 是 较少 比 或者 equal 至 1 k

Ω

.

为 一个 源 阻抗 更好 比 1 k

Ω

, 使用 这 异步的 转换 开始 信号 cstart

(cstart低 时间 控制 这 抽样 时期) 或者 程序 长 抽样 时期 至 增加 这

抽样 时间.

CS 16 20 I 碎片 选择. 一个 高-至-低 转变 在 这 cs输入 resets 这 内部的 4-位 计数器, 使能 sdi,

和 removes sdo 从 3-状态 在里面 一个 最大 建制 时间. sdi 是 无能 在里面 一个 建制 时间

之后 这 4-位 计数器 counts 至 16 (时钟 edges) 或者 一个 低-至-高 转变 的 cs

whichever

发生 第一. sdo 是 3-陈述 之后 这 rising 边缘 的 cs

.

CS

能 是 使用 作 这 fs 管脚 当 一个 专心致志的 串行 端口 是 使用.

CSTART 10 14 I 这个 终端 控制 这 开始 的 抽样 的 这 相似物 输入 从 一个 选择 multiplex 频道.

一个 高-至-低 转变 开始 抽样 的 这 相似物 输入 信号. 一个 低-至-高 转变 puts 这

s/h 在 支撑 模式 和 开始 这 转换. 这个 输入 是 独立 从 sclk 和 工作 当

CS

是 高 (inactive). 这 低 时间 的 cstart控制 这 持续时间 的 这 抽样 时期 的 这

转换器 (扩展 抽样).

系 这个 终端 至 v

CC

如果 不 使用.

eoc/(int) 4 4 O 终止 的 转换 或者 中断 至 host 处理器.

[programmed 作 eoc]

: 这个 输出 变得 从 一个 高-至-低 逻辑 水平的 在 这 终止 的 这

抽样 时期 和 仍然是 低 直到 这 转换 是 完全 和 数据 是 准备好 为 转移.

eoc 是 使用 在 转换 模式 00 仅有的.

[programmed 作 int

]

: 这个 管脚 能 也 是 编写程序 作 一个 中断 输出 信号 至 这

host 处理器. 这 下落 边缘 的 int

indicates 数据 是 准备好 为 输出. 这 下列的 cs

↓

或者

FS

↑

clears int. 这 下落 边缘 的 intputs sdo 后面的 至 3-状态 甚至 如果 cs是 安静的 起作用的.

FS 13 17 I dsp 框架 同步 输入. indication 的 这 开始 的 一个 串行 数据 框架 在 或者 输出 的 这 设备. 如果 fs

仍然是 低 之后 这 下落 边缘 的 cs

, sdi 是 不 使能 直到 一个 起作用的 fs 是 提交. 一个

高-至-低 转变 在 这 fs 输入 resets 这 内部的 4-位 计数器 和 使能 sdi 在里面 一个

最大 建制 时间. sdi 是 无能 在里面 一个 建制 时间 之后 这 4-位 计数器 counts 至 16 (时钟

edges) 或者 一个 低-至-高 转变 的 cs

whichever 发生 第一. sdo 是 3-陈述 之后 这 16th 位

是 提交.

系 这个 终端 至 v

CC

如果 不 使用.

地 11 15 I 地面 返回 为 这 内部的 电路系统. 除非 否则 指出, 所有 电压 度量 是 和

遵守 至 地.

PWDN 12 16 I 两个都 相似物 和 涉及 电路 是 powered 向下 当 这个 管脚 是 在 逻辑 零. 这 设备 能

是 restarted 用 起作用的 cs

或者 cstart之后 这个 管脚 是 牵引的 后面的 至 逻辑 一个.

SCLK 3 3 I 输入 串行 时钟. 这个 终端 receives 这 串行 sclk 从 这 host 处理器. sclk 是 使用 至

时钟 这 输入 sdi 至 这 输入 寄存器. 当 编写程序, 它 将 也 是 使用 作 这 源 的

这 转换 时钟.

SDI 2 2 I 串行 数据 输入. 这 输入 数据 是 提交 和 这 msb (d15) 第一. 这 第一 4-位 msbs,

d(15–12) 是 解码 作 一个 的 这 16 commands (12 仅有的 为 这 tlv1504). 所有 trailing blanks 是

filled 和 zeros. 这 配置 写 commands 需要 一个 额外的 12 位 的 数据.

当 fs 是 不 使用 (fs =1), 这 第一 msb (d15) 是 预期的 之后 这 下落 边缘 的 cs

和 是

shifted 在 在 这 rising edges 的 sclk (之后 cs

↓

).

当 fs 是 使用 (典型 和 一个 起作用的 fs 从 一个 dsp) 这 第一 msb (d15) 是 预期的 之后 这

下落 边缘 的 fs 和 是 shifted 在 在 这 下落 edges 的 sclk.