rev. d–12–

ad7476/ad7477/ad7478

输入 频率 – hz

–50

10k

thd – db

–55

–60

–65

–70

–75

100k 1M

–80

–85

–90

V

DD

= 2.35v

V

DD

= 2.7v

V

DD

= 5.25v

V

DD

= 4.75v

V

DD

= 3.6v

图示 9. thd vs. 相似物 输入 频率, f

S

= 993 ksps

输入 频率 – hz

–72

10k

thd – db

–74

–76

–78

–80

100k 1M

–82

–84

V

DD

= 2.35v

V

DD

= 2.7v

V

DD

= 5.25v

V

DD

= 4.75v

V

DD

= 3.6v

图示 10. thd vs. 相似物 输入 频率, f

S

= 605 ksps

数字的 输入

这 数字的 输入 应用 至 这 ad7476/ad7477/ad7478 是

不 限制 用 这 最大 比率 那 限制 这 相似物 输入.

instead, 这 数字的 输入 应用 能 go 至 7 v 和 是 不

restricted 用 这 v

DD

+ 0.3 v 限制 作 在 这 相似物 输入. 为

例子, 如果 这 ad7476/ad7477/ad7478 是 运作 和 一个

V

DD

的 3 v, 然后 5 v 逻辑 水平 可以 是 使用 在 这 数字的

输入. 不管怎样, 它 是 重要的 至 便条 那 这 数据输出 在

sdata 将 安静的 有 3 v 逻辑 水平 当 v

DD

=3v. 另一

有利因素 的 sclk 和

CS

不 正在 restricted 用 这 v

DD

+

0.3 v 限制 是 这 事实 那 电源 供应 sequencingissues 是

避免. 如果

CS

或者 sclk 是 应用 在之前 v

DD

, 那里 是 非 风险 的

获得-向上 作 那里 将 是 在 这 相似物 输入 如果 一个信号更好

比 0.3 v 是 应用 较早的 至 v

DD

.

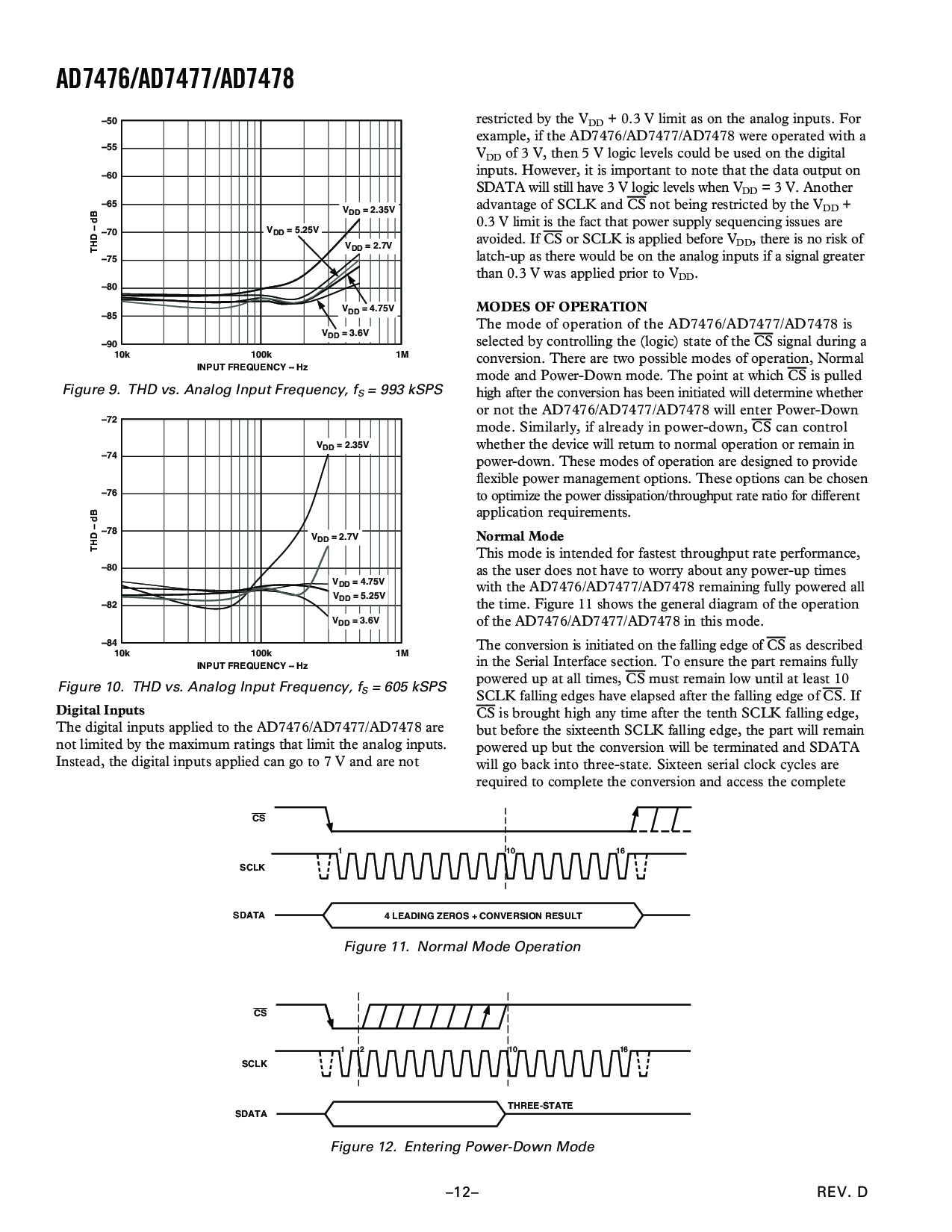

模式 的 运作

这 模式 的 运作 的 这 ad7476/ad7477/ad7478 是

选择 用 controlling 这 (逻辑) 状态 的 这

CS

信号 在 一个

转换. 那里 是 二 可能 模式 的 运作, 正常的

模式 和 电源-向下 模式. 这 要点 在 这个

CS

是 牵引的

高 之后 这 转换 有 被 initiated 将 决定 whether

或者 不 这 ad7476/ad7477/ad7478 将 enter 电源-向下

模式. similarly, 如果 already 在 电源-向下,

CS

能 控制

whether 这设备 将 返回 至 正常的 运作 或者 仍然是 在

电源-向下. 这些 模式 的 运作 是 设计 至 提供

有伸缩性的 电源 管理 选项. 这些 选项 能 是 选择

至 优化 这 电源 消耗/throughput 比率 比率 为 different

应用 (所需的)东西.

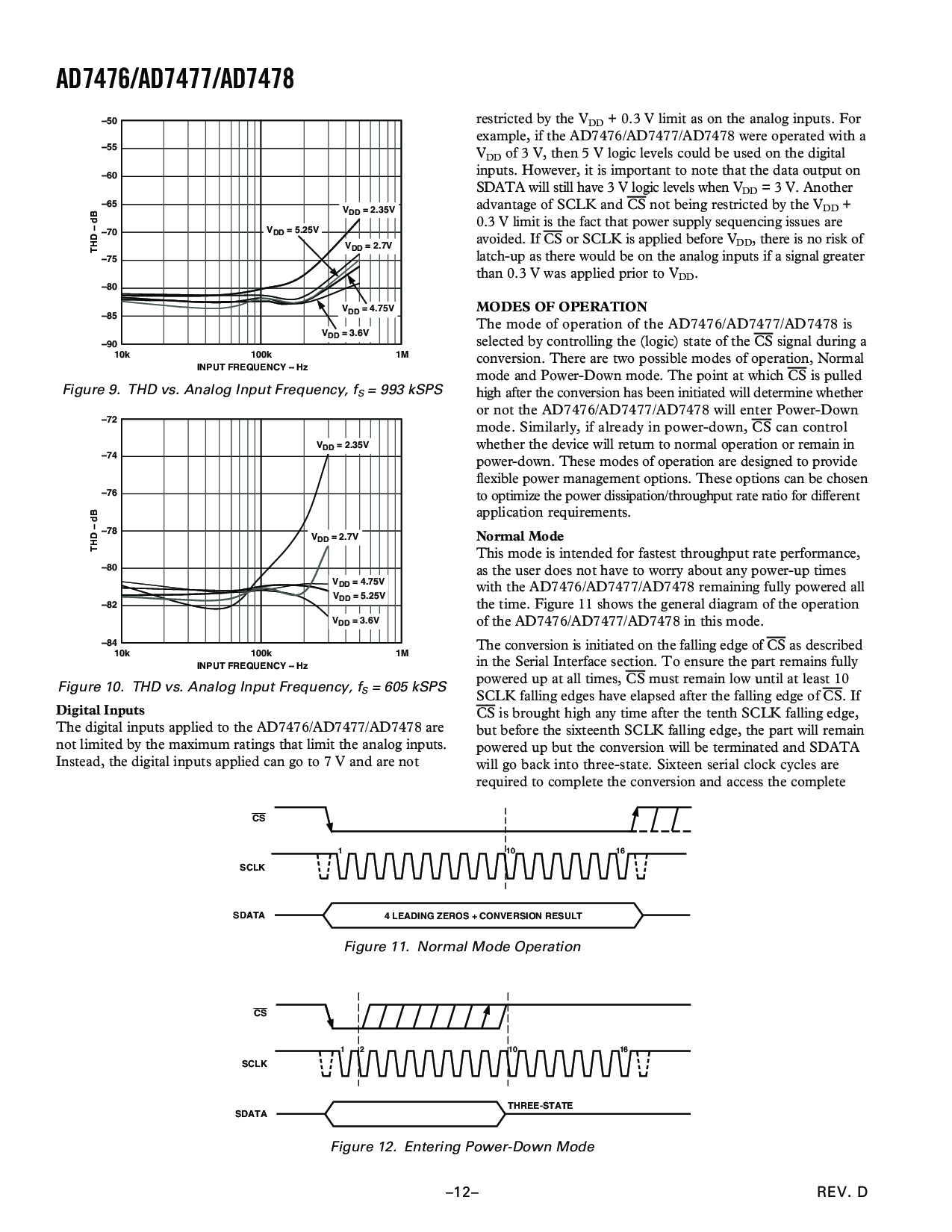

正常的 模式

这个 模式 是 将 为 fastest throughput 比率 效能,

作 这 用户 做 不 有 至 worry 关于 任何 电源-向上 时间

和 这 ad7476/ad7477/ad7478 remaining 全部地 powered 所有

这 时间. 图示 11 显示 这 一般 图解 的 这 运作

的 这 ad7476/ad7477/ad7478 在 这个 模式.

这 转换 是 initiated 在 这 下落 边缘 的

CS

作 描述

在 这 串行 接口 部分. 至 确保 这 部分 仍然是 全部地

powered 向上 在 所有 时间,

CS

必须 仍然是 低 直到 在 least 10

sclk 下落 edges 有 消逝 之后 这 下落 边缘 的

CS

. 如果

CS

是 brought 高 任何 时间 之后 这 tenth sclk 下落 边缘,

但是 在之前 这 sixteenth sclk 下落 边缘, 这 部分 将 仍然是

powered 向上 但是 这 转换 将 是 terminated 和 sdata

将 go 后面的 在 三-状态. 十六 串行 时钟 循环 是

required 至 完全 这 转换 和 进入 这 完全

4 leading zeros + 转换 结果

CS

SCLK

SDATA

1

10

16

图示 11. 正常的 模式 运作

1

10

16

2

三-状态

CS

SCLK

SDATA

图示 12. 进去 电源-向下 模式