1999 Oct 05 7

飞利浦 半导体 初步的 规格

2.7 ghz i

2

c-总线 控制 低 阶段

噪音 频率 synthesizer

TSA5059

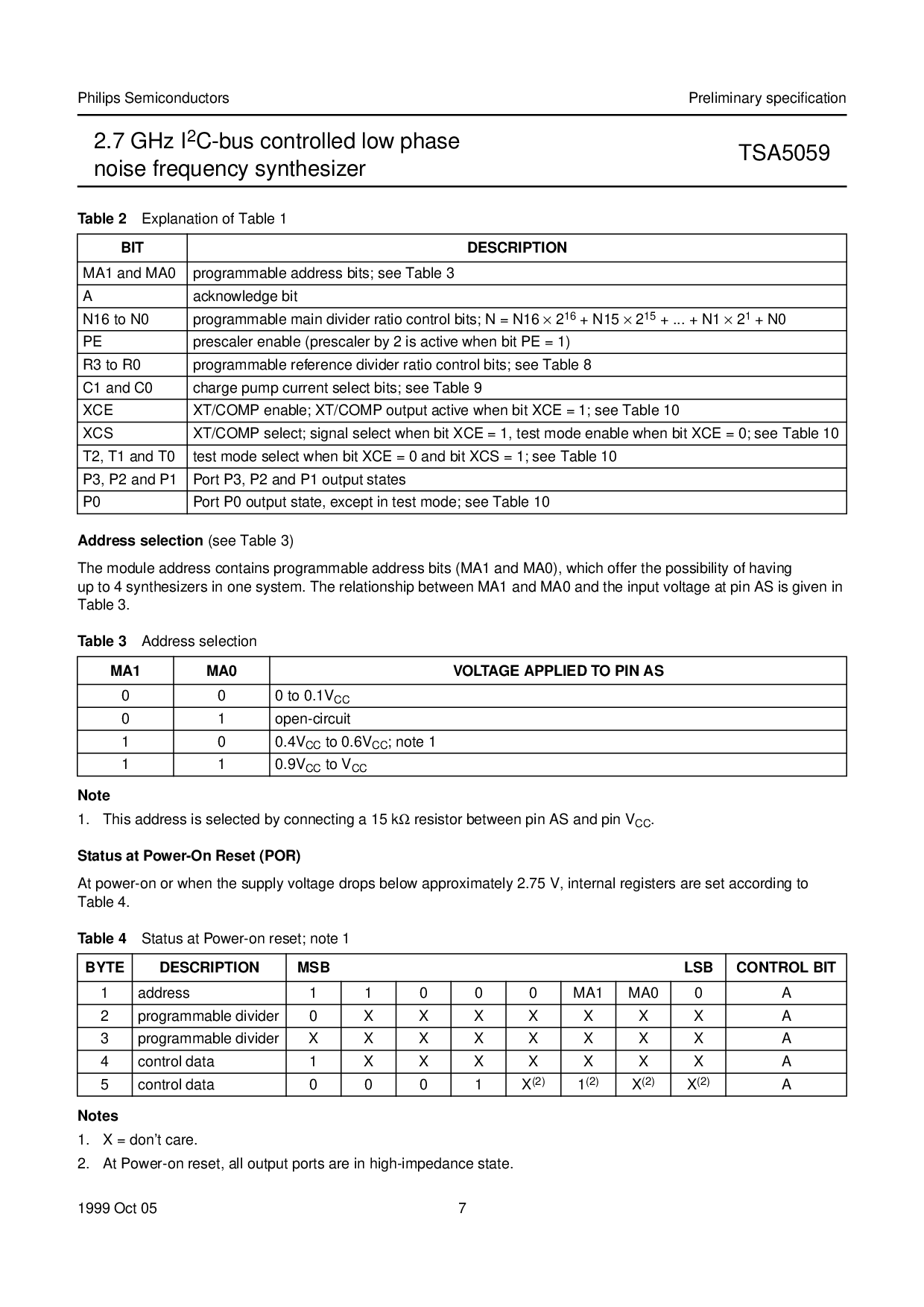

表格 2

explanation 的 表格 1

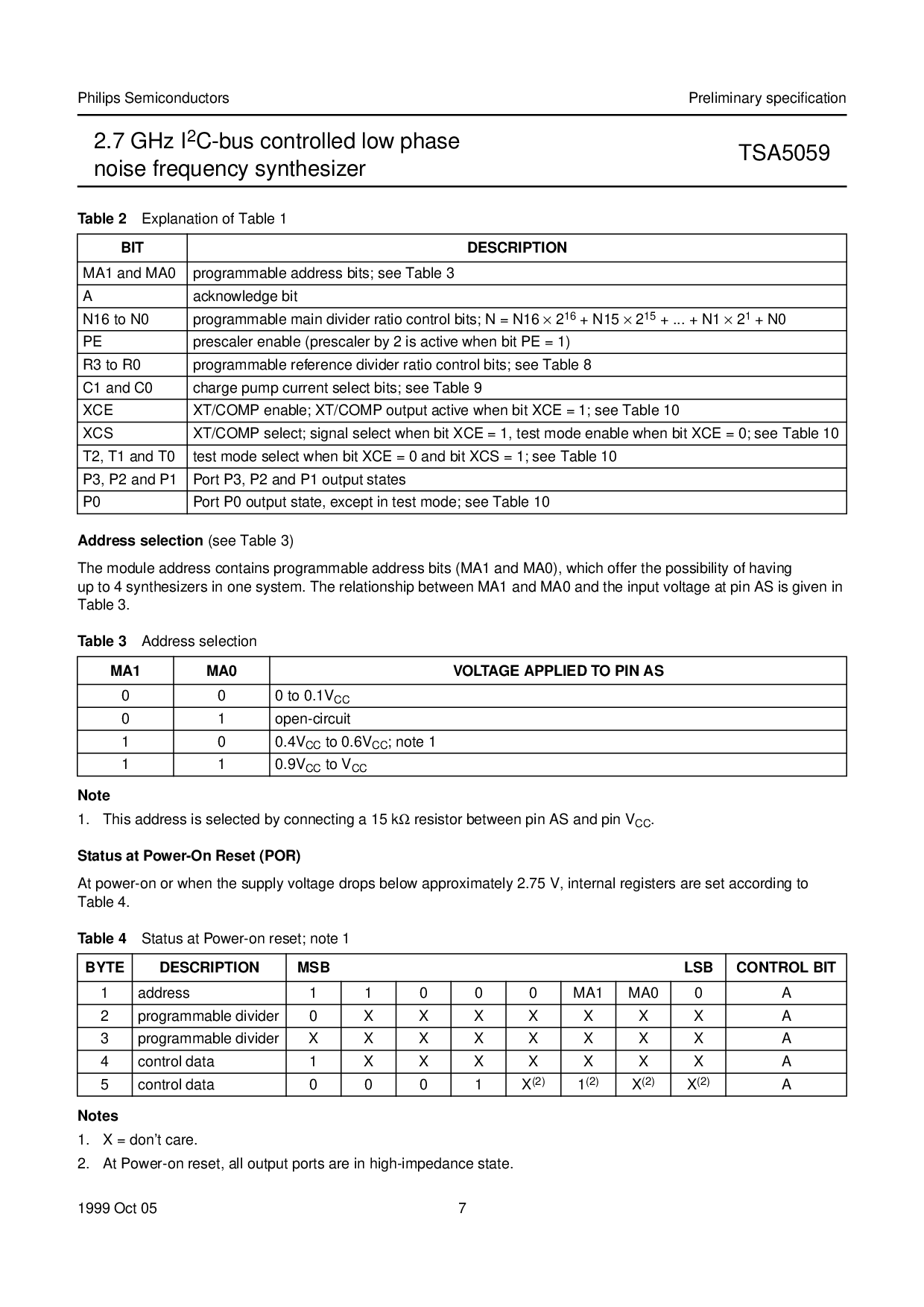

地址 选择

(看 表格 3)

这 单元 地址 包含 可编程序的 地址 位 (ma1 和 ma0), 这个 提供 这 possibility 的 having

向上 至 4 synthesizers 在 一个 系统. 这 relationship 在 MA1 和 MA0 和 这 输入 电压 在 管脚 作 是 给 在

表格 3.

表格 3

地址 选择

便条

1. 这个 地址 是 选择 用 连接 一个 15 k

Ω

电阻 在 管脚 作 和 管脚 V

CC

.

状态 在 电源-在 重置 (por)

在 电源-在 或者 当 这 供应 电压 drops 在下 大概 2.75 v, 内部的 寄存器 是 设置 符合 至

表格 4.

表格 4

状态 在 电源-在 重置; 便条 1

注释

1. X = don’t 小心.

2. 在 电源-在 重置, 所有 输出 端口 是 在 高-阻抗 状态.

位 描述

MA1 和 MA0 可编程序的 地址 位; 看 表格 3

一个 acknowledge 位

N16 至 N0 可编程序的 主要的 分隔物 比率 控制 位; n = N16

×

2

16

+ N15

×

2

15

+ ... + N1

×

2

1

+N0

PE 预分频器 使能 (预分频器 用 2 是 起作用的 当 位 PE = 1)

R3 至 R0 可编程序的 涉及 分隔物 比率 控制 位; 看 表格 8

C1 和 C0 承担 打气 电流 选择 位; 看 表格 9

XCE xt/竞赛 使能; xt/竞赛 输出 起作用的 当 位 XCE = 1; 看 表格 10

XCS xt/竞赛 选择; 信号 选择 当 位 XCE = 1, 测试 模式 使能 当 位 XCE = 0; 看 表格 10

t2, t1 和 T0 测试 模式 选择 当 位 XCE = 0 和 位 XCS = 1; 看 表格 10

p3, p2 和 P1 端口 p3, p2 和 p1 输出 states

P0 端口 p0 输出 状态, 除了 在 测试 模式; 看 表格 10

MA1 MA0 电压 应用 至 管脚 作

0 0 0 至 0.1v

CC

0 1 打开-电路

1 0 0.4v

CC

至 0.6v

CC

; 便条 1

1 1 0.9v

CC

至 V

CC

字节 描述 MSB LSB 控制 位

1 地址 11000MA1MA00 一个

2 可编程序的 分隔物 0 XXXXXXX 一个

3 可编程序的 分隔物 XXXXXXXX 一个

4 控制 数据 1 XXXXXXX 一个

5 控制 数据 0001X

(2)

1

(2)

X

(2)

X

(2)

一个