2000 Oct 24 6

飞利浦 半导体 产品 规格

1.3 ghz i

2

c-总线 控制 低 阶段

噪音 频率 synthesizer

TSA5060A

这 tsa5060a 是 控制 通过 这 二-线 i

2

c-总线.

为 程序编制, 那里 是 一个 7-位 单元 地址 和

位 r/w 为 selecting 读 或者 写 模式.

至 是 能 至 有 更多 比 一个 synthesizer 在 一个

I

2

c-总线 系统, 一个 的 四 可能 地址 是 选择

取决于 在 这 电压 应用 在 管脚 作 (看 表格 3).

这 TSA5060A fulfils 这 快 模式 I

2

c-总线, 符合 至

这 飞利浦 i

2

c-总线 规格. 这 i

2

c-总线 接口 是

设计 在 此类 一个 方法 那 管脚 scl 和 sda 能 是

连接 也 至 5 或者 3.3 v 牵引的-向上 i

2

c-总线 线条,

准许 这 pll synthesizer 至 是 连接 直接地 至

这 总线 线条 的 一个 3.3 v 微控制器.

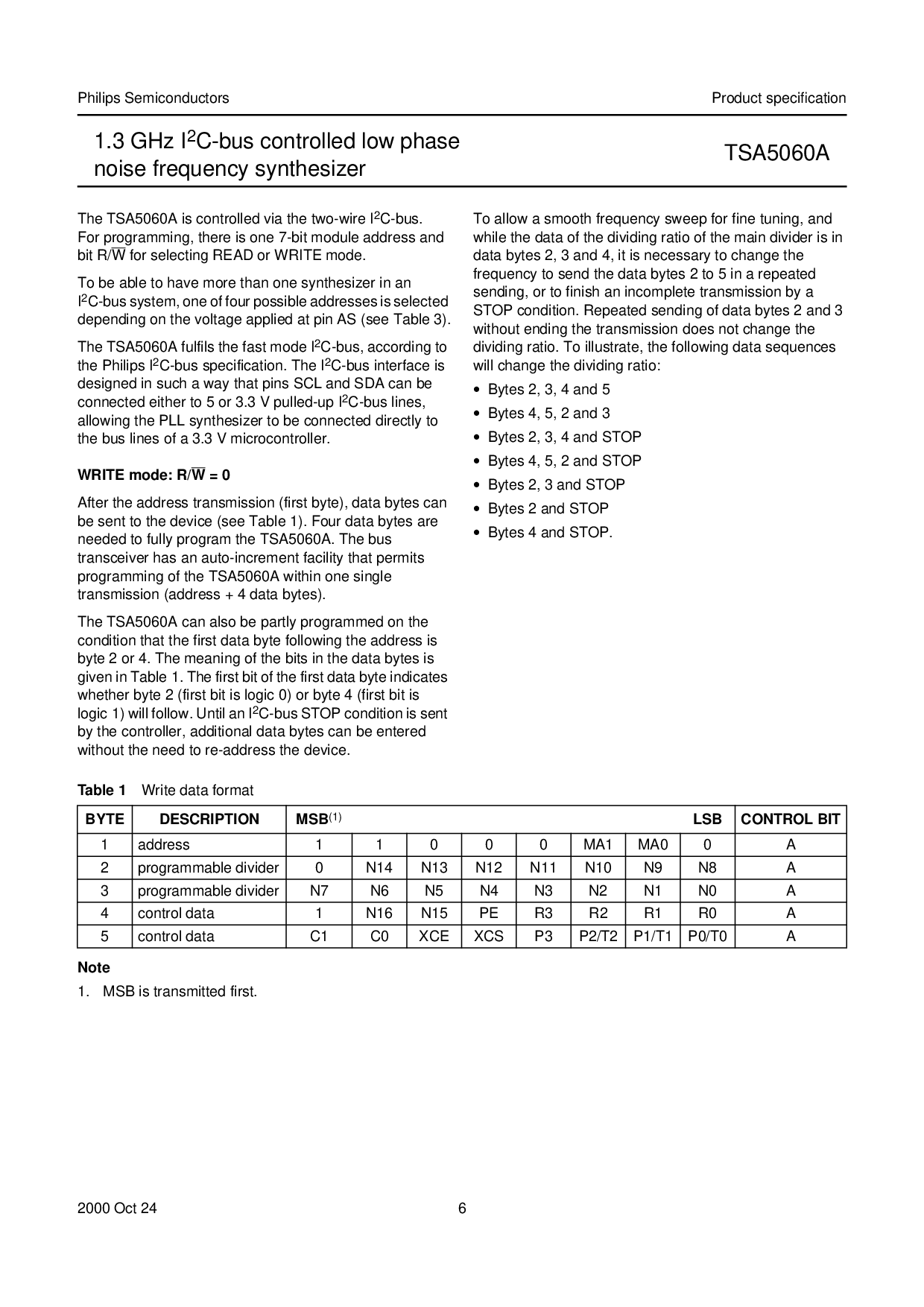

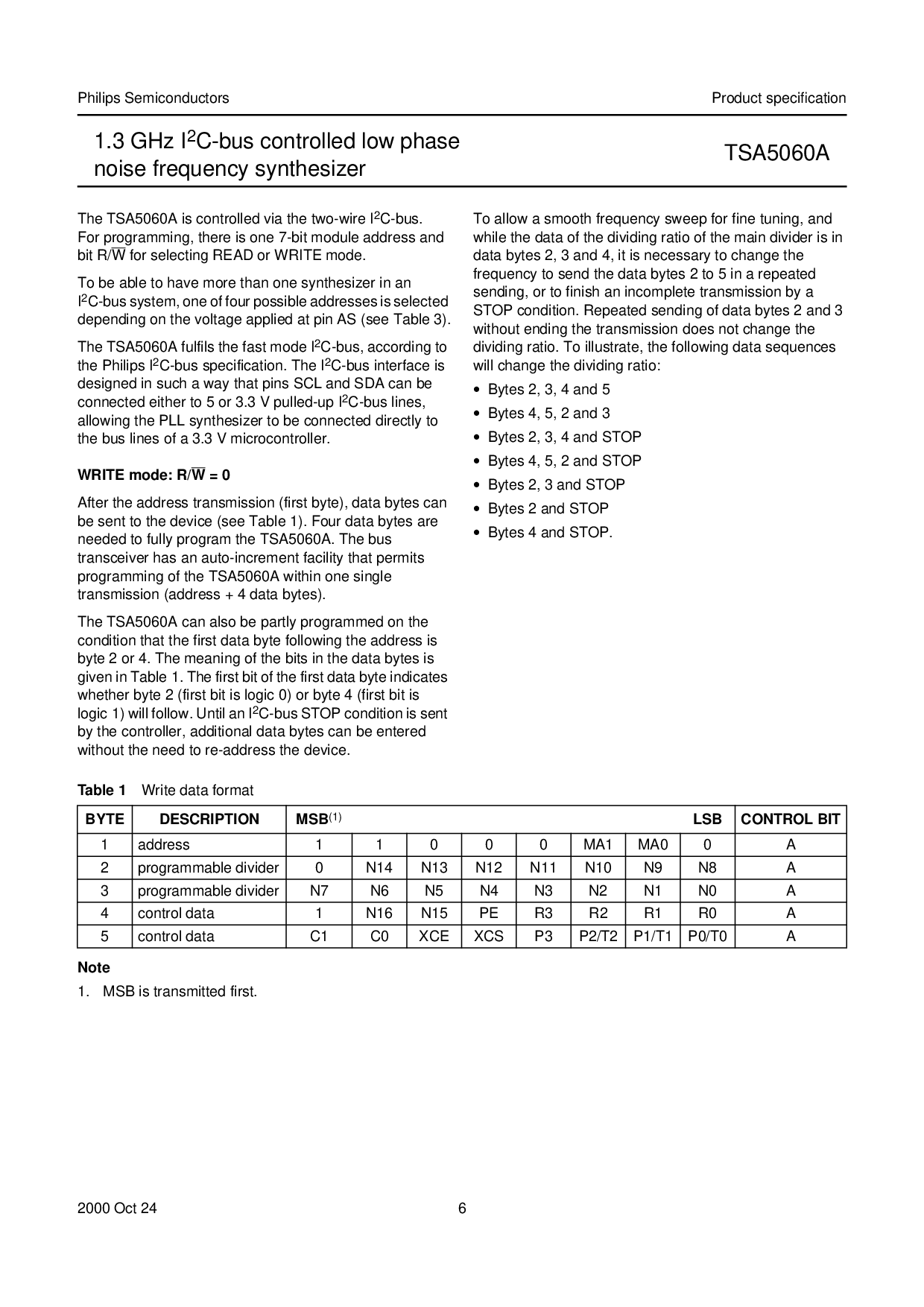

写 模式: r/W=0

之后 这 地址 传递 (第一 字节), 数据 字节 能

是 sent 至 这 设备 (看 表格 1). 四 数据 字节 是

需要 至 全部地 程序 这 tsa5060a. 这 总线

transceiver 有 一个 自动-increment facility 那 准许

程序编制 的 这 tsa5060a 在里面 一个 单独的

传递 (地址 + 4 数据 字节).

这 tsa5060a 能 也 是 partly 编写程序 在 这

情况 那 这 第一 数据 字节 下列的 这 地址 是

字节 2 或者 4. 这 meaning 的 这 位 在 这 数据 字节 是

给 在 表格 1. 这 第一 位 的 这 第一 数据 字节 indicates

whether 字节 2 (第一 位 是 逻辑 0) 或者 字节 4 (第一 位 是

逻辑 1) 将 follow. 直到 一个 I

2

c-总线 停止 情况 是 sent

用 这 控制, 额外的 数据 字节 能 是 entered

没有 这 需要 至 re-地址 这 设备.

至 准许 一个 平整的 频率 sweep 为 fine tuning, 和

当 这 数据 的 这 dividing 比率 的 这 主要的 分隔物 是 在

数据 字节 2, 3 和 4, 它 是 需要 至 改变 这

频率 至 send 这 数据 字节 2 至 5 在 一个 重复的

sending, 或者 至 完成 一个 incomplete 传递 用 一个

停止 情况. 重复的 sending 的 数据 字节 2 和 3

没有 ending 这 传递 做 不 改变 这

dividing 比率. 至 illustrate, 这 下列的 数据 sequences

将 改变 这 dividing 比率:

•

字节 2, 3, 4 和 5

•

字节 4, 5, 2 和 3

•

字节 2, 3, 4 和 停止

•

字节 4, 5, 2 和 停止

•

字节 2, 3 和 停止

•

字节 2 和 停止

•

字节 4 和 停止.

表格 1

写 数据 format

便条

1. msb 是 transmitted 第一.

字节 描述 MSB

(1)

LSB 控制 位

1 地址 1 1 0 0 0 MA1 MA0 0 一个

2 可编程序的 分隔物 0 N14 N13 N12 N11 N10 N9 N8 一个

3 可编程序的 分隔物 N7 N6 N5 N4 N3 N2 N1 N0 一个

4 控制 数据 1 N16 N15 PE R3 R2 R1 R0 一个

5 控制 数据 C1 C0 XCE XCS P3 p2/t2 p1/t1 p0/t0 一个