idt54/74fct88915tt 55/70/100/133

低 skew pll-为基础 cmos 时钟 驱动器 军队 和 商业的 温度 范围

9.7 6

注释:

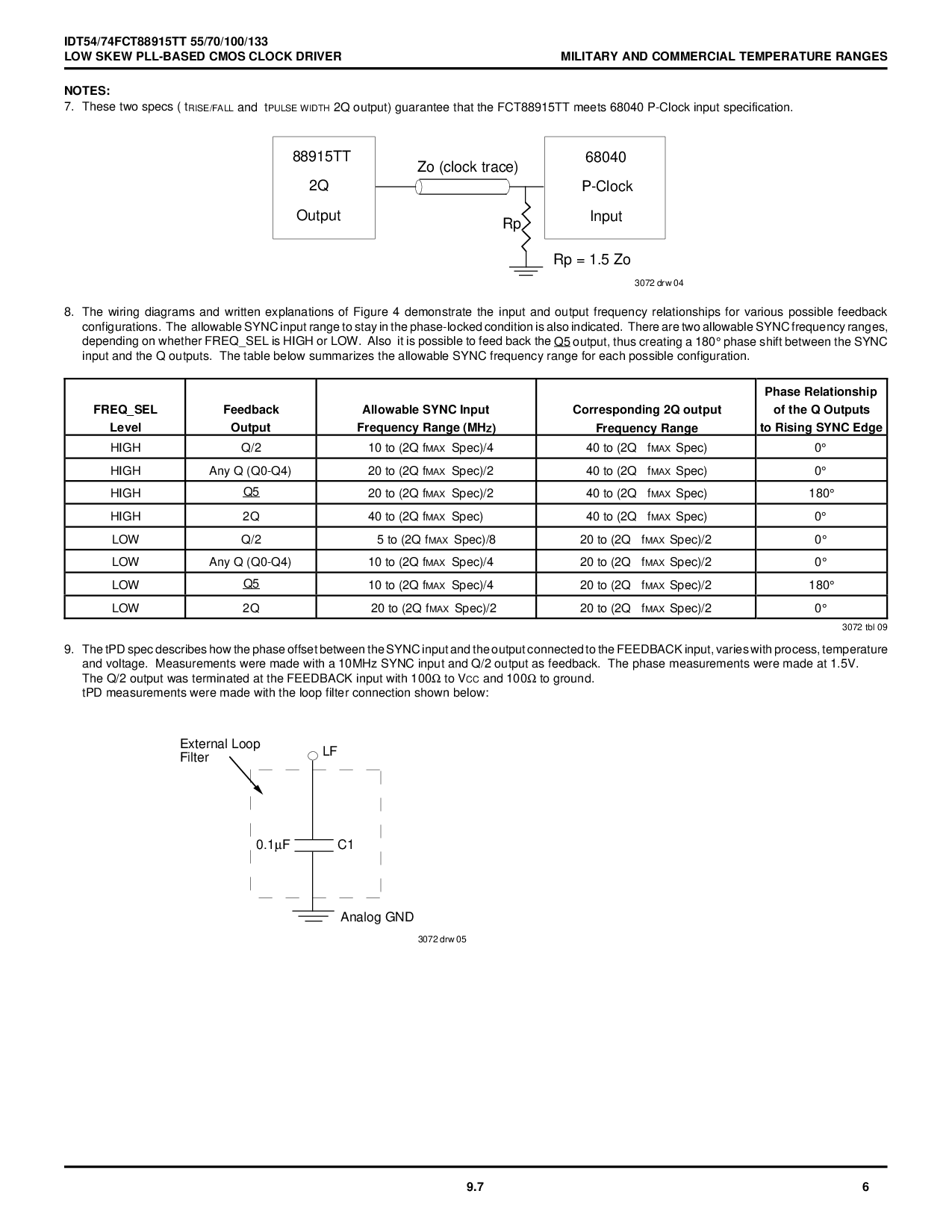

7. 这些 二 规格 ( t

上升/下降

和 t

脉冲波 宽度

2q 输出) 保证 那 这 fct88915tt 满足 68040 p-时钟 输入 规格.

8. 这 线路 图解 和 写 explanations 的 图示 4 demonstrate 这 输入 和 输出 频率 relationships 为 各种各样的 可能 反馈

配置. 这 容许的 同步 输入 范围 至 停留 在 这 阶段-锁 情况 是 也 表明. 那里 是 二 容许的 同步 频率 范围,

取决于 在 whether freq_sel 是 高 或者 低. 也 它 是 可能 至 喂养 后面的 这

q5 输出, 因此 creating 一个 180

°

阶段 变换 在 这 同步

输入 和 这 q 输出. 这 表格 在下 summarizes 这 容许的 同步 频率 范围 为 各自 可能 配置.

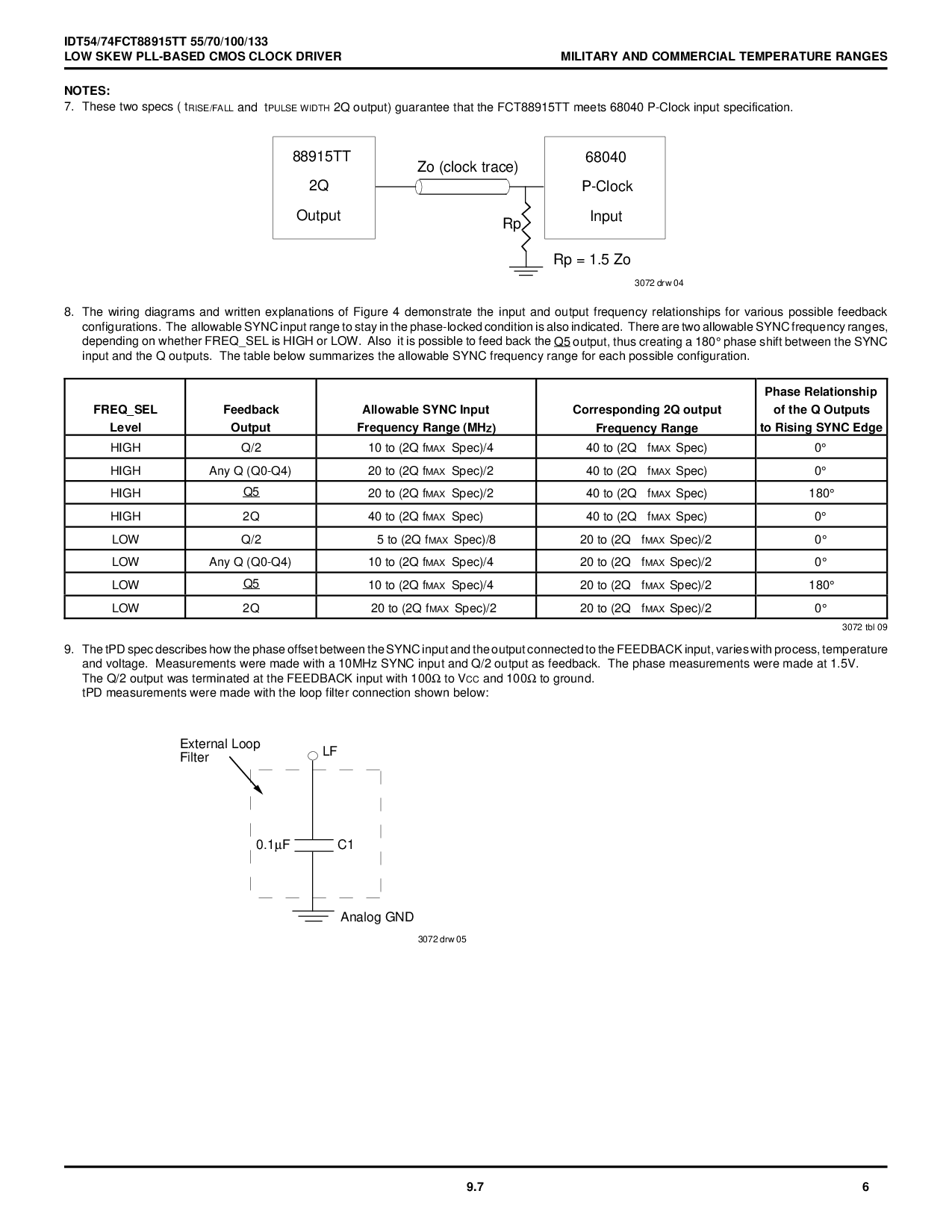

9. 这 tpd 规格 describes 如何 这 阶段 补偿 在 这 同步 输入 和 这 输出 连接 至 这 反馈 输入, varies 和 处理, 温度

和 电压. 度量 是 制造 和 一个 10mhz 同步 输入 和 q/2 输出 作 反馈. 这 阶段 度量 是 制造 在 1.5v.

这 q/2 输出 是 terminated 在 这 反馈 输入 和 100

Ω

至 v

CC

和 100

Ω

至 地面.

tpd 度量 是 制造 和 这 循环 过滤 连接 显示 在下:

LF

外部 循环

过滤

0.1

µ

FC1

相似物 地

3072 tbl 09

3072 drw 05

3072 drw 04

68040

p-时钟

输入

88915TT

2Q

输出

Rp

zo (时钟 查出)

rp = 1.5 zo

freq_sel

水平的

反馈

输出

容许的 同步 输入

频率 范围 (mh

Z

)

相应的 2q 输出

频率 范围

阶段 relationship

的 这 q 输出

至 rising 同步 边缘

高 q/2 10 至 (2q f

最大值

规格)/4 40 至 (2q f

最大值

规格) 0

°

高 任何 q (q0-q4) 20 至 (2q f

最大值

规格)/2 40 至 (2q f

最大值

规格) 0

°

高

Q5

20 至 (2q f

最大值

规格)/2 40 至 (2q f

最大值

规格) 180

°

高 2Q 40 至 (2q f

最大值

规格) 40 至 (2q f

最大值

规格) 0

°

低 q/2 5 至 (2q f

最大值

规格)/8 20 至 (2q f

最大值

规格)/2 0

°

低 任何 q (q0-q4) 10 至 (2q f

最大值

规格)/4 20 至 (2q f

最大值

规格)/2 0

°

低

Q5

10 至 (2q f

最大值

规格)/4 20 至 (2q f

最大值

规格)/2 180

°

低 2Q 20 至 (2q f

最大值

规格)/2 20 至 (2q f

最大值

规格)/2 0

°