4

ucc1580-1,-2,-3,-4

ucc2580-1,-2,-3,-4

ucc3580-1,-2,-3,-4

电的 特性

除非 否则 陈述, 所有 规格 是 在 这 全部 温度 范围, VDD

= 12v, r1 = 18.2k, r2 = 4.41k, c

T

= 100pf, r3 = 100k, c

OUT1

= 0, c

OUT2

= 0. t

一个

= 0°c 至 70°c 为 这 ucc3580,

−

40°c 至 85°c

为 这 ucc2580,

−

55°c 至 125°c 为 这 ucc1580, t

一个

=T

J

.

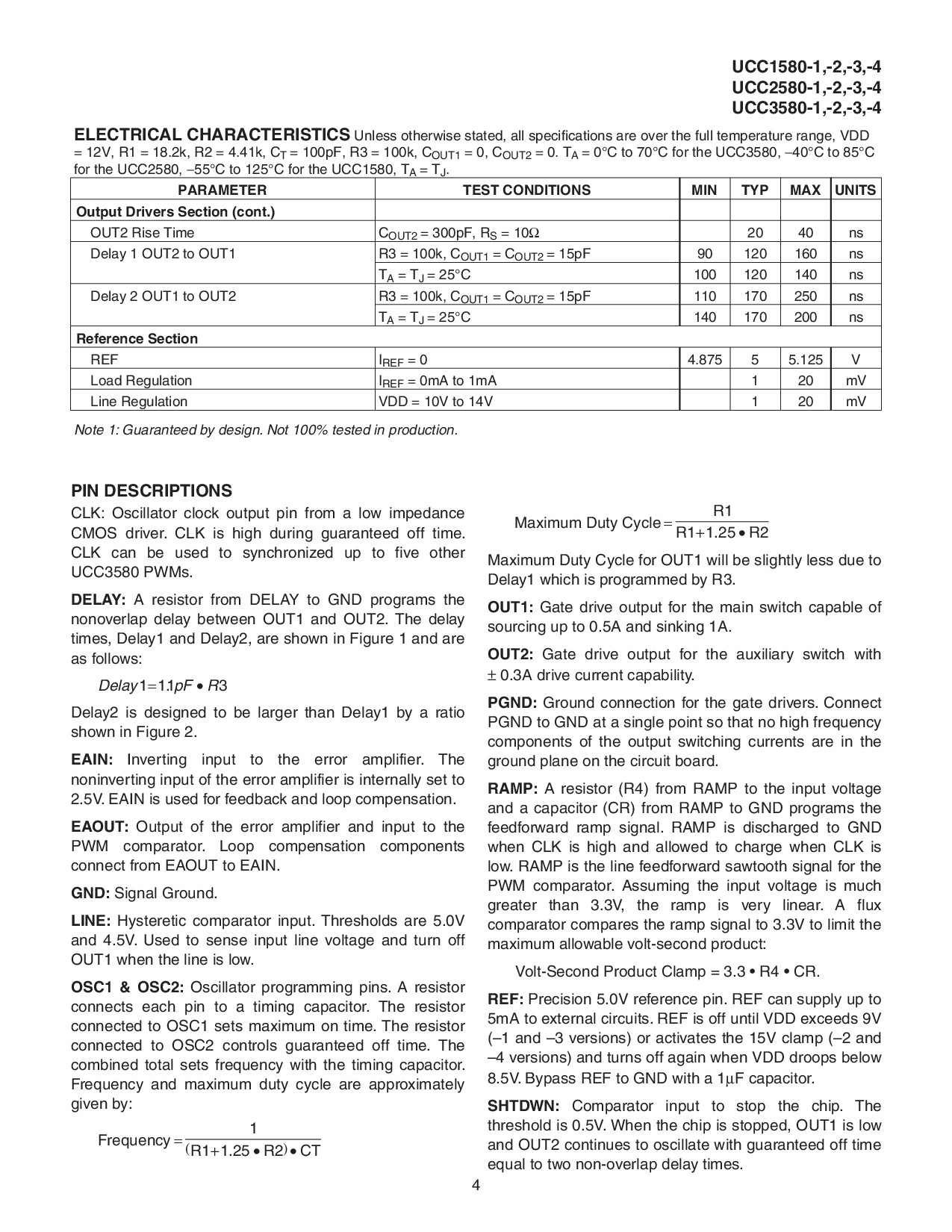

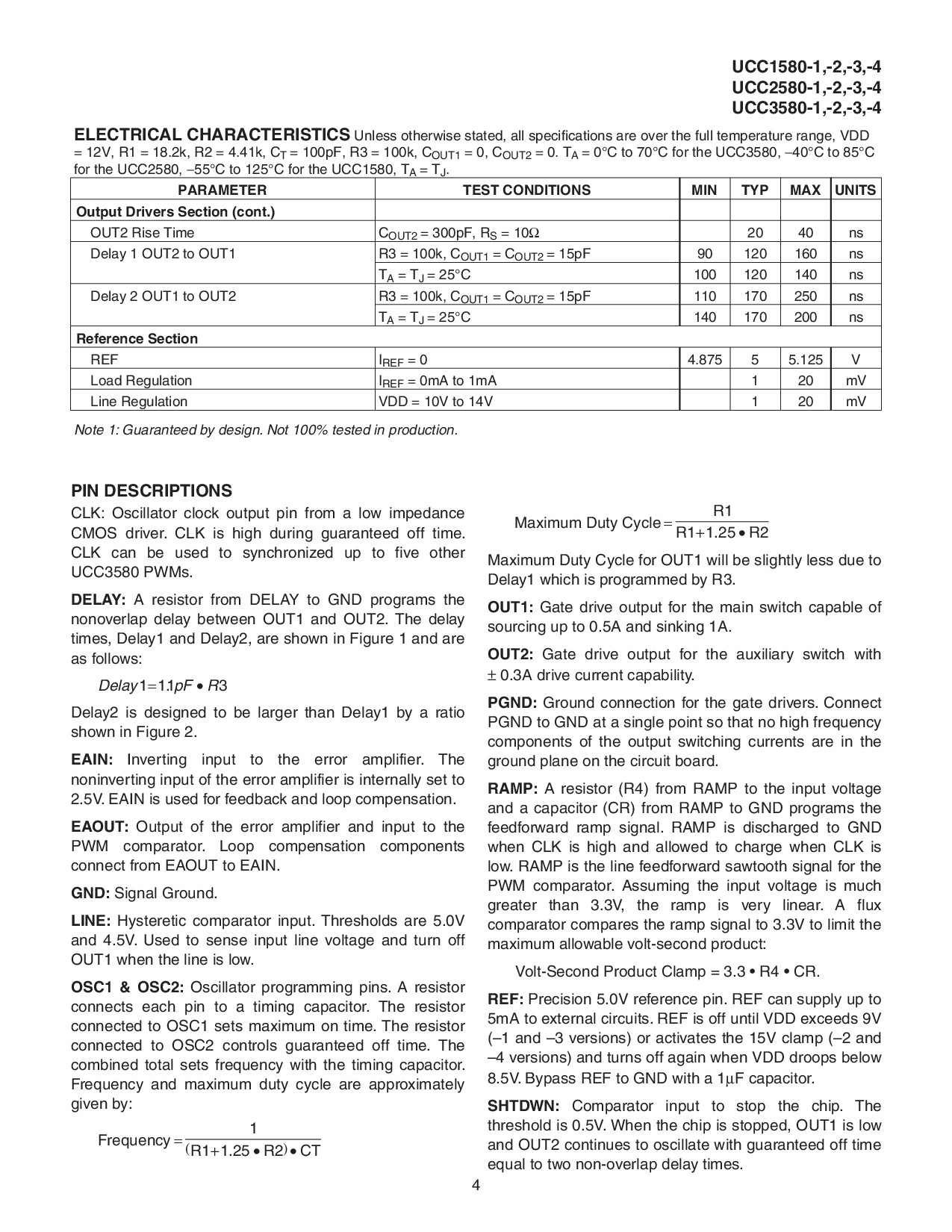

参数 测试 情况 最小值 典型值 最大值 单位

输出 驱动器 部分 (内容.)

out2 上升 时间 C

OUT2

= 300pf, r

S

= 10

Ω

20 40 ns

延迟 1 out2 至 out1 r3 = 100k, c

OUT1

= c

OUT2

= 15pf 90 120 160 ns

T

一个

=T

J

= 25°c 100 120 140 ns

延迟 2 out1 至 out2 r3 = 100k, c

OUT1

= c

OUT2

= 15pf 110 170 250 ns

T

一个

=T

J

= 25°c 140 170 200 ns

涉及 部分

REF I

REF

= 0 4.875 5 5.125 V

加载 规章制度 I

REF

= 0ma 至 1ma 1 20 mV

线条 规章制度 VDD = 10v 至 14v 1 20 mV

便条 1: 有保证的 用 设计. 不 100% 测试 在 生产.

clk: 振荡器 时钟 输出 管脚 从 一个 低 阻抗

CMOS 驱动器. CLK 是 高 在 有保证的 止 时间.

CLK 能 是 使用 至 同步 向上 至 five 其它

UCC3580 pwms.

延迟:

一个 电阻 从 延迟 至 地 programs 这

nonoverlap 延迟 在 OUT1 和 out2. 这 延迟

时间, Delay1 和 delay2, 是 显示 在 图示 1 和 是

作 跟随:

延迟 pF R

111 3

=•

.

Delay2 是 设计 至 是 大 比 Delay1 用 一个 比率

显示 在 图示 2.

eain:

反相的 输入 至 这 错误 放大器. 这

同相 输入 的 这 错误 放大器 是 内部 设置 至

2.5v. EAIN 是 使用 为 反馈 和 循环 补偿.

eaout:

输出 的 这 错误 放大器 和 输入 至 这

PWM 比较器. 循环 补偿 组件

连接 从 EAOUT 至 eain.

地:

信号 地面.

线条:

Hysteretic 比较器 输入. 门槛 是 5.0v

和 4.5v. 使用 至 sense 输入 线条 电压 和 转变 止

out1 当 这 线条 是 低.

OSC1 &放大; osc2:

振荡器 程序编制 管脚. 一个 电阻

connects 各自 管脚 至 一个 定时 电容. 这 电阻

连接 至 OSC1 sets 最大 在 时间. 这 电阻

连接 至 OSC2 控制 有保证的 止 时间. 这

联合的 总的 sets 频率 和 这 定时 电容.

频率 和 最大 职责 循环 是 大概

给 用:

()

频率

1

R1 1.25 R2 CT

=

+••

最大 职责 循环

R1

R1 1.25 R2

=

+•

最大 职责 循环 为 OUT1 将 是 slightly 较少 预定的 至

delay1 这个 是 编写程序 用 r3.

out1:

门 驱动 输出 为 这 主要的 转变 有能力 的

sourcing 向上 至 0.5a 和 sinking 1a.

out2:

门 驱动 输出 为 这 auxiliary 转变 和

±

0.3a 驱动 电流 能力.

pgnd:

地面 连接 为 这 门 驱动器. 连接

PGND 至 地 在 一个 单独的 要点 所以 那 非 高 频率

组件 的 这 输出 切换 电流 是 在 这

地面 平面 在 这 电路 板.

ramp:

一个 电阻 (r4) 从 RAMP 至 这 输入 电压

和 一个 电容 (cr) 从 RAMP 至 地 programs 这

feedforward ramp 信号. RAMP 是 释放 至 地

当 CLK 是 高 和 允许 至 承担 当 CLK 是

低. RAMP 是 这 线条 feedforward sawtooth 信号 为 这

PWM 比较器. 假设 这 输入 电压 是 更

更好 比 3.3v, 这 ramp 是 非常 直线的. 一个 通量

比较器 比较 这 ramp 信号 至 3.3v 至 限制 这

最大 容许的 volt-第二 产品:

volt-第二 产品 clamp = 3.3 • r4 • cr.

ref:

精确 5.0v 涉及 管脚. REF 能 供应 向上 至

5mA 至 外部 电路. REF 是 止 直到 VDD 超过 9V

(–1 和 –3 版本) 或者 activates 这 15V clamp (–2 和

–4 版本) 和 转变 止 又一次 当 VDD droops 在下

8.5v. 绕过 ref 至 地 和 一个 1

µ

f 电容.

shtdwn:

比较器 输入 至 停止 这 碎片. 这

门槛 是 0.5v. 当 这 碎片 是 stopped, OUT1 是 低

和 OUT2 持续 至 oscillate 和 有保证的 止 时间

equal 至 二 非-overlap 延迟 时间.

管脚 描述