2000 二月 07 8

飞利浦 半导体 初步的 规格

低 电源 音频的 dac UDA1334BTS

8.4 过滤 stream dac

这 fsdac 是 一个 semi-数字的 reconstruction 过滤 那

converts 这 1-位 数据 stream 的 这 噪音 shaper 至 一个

相似物 输出 电压. 这 过滤 coefficients 是

执行 作 电流 来源 和 是 summed 在

模拟的 地面 的 这 输出 运算的 放大器. 在 这个

方法 非常 高 信号-至-噪音 效能 和 低 时钟

jitter 敏锐的 是 达到. 非 邮递-过滤 是 需要 预定的 至

这 固有的 过滤 函数 的 这 dac. 在-板 放大器

转变 这 fsdac 输出 电流 至 一个 输出 电压

信号 有能力 的 驱动 一个 线条 输出.

这 输出 电压 的 这 fsdac scales 按比例地

和 这 电源 供应 电压.

8.5 电源-在 重置

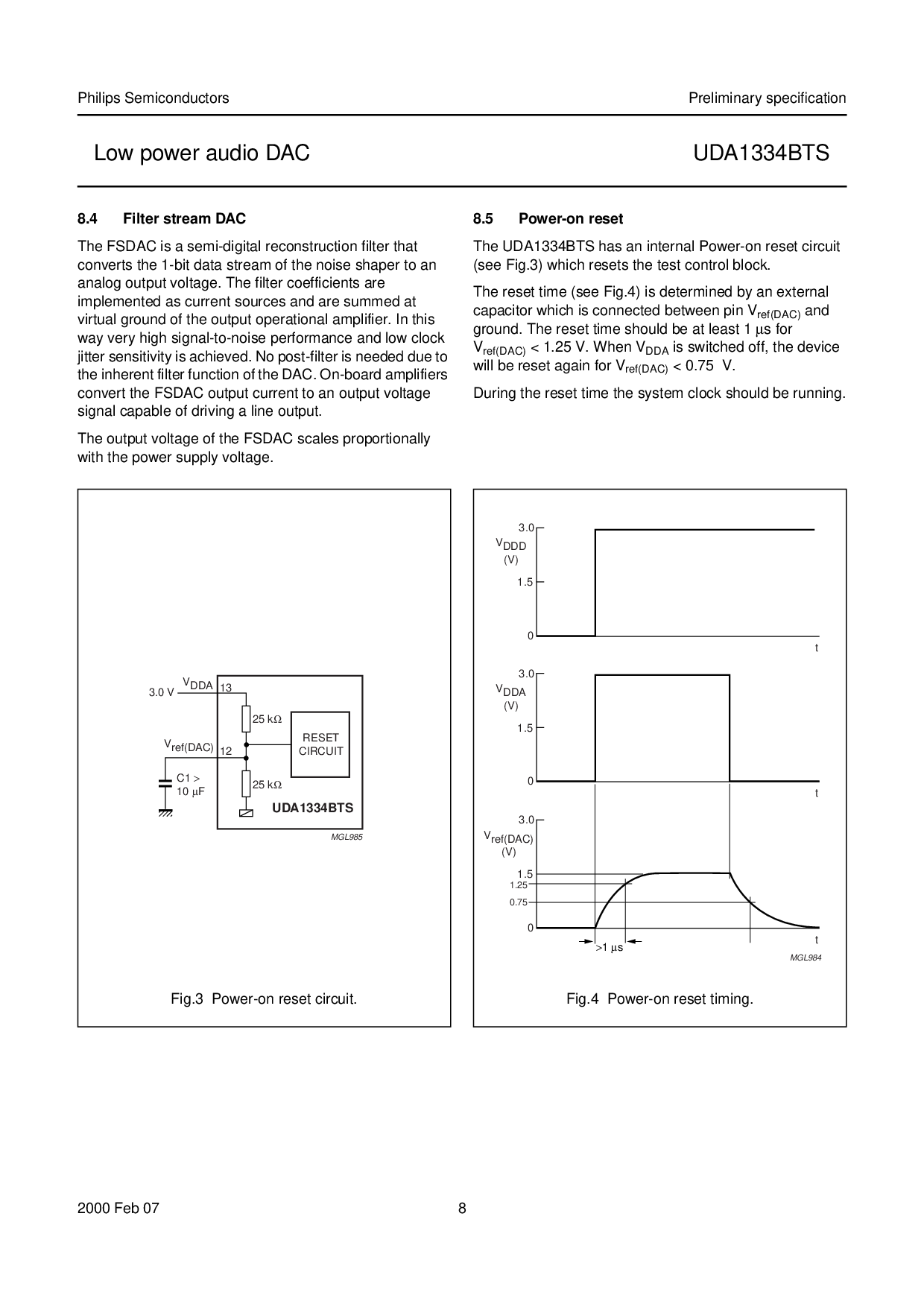

这 uda1334bts 有 一个 内部的 电源-在 重置 电路

(看 图.3) 这个 resets 这 测试 控制 块.

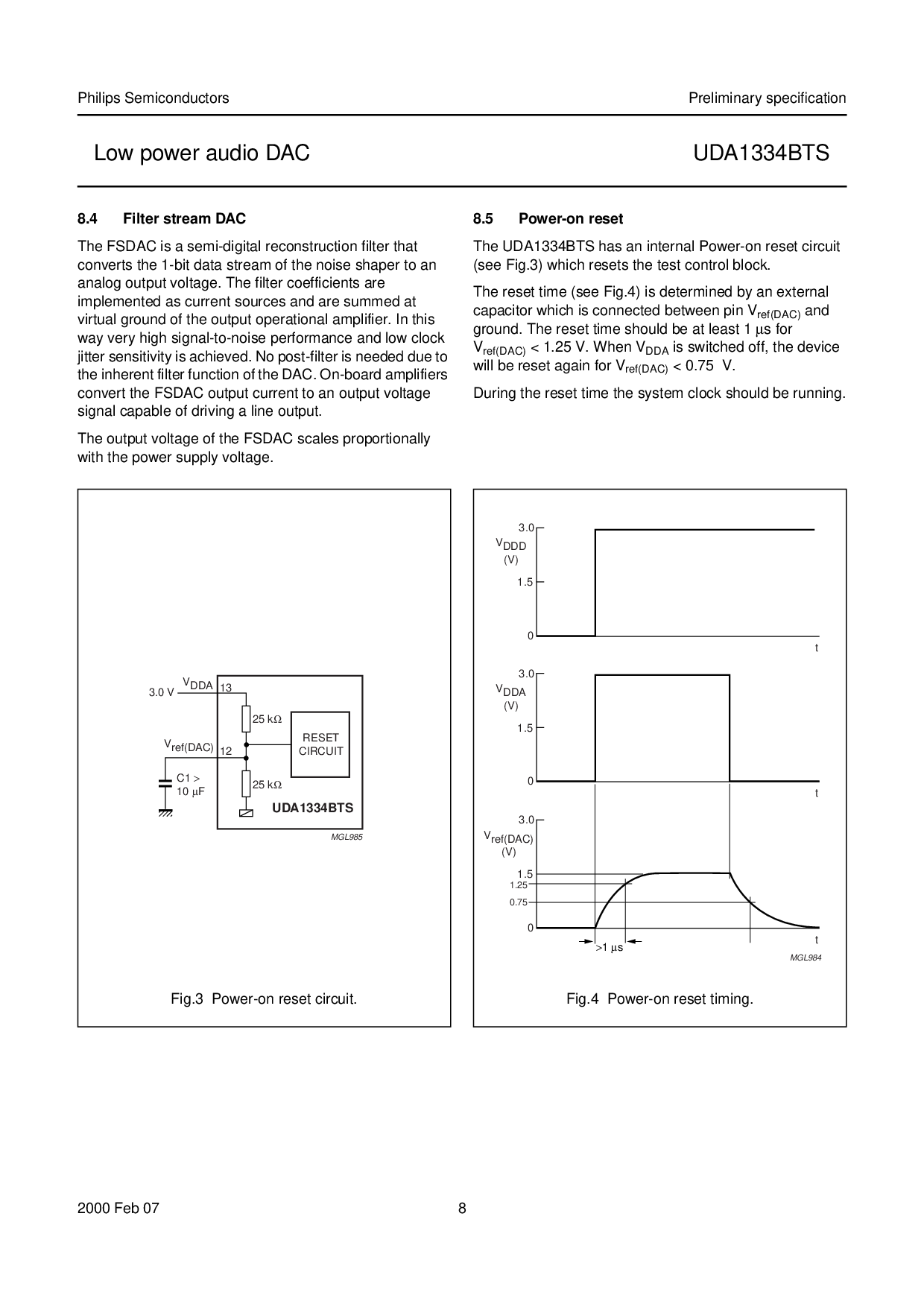

这 重置 时间 (看 图.4) 是 决定 用 一个 外部

电容 这个 是 连接 在 管脚 V

ref(dac)

和

地面. 这 重置 时间 应当 是 在 least 1

µ

s 为

V

ref(dac)

< 1.25 v. 当 v

DDA

是 切换 止, 这 设备

将 是 重置 又一次 为 v

ref(dac)

< 0.75 v.

在 这 重置 时间 这 系统 时钟 应当 是 运动.

handbook, halfpage

V

DDA

V

ref(dac)

3.0 v

13

12

MGL985

UDA1334BTS

C1

>

10

µ

F

重置

电路

25 k

Ω

25 k

Ω

图.3 电源-在 重置 电路.

handbook, halfpage

3.0

V

DDD

(v)

1.5

0

t

3.0

V

DDA

(v)

1.5

0

t

3.0

V

ref(dac)

(v)

1.5

1.25

0.75

0

t

MGL984

>

1

µ

s

图.4 电源-在 重置 定时.