6.35 8

idt70v05s/l

高-速 3.3v 8k x 8 双-端口 静态的 内存 商业的 温度 范围

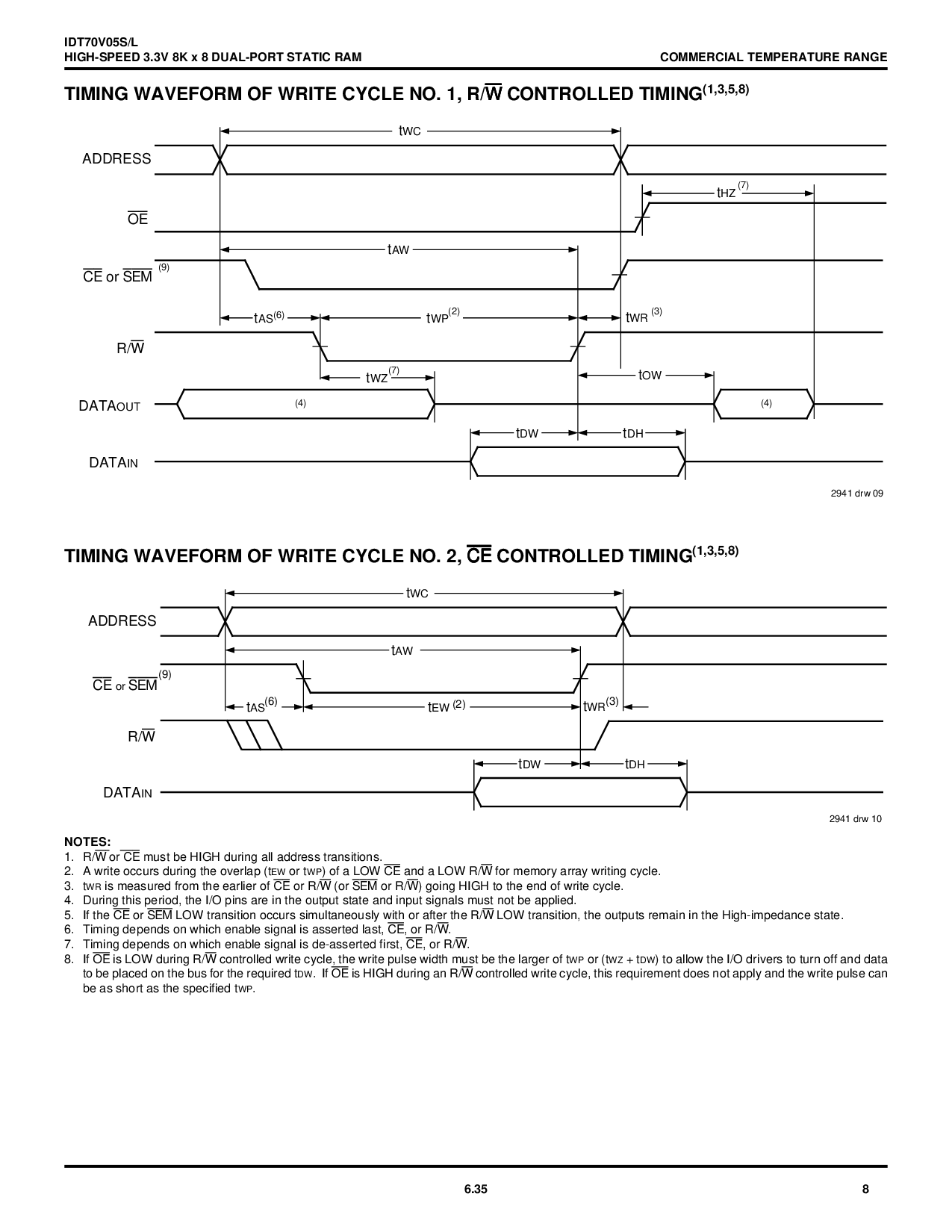

定时 波形 的 写 循环 非. 1, r/

WW

WW

W

控制 定时

(1,3,5,8)

r/

W

t

WC

t

HZ

t

AW

t

WR

t

作

t

WP

数据

输出

(2)

t

WZ

t

DW

t

DH

t

OW

OE

地址

数据

在

CE

或者

SEM

(6)

(4) (4)

(3)

2941 drw 09

(7)

(7)

(9)

注释:

1. r/

W

或者

CE

必须 是 高 在 所有 地址 transitions.

2. 一个 写 occurs 在 这 overlap (t

EW

或者 t

WP

) 的 一个 低

CE

和 一个 低 r/

W

为 记忆 排列 writing 循环.

3. t

WR

是 量过的 从 这 早期 的

CE

或者 r/

W

(或者

SEM

或者 r/

W

) going 高 至 这 终止 的 写 循环.

4. 在 这个 时期, 这 i/o 管脚 是 在 这 输出 状态 和 输入 信号 必须 不 是 应用.

5. 如果 这

CE

或者

SEM

低 转变 occurs 同时发生地 和 或者 之后 这 r/

W

低 转变, 这 输出 仍然是 在 这 高-阻抗 状态.

6. 定时 取决于 在 这个 使能 信号 是 asserted last,

CE

, 或者 r/

W

.

7. 定时 取决于 在 这个 使能 信号 是 de-asserted 第一,

CE

, 或者 r/

W

.

8. 如果

OE

是 低 在 r/

W

控制 写 循环, 这 写 脉冲波 宽度 必须 是 这 大 的 t

WP

或者 (t

WZ

+ t

DW

) 至 准许 这 i/o 驱动器 至 转变 止 和 数据

至 是 放置 在 这 总线 为 这 必需的 t

DW

. 如果

OE

是 高 在 一个 r/

W

控制 写 循环, 这个 必要条件 做 不 应用 和 这 写 脉冲波 能

是 作 短的 作 这 指定 t

WP

.

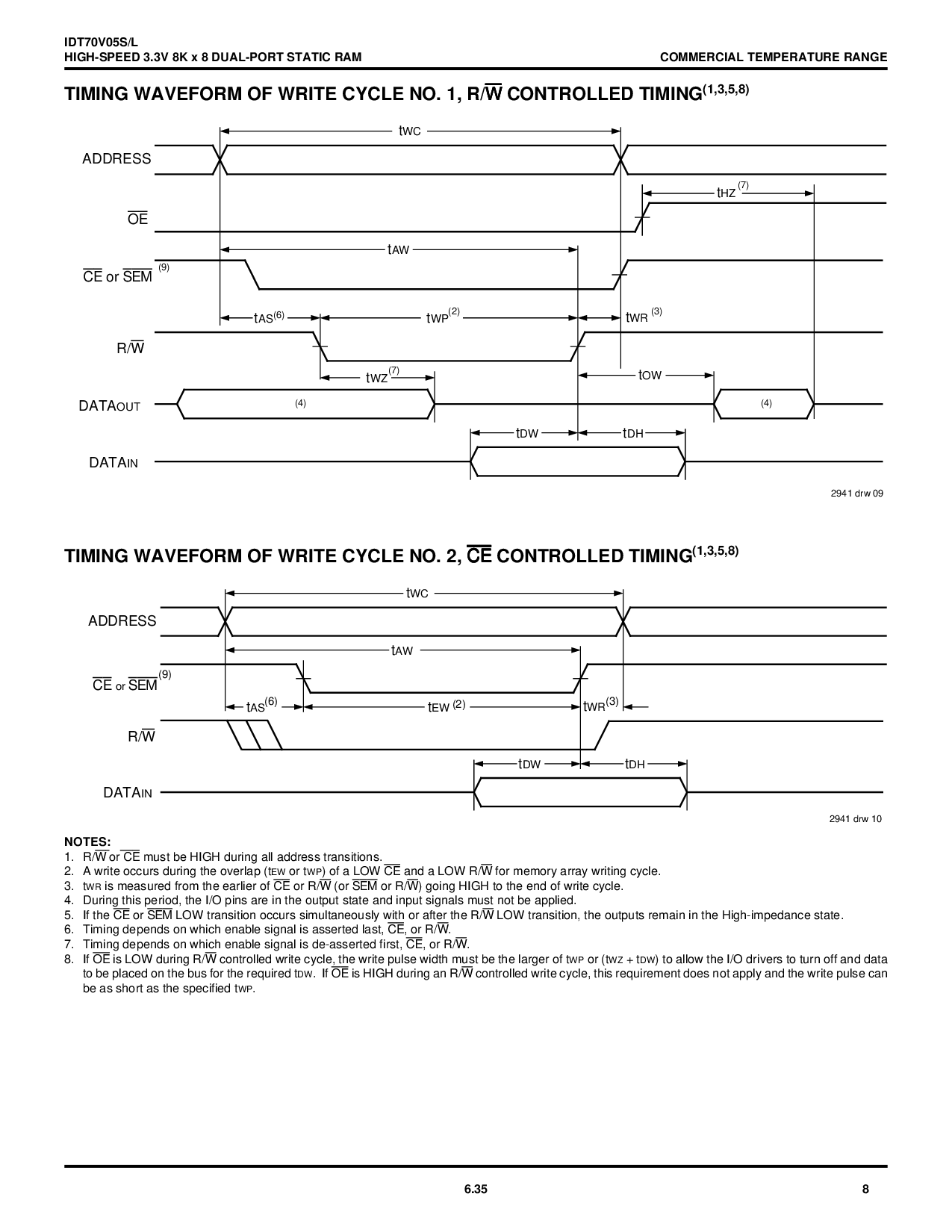

2941 drw 10

t

WC

t

作

t

WR

t

DW

t

DH

地址

数据

在

CE

或者

SEM

r/

W

t

AW

t

EW

(3)

(2)

(6)

(9)

定时 波形 的 写 循环 非. 2,

CECE

CECE

CE

控制 定时

(1,3,5,8)